S12 Clock, Reset and Power Management Unit (S12CPMU)

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 397

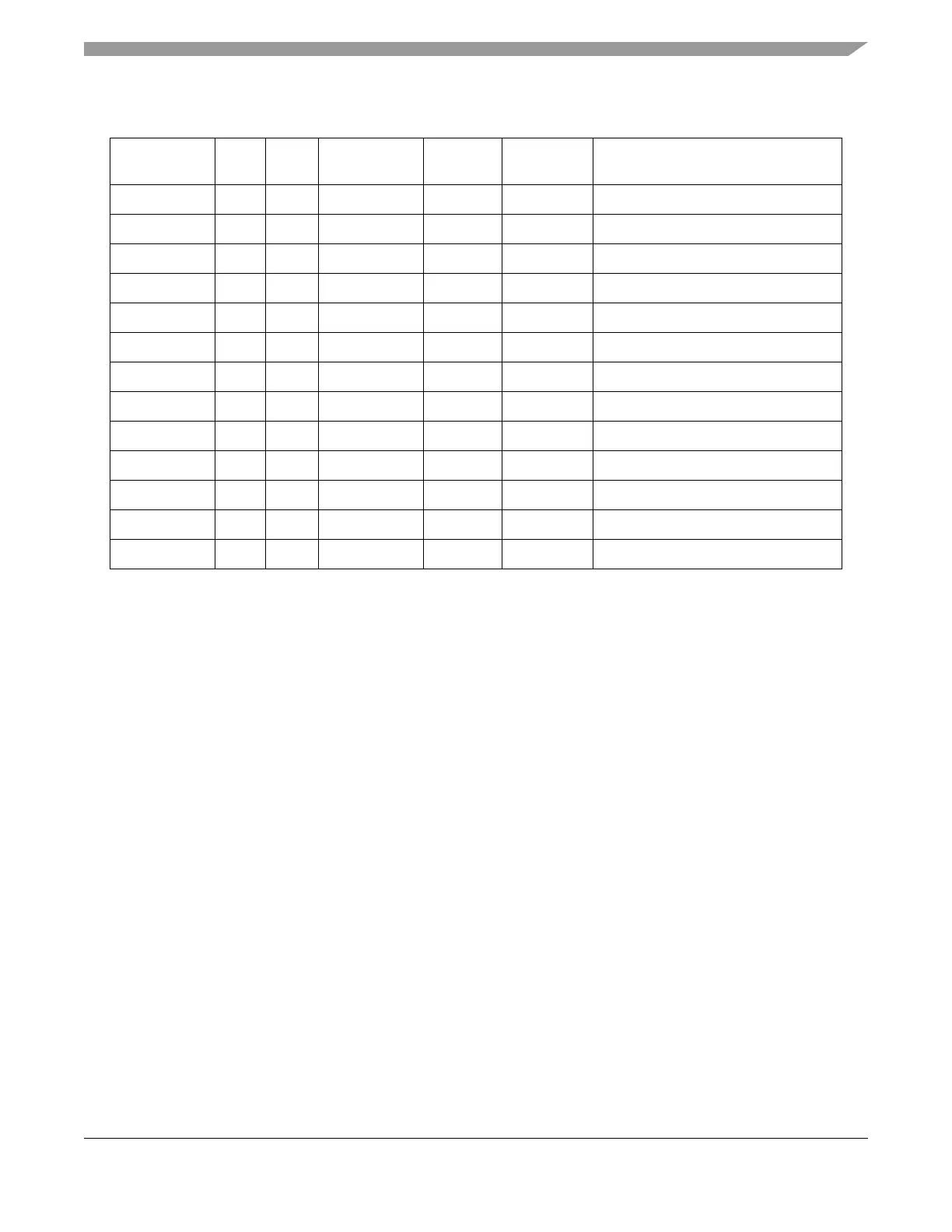

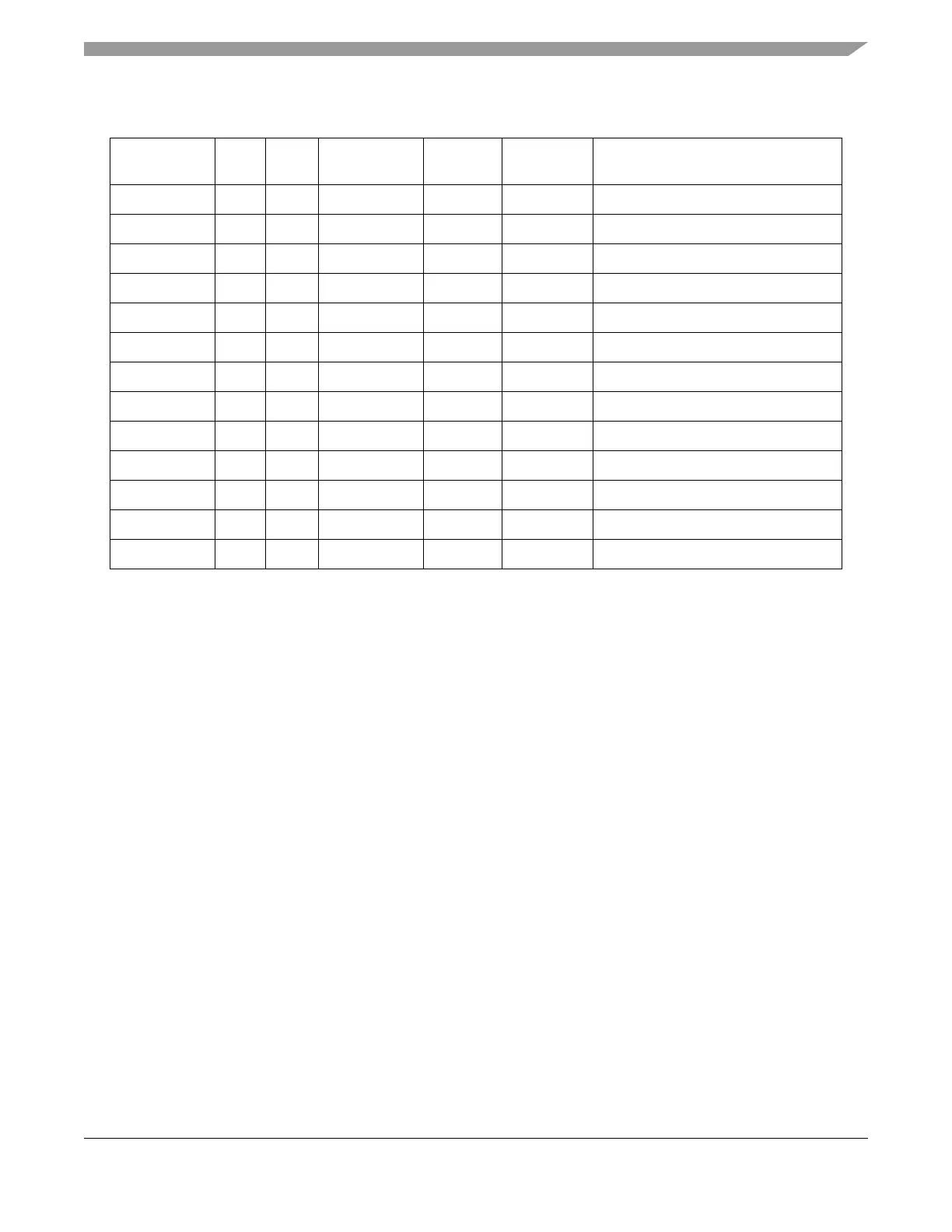

Table 10-28. COP condition (run, static) in Stop Mode

Three control bits in the CPMUCOP register allow selection of seven COP time-out periods.

When COP is enabled, the program must write $55 and $AA (in this order) to the CPMUARMCOP

register during the selected time-out period. Once this is done, the COP time-out period is restarted. If the

program fails to do this and the COP times out, a COP reset is generated. Also, if any value other than $55

or $AA is written, a COP reset is generated.

Windowed COP operation is enabled by setting WCOP in the CPMUCOP register. In this mode, writes to

the CPMUARMCOP register to clear the COP timer must occur in the last 25% of the selected time-out

period. A premature write will immediately reset the part.

10.5.3 Power-On Reset (POR)

The on-chip POR circuitry detects when the internal supply VDD drops below an appropriate voltage

level. The POR is deasserted, if the internal supply VDD exceeds an appropriate voltage level (voltage

levels are not specified in this document because this internal supply is not visible on device pins).

10.5.4 Low-Voltage Reset (LVR)

The on-chip LVR circuitry detects when one of the supply voltages VDD, VDDF or VDDX drops below

an appropriate voltage level. If LVR is deasserted the MCU is fully operational at the specified maximum

speed. The LVR assert and deassert levels for the supply voltage VDDX are V

LVRXA

and V

LVRXD

and are

specified in the device Reference Manual.

COPOSCSEL1 PSTP PCE COPOSCSEL0 OSCE UPOSC COP counter behavior in Stop Mode

(clock source)

1 x x x x x Run (ACLK)

0 1 1 1 1 1 Run (OSCCLK)

0 1 1 0 0 x Static (IRCCLK)

0 1 1 0 1 x Static (IRCCLK)

0 1 0 0 x x Static (IRCCLK)

0 1 0 1 1 1 Static (OSCCLK)

0 0 1 1 1 1 Static (OSCCLK)

0 0 1 0 1 x Static (IRCCLK)

0 0 1 0 0 0 Static (IRCCLK)

0 0 0 1 1 1 Satic (OSCCLK)

0 0 0 0 1 1 Static (IRCCLK)

0 0 0 0 1 0 Static (IRCCLK)

0 0 0 0 0 0 Static (IRCCLK)

Loading...

Loading...