Device Overview MC9S12G-Family

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 143

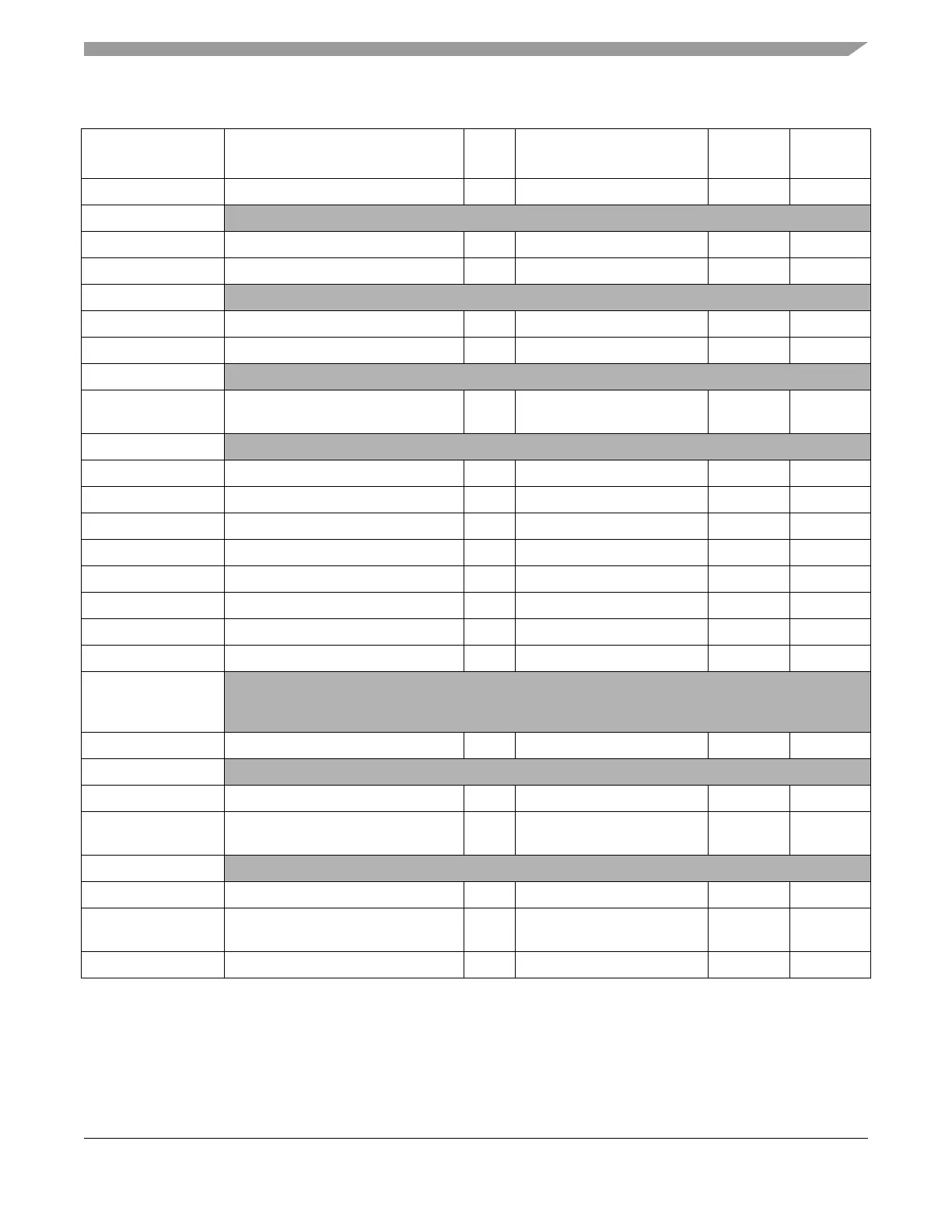

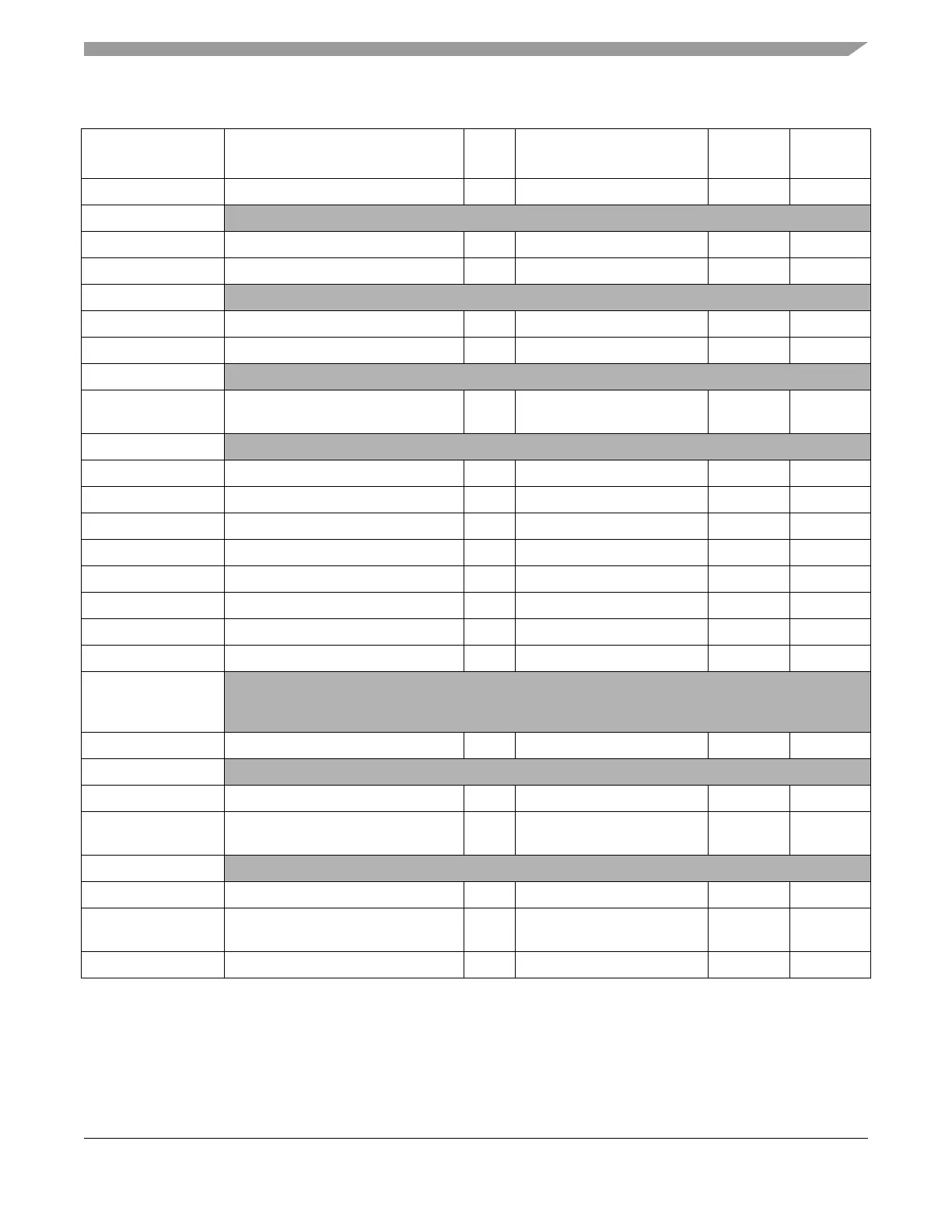

Vector base + $D2 ADC I bit ATDCTL2 (ASCIE) No Yes

Vector base + $D0

Reserved

Vector base + $CE Port J I bit PIEJ (PIEJ7-PIEJ0) Yes Yes

Vector base + $CC ACMP I bit ACMPC (ACIE) No Yes

Vector base + $CA

Reserved

Vector base + $C8 Oscillator status interrupt I bit CPMUINT (OSCIE) No Yes

Vector base + $C6 PLL lock interrupt I bit CPMUINT (LOCKIE) No Yes

Vector base + $C4

Reserved

Vector base + $C2 SCI2 I bit SCI2CR2

(TIE, TCIE, RIE, ILIE)

Yes Yes

Vector base + $C0 Reserved

Vector base + $BE SPI1 I bit SPI1CR1 (SPIE, SPTIE) No Yes

Vector base + $BC SPI2 I bit SPI2CR1 (SPIE, SPTIE) No Yes

Vector base + $BA FLASH error I bit FERCNFG (SFDIE, DFDIE) No No

Vector base + $B8 FLASH command I bit FCNFG (CCIE) No Yes

Vector base + $B6 CAN wake-up I bit CANRIER (WUPIE) Yes Yes

Vector base + $B4 CAN errors I bit CANRIER (CSCIE, OVRIE) No Yes

Vector base + $B2 CAN receive I bit CANRIER (RXFIE) No Yes

Vector base + $B0 CAN transmit I bit CANTIER (TXEIE[2:0]) No Yes

Vector base + $AE

to

Vector base + $90

Reserved

Vector base + $8E Port P interrupt I bit PIEP (PIEP7-PIEP0) Yes Yes

Vector base+ $8C

Reserved

Vector base + $8A Low-voltage interrupt (LVI) I bit CPMUCTRL (LVIE) No Yes

Vector base + $88 Autonomous periodical interrupt

(API)

I bit CPMUAPICTRL (APIE) Yes Yes

Vector base + $86

Reserved

Vector base + $84 ADC compare interrupt I bit ATDCTL2 (ACMPIE) No Yes

Vector base + $82 Port AD interrupt I bit PIE1AD(PIE1AD7-PIE1AD0)

PIE0AD(PIE0AD7-PIE0AD0)

Yes Yes

Vector base + $80 Spurious interrupt — None - -

1

16 bits vector address based

2

Only available if the 8 channel timer module is instantiated on the device

3

Only available if the 8 channel timer module is instantiated on the device

Table 1-35. Interrupt Vector Locations (Sheet 2 of 2)

Vector Address

1

Interrupt Source

CCR

Mask

Local Enable

Wake up

from STOP

Wakeup

from WAIT

Loading...

Loading...