Port Integration Module (S12GPIMV1)

MC9S12G Family Reference Manual Rev.1.27

164 NXP Semiconductors

• When routing of ADC channels to PC4-PC0 is selected

(PRR1[PRR1AN]=1) the related bit in the ADC Digital Input Enable

Register (ATDDIEN) must be set to 1 to activate the digital input

function on those pins not used as ADC inputs. If the external trigger

source is one of the ADC channels, the digital input buffer of this

channel is automatically enabled.

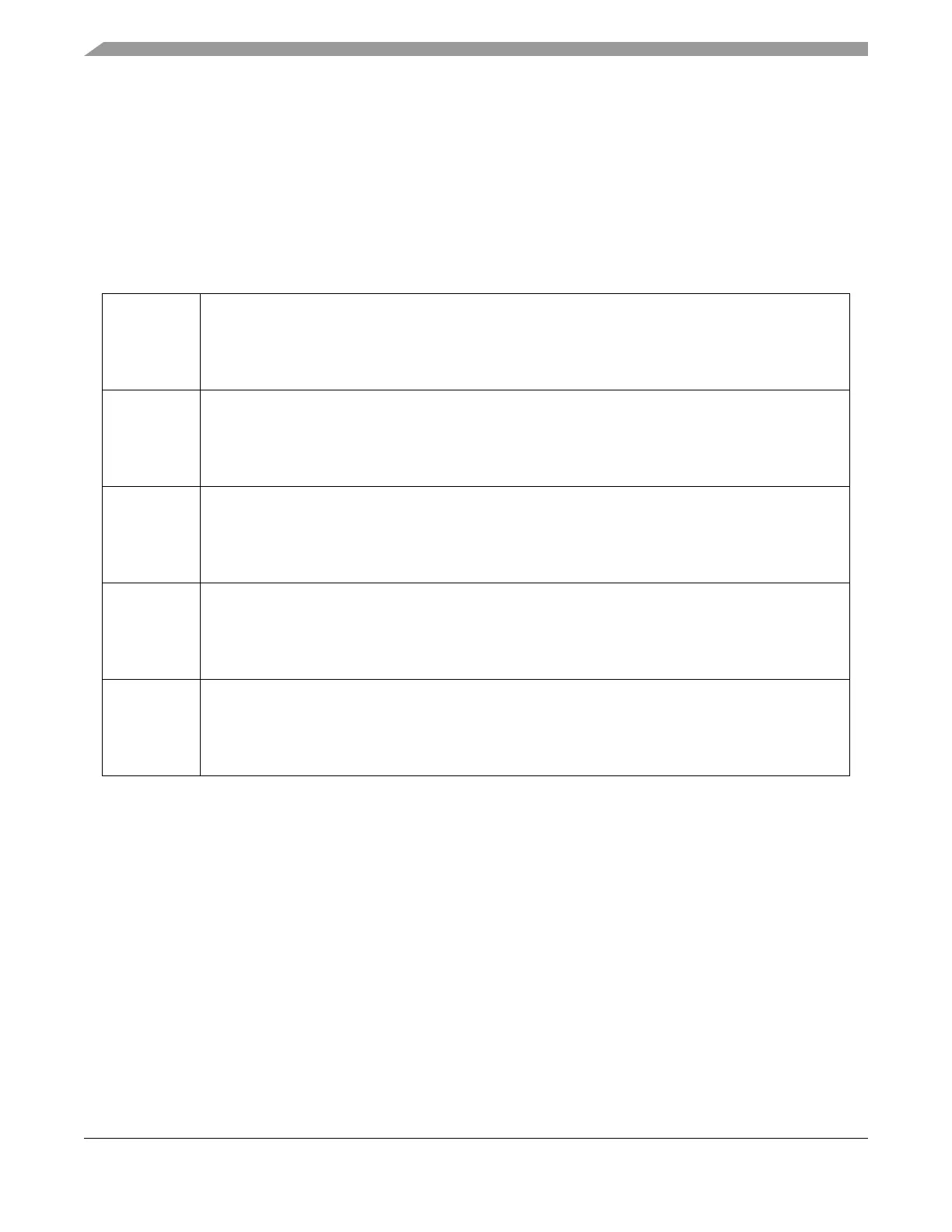

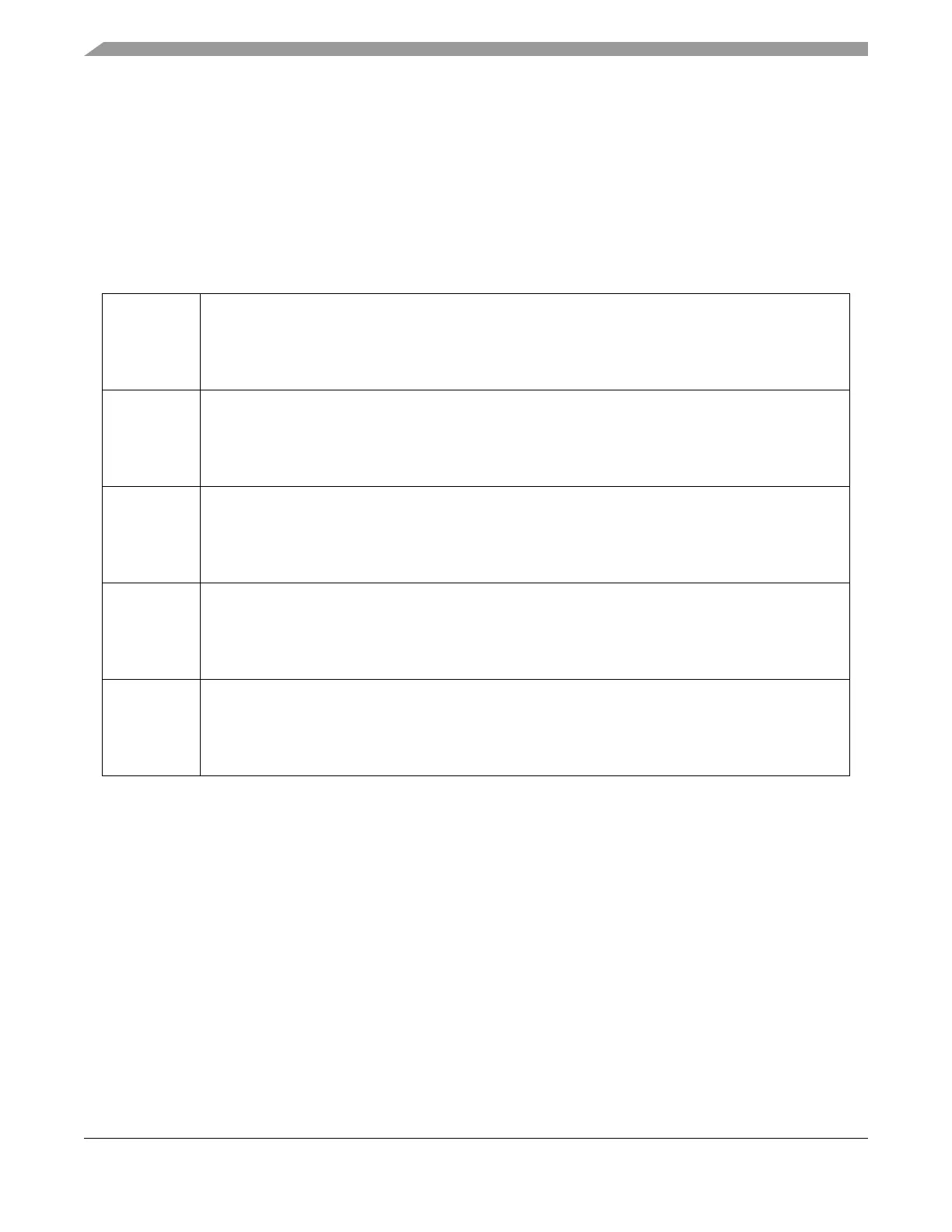

Table 2-8. Port C Pins PC7-0

PC7 • 100 LQFP: The unbuffered analog output signal DACU1 of the DAC1 module is mapped to this pin if

the DAC is operating in “unbuffered DAC” mode. If this pin is used with the DAC then the digital I/O

function and pull device are disabled.

• Signal priority:

100 LQFP: DACU1 > GPO

PC6 • 100 LQFP: The non-inverting analog input signal AMPP1 of the DAC1 module is mapped to this pin if

the DAC is operating in “unbuffered DAC with operational amplifier” or “operational amplifier only”

mode. If this pin is used with the DAC then the digital input buffer is disabled.

• Signal priority:

100 LQFP: GPO

PC5 • 100 LQFP: The inverting analog input signal AMPM1 of the DAC1 module is mapped to this pin if the

DAC is operating in “unbuffered DAC with operational amplifier” or “operational amplifier only” mode.

If this pin is used with the DAC then the digital input buffer is disabled.

• Signal priority:

100 LQFP: GPO

PC4-PC2 • 100 LQFP: If routing is active (PRR1[PRR1AN]=1) the ADC analog input channel signals AN15-13 and

their related digital trigger inputs are mapped to these pins. The routed ADC function has no effect on

the output state. Refer to NOTE/2-163 for input buffer control.

• Signal priority:

100 LQFP: GPO

PC1-PC0 • 100 LQFP: If routing is active (PRR1[PRR1AN]=1) the ADC analog input channel signals AN11-10 and

their related digital trigger inputs are mapped to these pins. The routed ADC function has no effect on

the output state. Refer to NOTE/2-163 for input buffer control.

• Signal priority:

100 LQFP: GPO

Loading...

Loading...