Analog-to-Digital Converter (ADC12B12CV2)

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 495

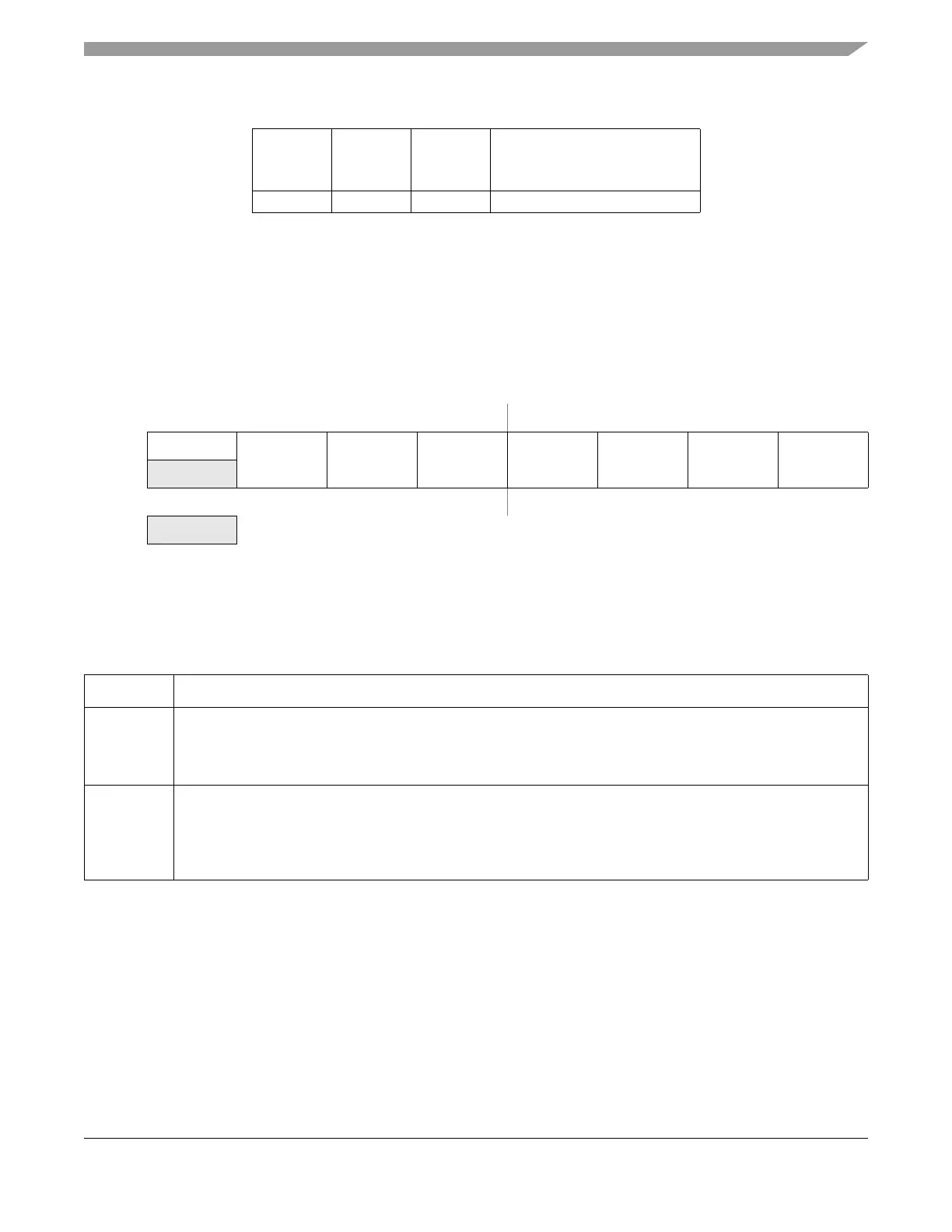

14.3.2.6 ATD Control Register 5 (ATDCTL5)

Writes to this register will abort current conversion sequence and start a new conversion sequence. If the

external trigger function is enabled (ETRIGE=1) an initial write to ATDCTL5 is required to allow starting

of a conversion sequence which will then occur on each trigger event. Start of conversion means the

beginning of the sampling phase.

Read: Anytime

Write: Anytime

111 24

Module Base + 0x0005

76543210

R0

SC SCAN MULT CD CC CB CA

W

Reset00000000

= Unimplemented or Reserved

Figure 14-8. ATD Control Register 5 (ATDCTL5)

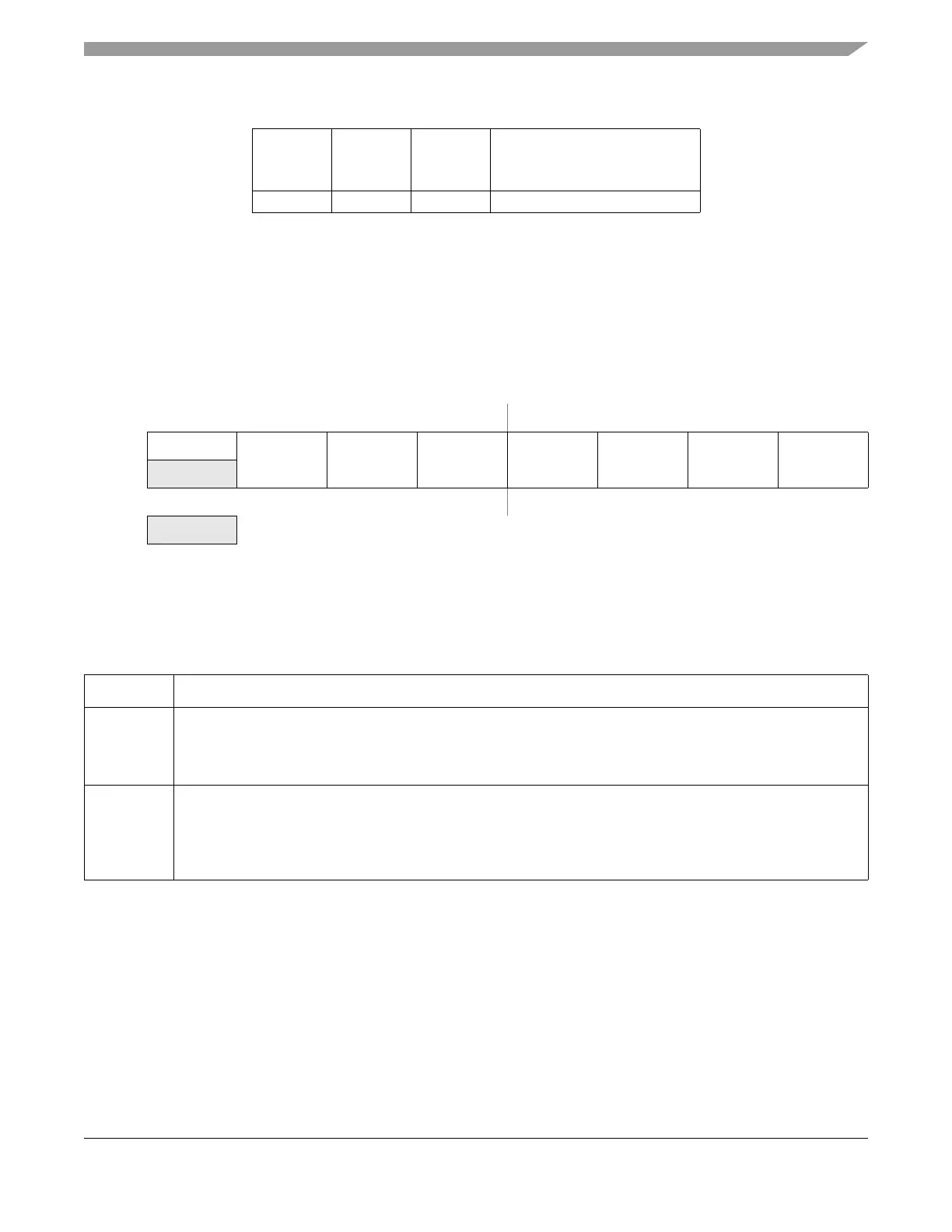

Table 14-14. ATDCTL5 Field Descriptions

Field Description

6

SC

Special Channel Conversion Bit — If this bit is set, then special channel conversion can be selected using CD,

CC, CB and CA of ATDCTL5. Table 14-15 lists the coding.

0 Special channel conversions disabled

1 Special channel conversions enabled

5

SCAN

Continuous Conversion Sequence Mode — This bit selects whether conversion sequences are performed

continuously or only once. If the external trigger function is enabled (ETRIGE=1) setting this bit has no effect,

thus the external trigger always starts a single conversion sequence.

0 Single conversion sequence

1 Continuous conversion sequences (scan mode)

Table 14-13. Sample Time Select

SMP2 SMP1 SMP0

Sample Time

in Number of

ATD Clock Cycles

Loading...

Loading...