Analog-to-Digital Converter (ADC12B16CV2)

MC9S12G Family Reference Manual Rev.1.27

550 NXP Semiconductors

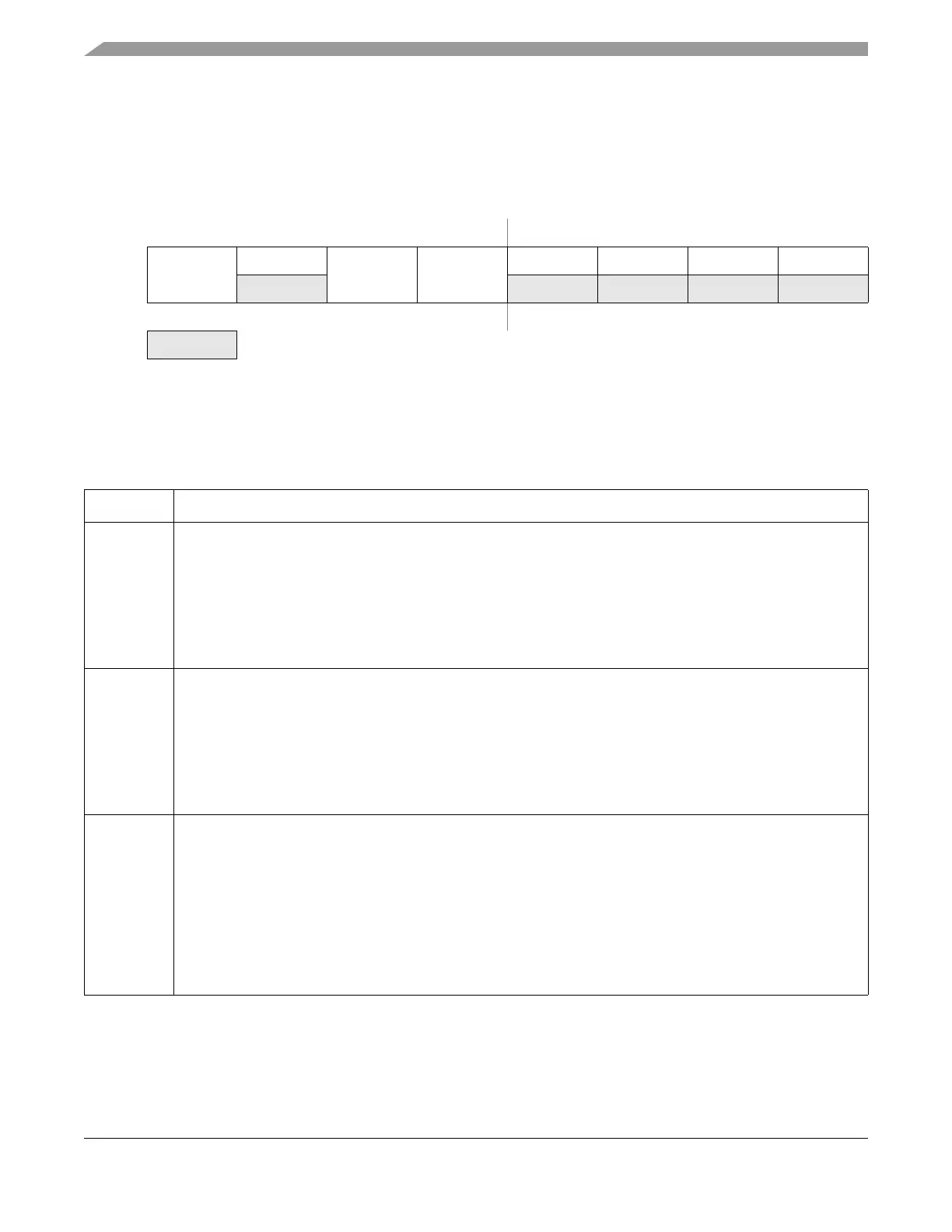

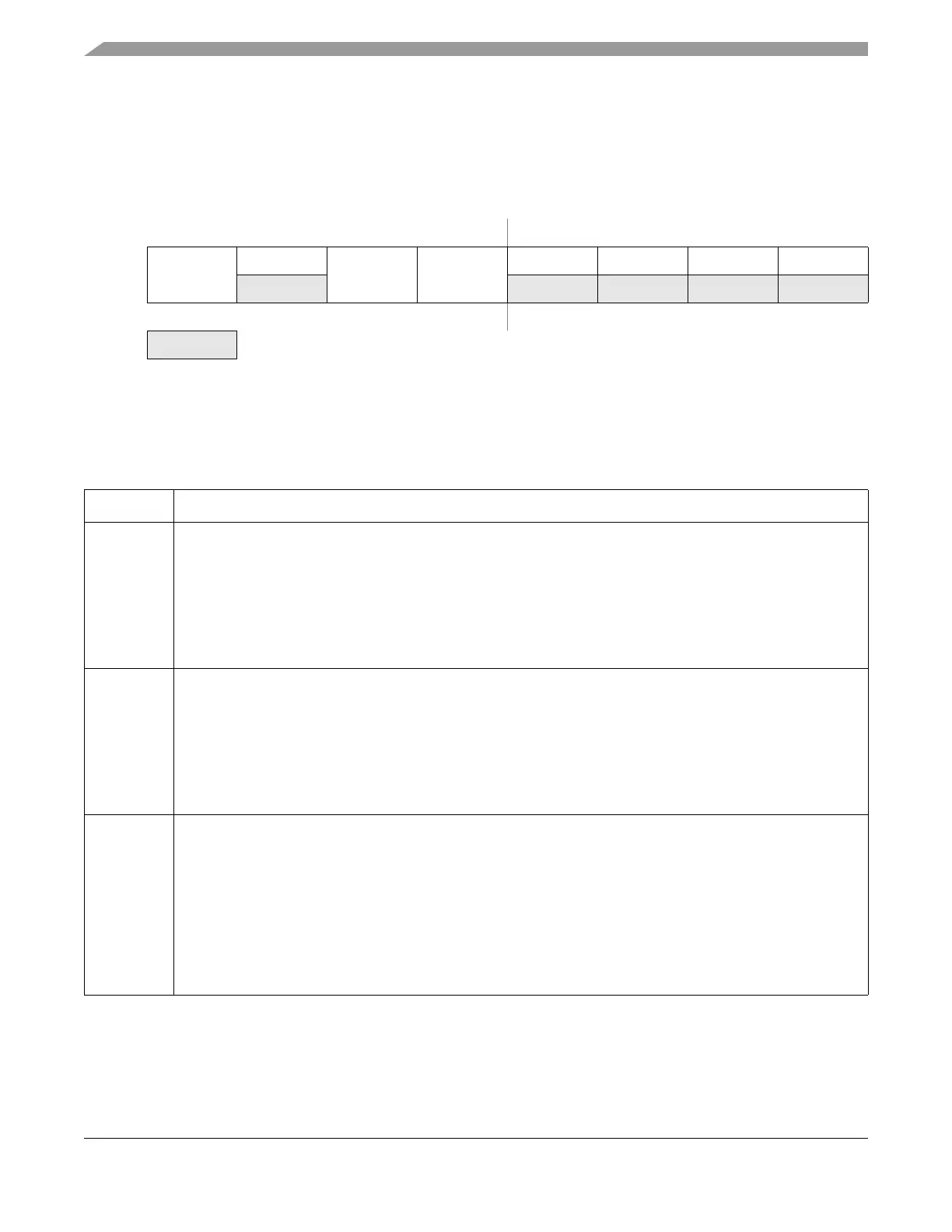

16.3.2.7 ATD Status Register 0 (ATDSTAT0)

This register contains the Sequence Complete Flag, overrun flags for external trigger and FIFO mode, and

the conversion counter.

Read: Anytime

Write: Anytime (No effect on (CC3, CC2, CC1, CC0))

Module Base + 0x0006

76543210

R

SCF

0

ETORF FIFOR

CC3 CC2 CC1 CC0

W

Reset00000000

= Unimplemented or Reserved

Figure 16-9. ATD Status Register 0 (ATDSTAT0)

Table 16-16. ATDSTAT0 Field Descriptions

Field Description

7

SCF

Sequence Complete Flag — This flag is set upon completion of a conversion sequence. If conversion

sequences are continuously performed (SCAN=1), the flag is set after each one is completed. This flag is cleared

when one of the following occurs:

A) Write “1” to SCF

B) Write to ATDCTL5 (a new conversion sequence is started)

C) If AFFC=1 and a result register is read

0 Conversion sequence not completed

1 Conversion sequence has completed

5

ETORF

External Trigger Overrun Flag — While in edge sensitive mode (ETRIGLE=0), if additional active edges are

detected while a conversion sequence is in process the overrun flag is set. This flag is cleared when one of the

following occurs:

A) Write “1” to ETORF

B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)

C) Write to ATDCTL5 (a new conversion sequence is started)

0 No External trigger overrun error has occurred

1 External trigger overrun error has occurred

4

FIFOR

Result Register Overrun Flag — This bit indicates that a result register has been written to before its associated

conversion complete flag (CCF) has been cleared. This flag is most useful when using the FIFO mode because

the flag potentially indicates that result registers are out of sync with the input channels. However, it is also

practical for non-FIFO modes, and indicates that a result register has been overwritten before it has been read

(i.e. the old data has been lost). This flag is cleared when one of the following occurs:

A) Write “1” to FIFOR

B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)

C) Write to ATDCTL5 (a new conversion sequence is started)

0 No overrun has occurred

1 Overrun condition exists (result register has been written while associated CCFx flag was still set)

Loading...

Loading...