Device Overview MC9S12G-Family

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 57

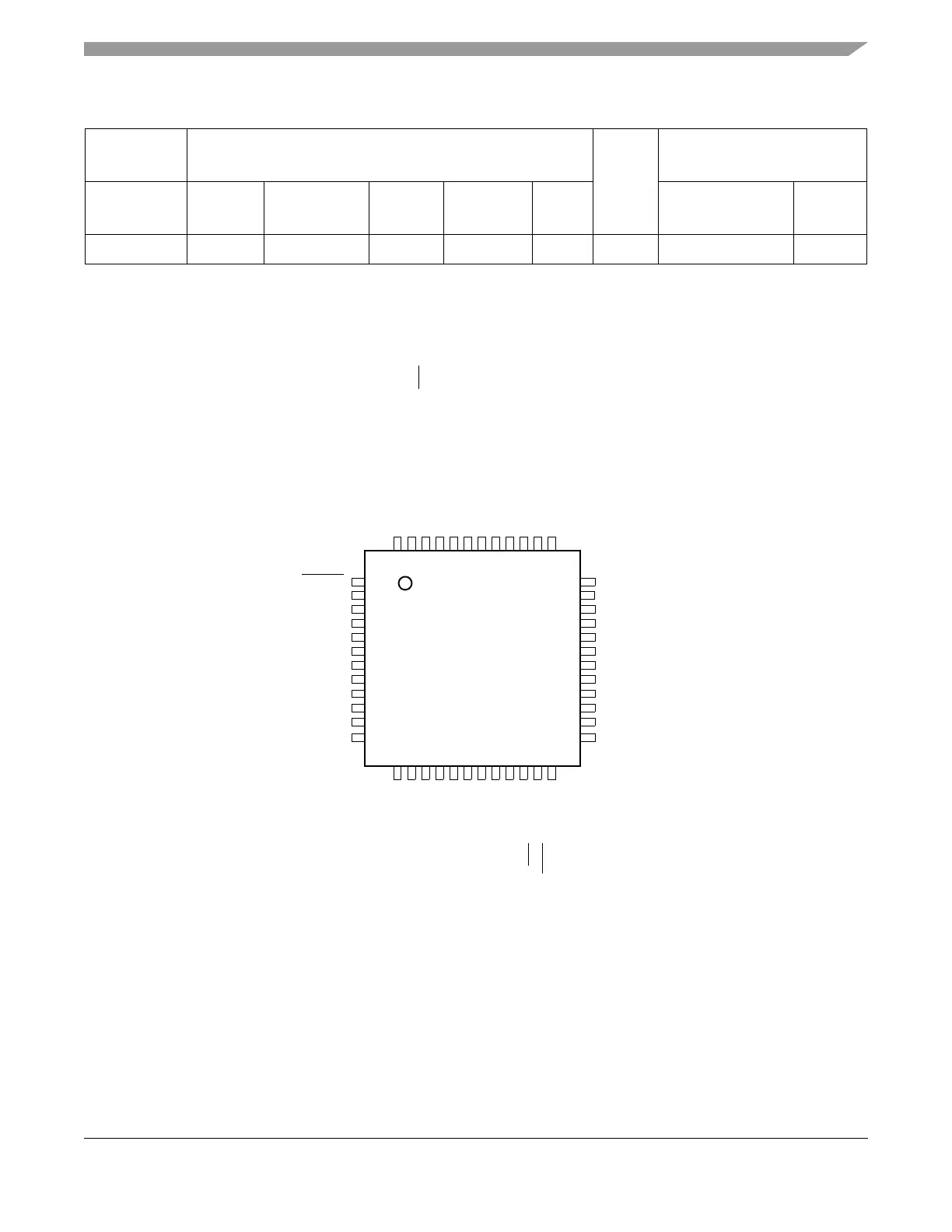

1.8.1.3 Pinout 48-Pin LQFP/QFN

Figure 1-5. 48-Pin LQFP/QFN Pinout for S12GN16 and S12GN32

32 PM1 — — — — V

DDX

PERM/PPSM Disabled

1

The regular I/O characteristics (see Section A.2, “I/O Characteristics”) apply if the EXTAL/XTAL function is disabled

Table 1-9. 32-Pin LQFP OPinout for S12GN16 and S12GN32

Function

<----lowest-----PRIORITY-----highest---->

Power

Supply

Internal Pull

Resistor

Package Pin Pin

2nd

Func.

3rd

Func.

4th

Func

5th

Func

CTRL

Reset

State

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

36

35

34

33

32

31

30

29

28

27

26

25

48

47

46

45

44

43

42

41

40

39

38

37

S12GN16

S12GN32

48-Pin LQFP/QFN

PAD7/KWAD7/AN7

PAD6/KWAD6/AN6

PAD5/KWAD5/AN5

PAD4/KWAD4/AN4

PAD11/KWAD11/ACMPM

PAD3/KWAD3/AN3

PAD10/KWAD10/ACMPP

PAD2/KWAD2/AN2

PAD9/KWAD9/ACMPO

PAD1/KWAD1/AN1

PAD8/KWAD8

PAD0/KWAD0/AN0

PWM0/API_EXTCLK/ETRIG0/KWP0/PP0

PWM1/ECLKX2/ETRIG1/KWP1/PP1

PWM2/ETRIG2/KWP2/PP2

PWM3/ETRIG3/KWP3/PP3

PWM4/KWP4/PP4

PWM5/KWP5/PP5

IOC5/PT5

IOC4/PT4

IOC3/PT3

IOC2/PT2

IRQ

/IOC1/PT1

XIRQ

/IOC0/PT0

RESET

VDDXR

VSSX

EXTAL/PE0

VSS

XTAL/PE1

TEST

KWJ0/PJ0

KWJ1/PJ1

KWJ2/PJ2

KWJ3/PJ3

BKGD

PM1

PM0

PS7/API_EXTCLK/ECLK/SS0

PS6/SCK0

PS5/MOSI0

PS4/MISO0

PS3

PS2

PS1/TXD0

PS0/RXD0

VSSA

VDDA/VRH

Loading...

Loading...