Scalable Controller Area Network (S12MSCANV3)

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 581

NOTE

The CANRFLG register is held in the reset state

1

when the initialization

mode is active (INITRQ = 1 and INITAK = 1). This register is writable

again as soon as the initialization mode is exited (INITRQ = 0 and INITAK

= 0).

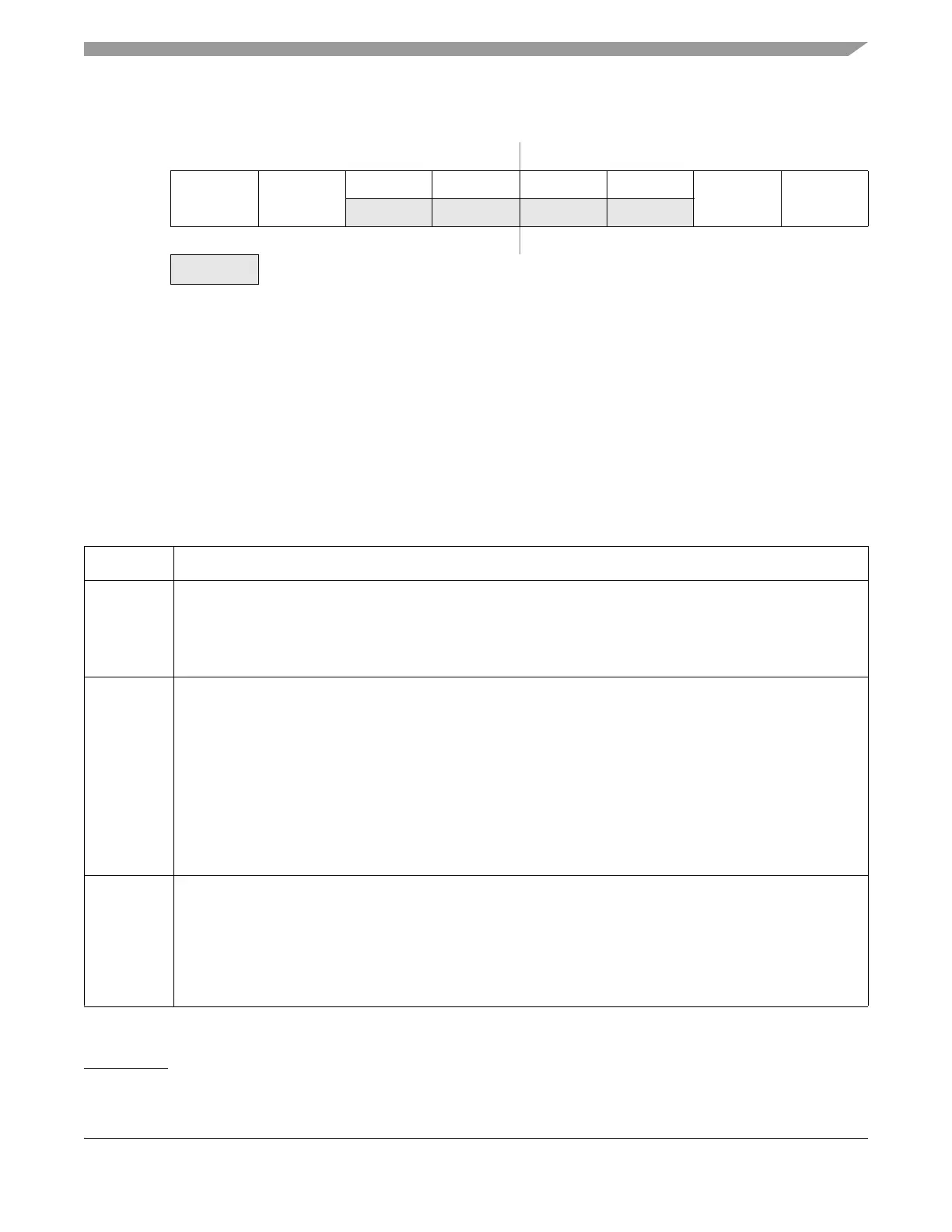

Module Base + 0x0004 Access: User read/write

1

1

Read: Anytime

Write: Anytime when not in initialization mode, except RSTAT[1:0] and TSTAT[1:0] flags which are read-only; write of 1 clears

flag; write of 0 is ignored

76543210

R

WUPIF CSCIF

RSTAT1 RSTAT0 TSTAT1 TSTAT0

OVRIF RXF

W

Reset:00000000

= Unimplemented

Figure 18-8. MSCAN Receiver Flag Register (CANRFLG)

1. The RSTAT[1:0], TSTAT[1:0] bits are not affected by initialization mode.

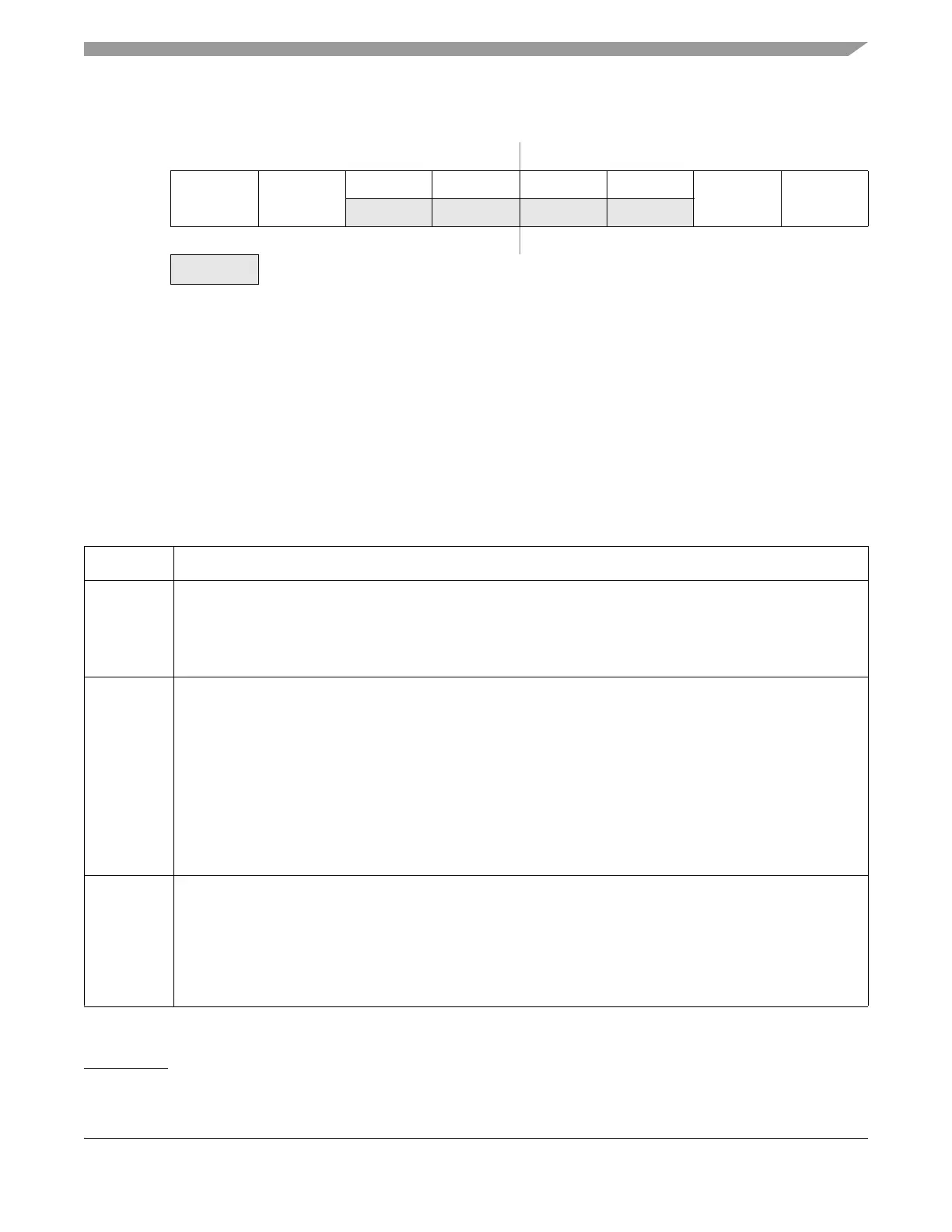

Table 18-11. CANRFLG Register Field Descriptions

Field Description

7

WUPIF

Wake-Up Interrupt Flag — If the MSCAN detects CAN bus activity while in sleep mode (see Section 18.4.5.5,

“MSCAN Sleep Mode,”) and WUPE = 1 in CANTCTL0 (see Section 18.3.2.1, “MSCAN Control Register 0

(CANCTL0)”), the module will set WUPIF. If not masked, a wake-up interrupt is pending while this flag is set.

0 No wake-up activity observed while in sleep mode

1 MSCAN detected activity on the CAN bus and requested wake-up

6

CSCIF

CAN Status Change Interrupt Flag — This flag is set when the MSCAN changes its current CAN bus status

due to the actual value of the transmit error counter (TEC) and the receive error counter (REC). An additional

4-bit (RSTAT[1:0], TSTAT[1:0]) status register, which is split into separate sections for TEC/REC, informs the

system on the actual CAN bus status (see Section 18.3.2.6, “MSCAN Receiver Interrupt Enable Register

(CANRIER)”). If not masked, an error interrupt is pending while this flag is set. CSCIF provides a blocking

interrupt. That guarantees that the receiver/transmitter status bits (RSTAT/TSTAT) are only updated when no

CAN status change interrupt is pending. If the TECs/RECs change their current value after the CSCIF is

asserted, which would cause an additional state change in the RSTAT/TSTAT bits, these bits keep their status

until the current CSCIF interrupt is cleared again.

0 No change in CAN bus status occurred since last interrupt

1 MSCAN changed current CAN bus status

5-4

RSTAT[1:0]

Receiver Status Bits — The values of the error counters control the actual CAN bus status of the MSCAN. As

soon as the status change interrupt flag (CSCIF) is set, these bits indicate the appropriate receiver related CAN

bus status of the MSCAN. The coding for the bits RSTAT1, RSTAT0 is:

00 RxOK: 0 receive error counter 96

01 RxWRN: 96 receive error counter 128

10 RxERR: 128 receive error counter

11 Bus-off

1

: transmit error counter

Loading...

Loading...