Serial Peripheral Interface (S12SPIV5)

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 711

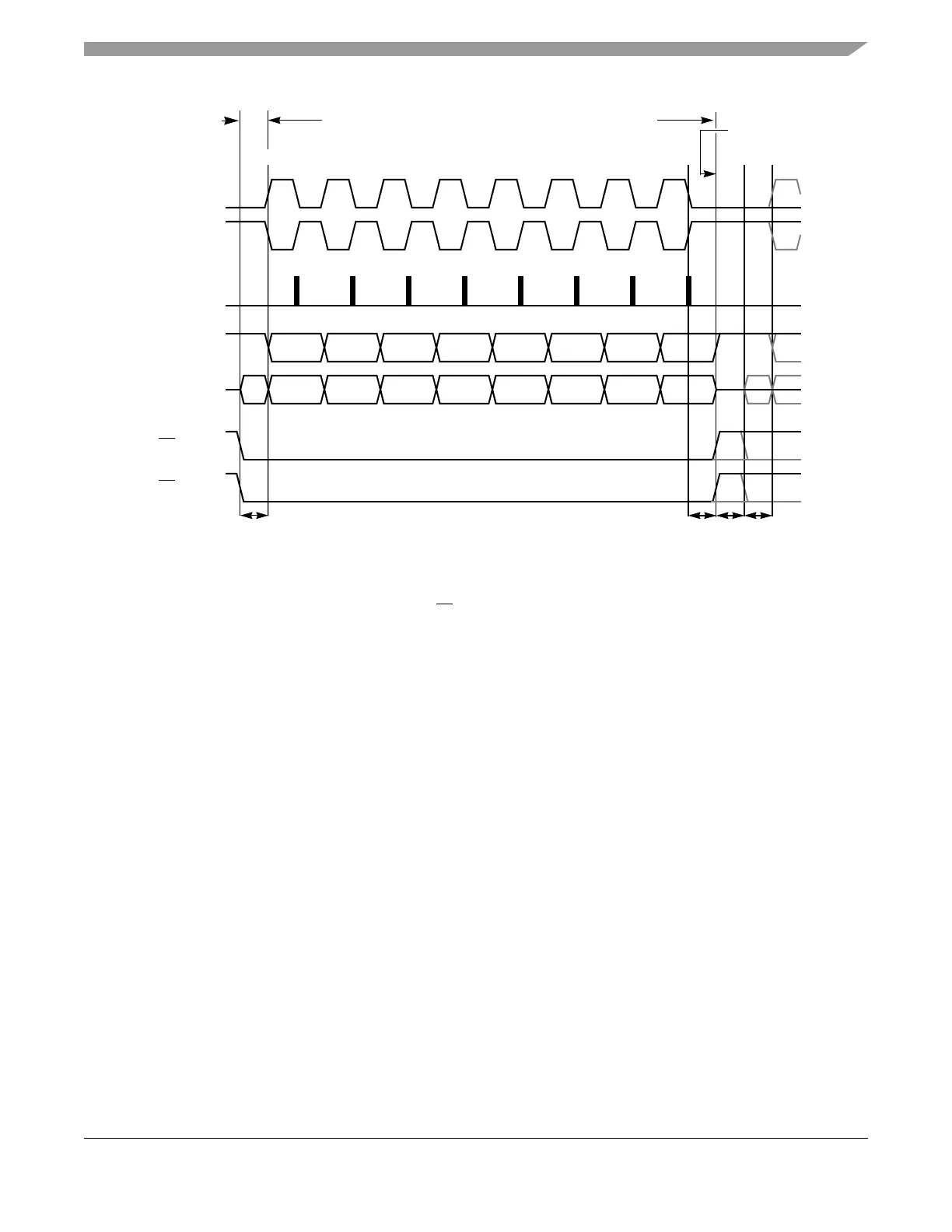

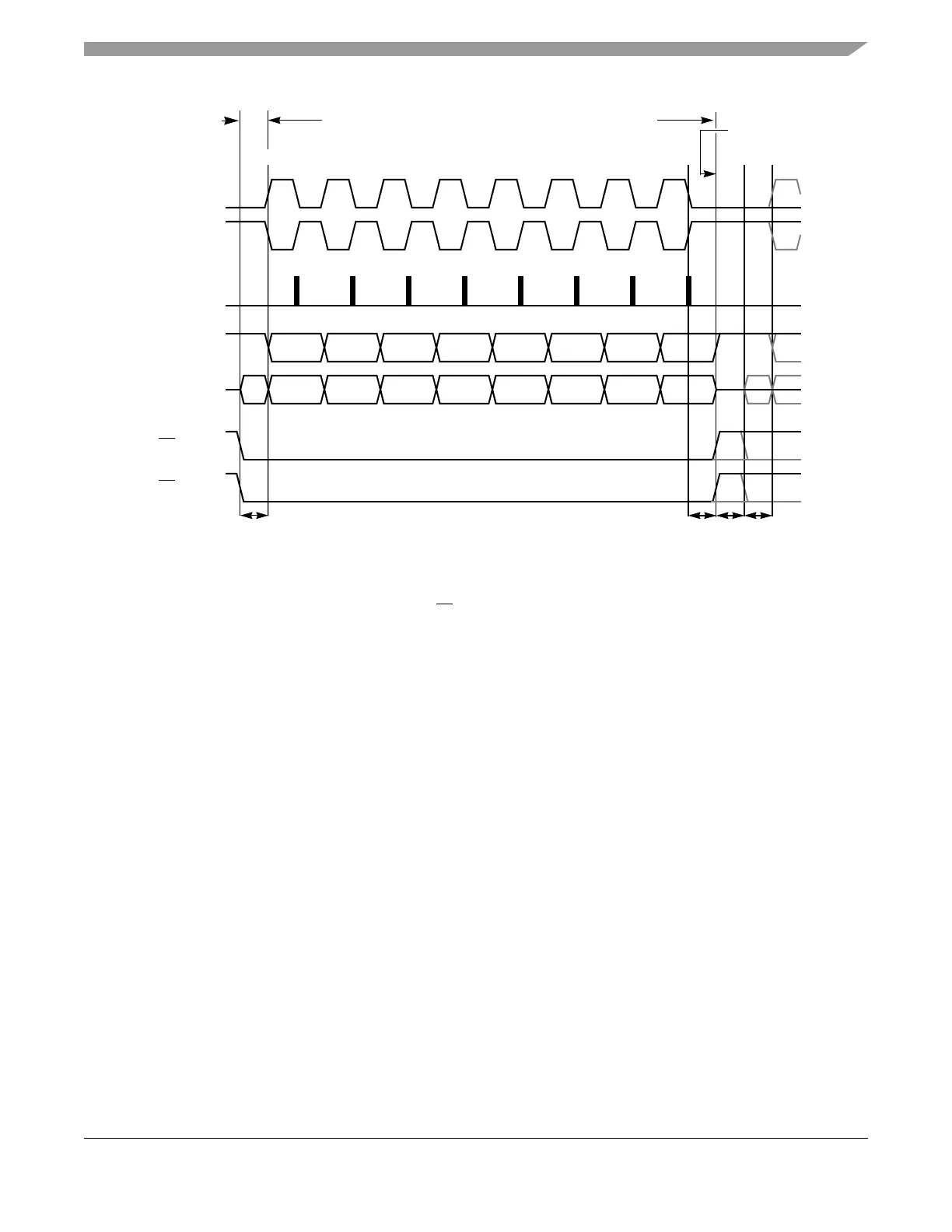

Figure 21-14. SPI Clock Format 1 (CPHA = 1), with 8-Bit Transfer Width selected (XFRW = 0)

t

L

t

T

for t

T

, t

l

, t

L

Minimum 1/2 SCK

t

I

t

L

If next transfer begins here

Begin End

SCK (CPOL = 0)

SAMPLE I

CHANGE O

SEL SS

(O)

Transfer

SCK (CPOL = 1)

MSB first (LSBFE = 0):

LSB first (LSBFE = 1):

MSB

LSB

LSB

MSB

Bit 5

Bit 2

Bit 6

Bit 1

Bit 4

Bit 3

Bit 3

Bit 4

Bit 2

Bit 5

Bit 1

Bit 6

CHANGE O

SEL SS

(I)

MOSI pin

MISO pin

Master only

MOSI/MISO

t

L

= Minimum leading time before the first SCK edge, not required for back-to-back transfers

t

T

= Minimum trailing time after the last SCK edge

t

I

= Minimum idling time between transfers (minimum SS high time), not required for back-to-back transfers

1 234 56 78910111213141516SCK Edge Number

End of Idle State

Begin of Idle State

Loading...

Loading...