64 KByte Flash Module (S12FTMRG64K1V1)

MC9S12G Family Reference Manual Rev.1.27

932 NXP Semiconductors

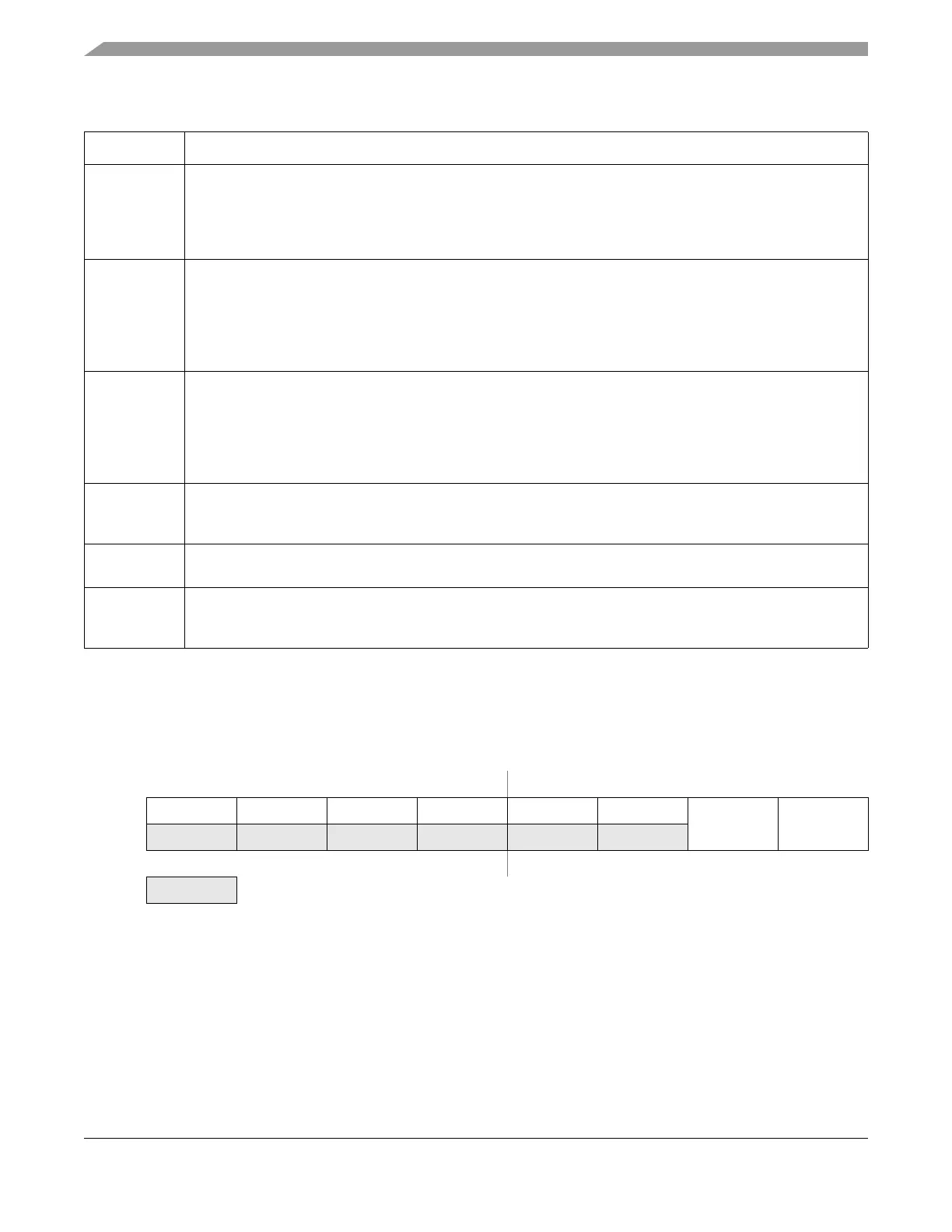

27.3.2.8 Flash Error Status Register (FERSTAT)

The FERSTAT register reflects the error status of internal Flash operations.

All flags in the FERSTAT register are readable and only writable to clear the flag.

Table 27-15. FSTAT Field Descriptions

Field Description

7

CCIF

Command Complete Interrupt Flag — The CCIF flag indicates that a Flash command has completed. The

CCIF flag is cleared by writing a 1 to CCIF to launch a command and CCIF will stay low until command

completion or command violation.

0 Flash command in progress

1 Flash command has completed

5

ACCERR

Flash Access Error Flag — The ACCERR bit indicates an illegal access has occurred to the Flash memory

caused by either a violation of the command write sequence (see Section 27.4.4.2) or issuing an illegal Flash

command. While ACCERR is set, the CCIF flag cannot be cleared to launch a command. The ACCERR bit is

cleared by writing a 1 to ACCERR. Writing a 0 to the ACCERR bit has no effect on ACCERR.

0 No access error detected

1 Access error detected

4

FPVIOL

Flash Protection Violation Flag —The FPVIOL bit indicates an attempt was made to program or erase an

address in a protected area of P-Flash or EEPROM memory during a command write sequence. The FPVIOL

bit is cleared by writing a 1 to FPVIOL. Writing a 0 to the FPVIOL bit has no effect on FPVIOL. While FPVIOL

is set, it is not possible to launch a command or start a command write sequence.

0 No protection violation detected

1 Protection violation detected

3

MGBUSY

Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller

.

0 Memory Controller is idle

1 Memory Controller is busy executing a Flash command (CCIF = 0)

2

RSVD

Reserved Bit — This bit is reserved and always reads 0

.

1–0

MGSTAT[1:0]

Memory Controller Command Completion Status Flag — One or more MGSTAT flag bits are set if an error

is detected during execution of a Flash command or during the Flash reset sequence. See Section 27.4.6,

“Flash Command Description,” and Section 27.6, “Initialization” for details.

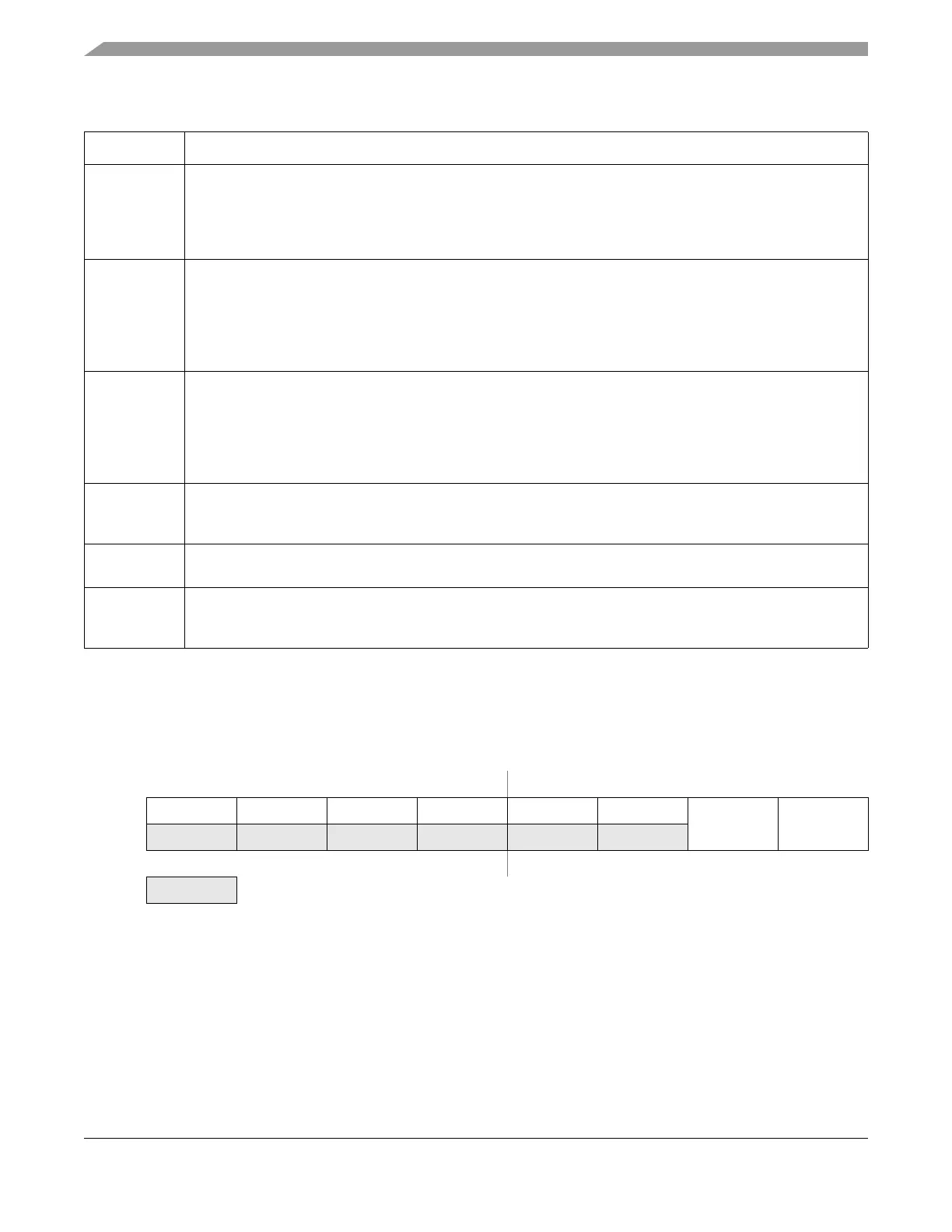

Offset Module Base + 0x0007

76543210

R000000

DFDIF SFDIF

W

Reset00000000

= Unimplemented or Reserved

Figure 27-12. Flash Error Status Register (FERSTAT)

Loading...

Loading...