RL78/G15 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0959EJ0110 Rev.1.10 Page 406 of 765

Mar 7, 2023

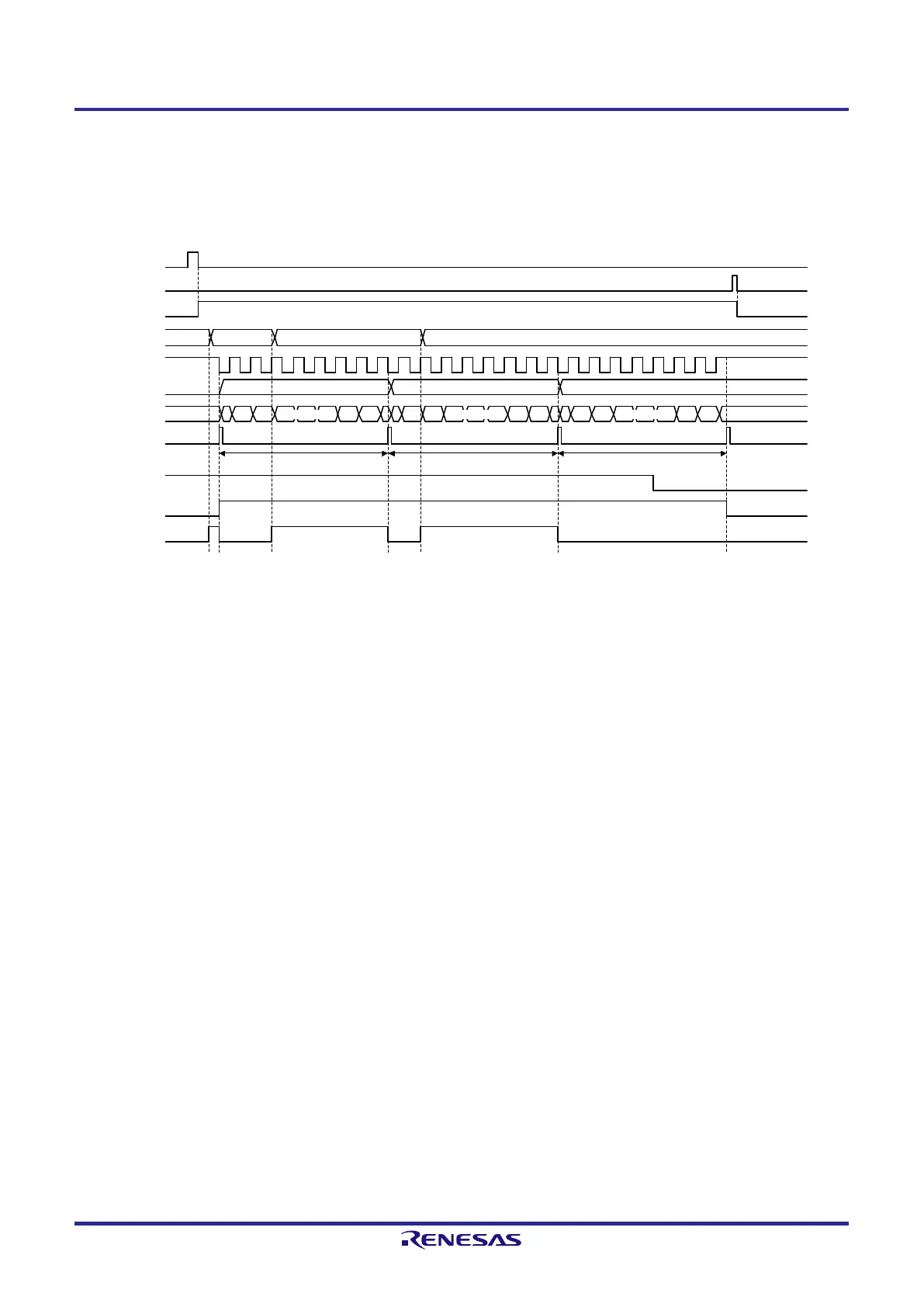

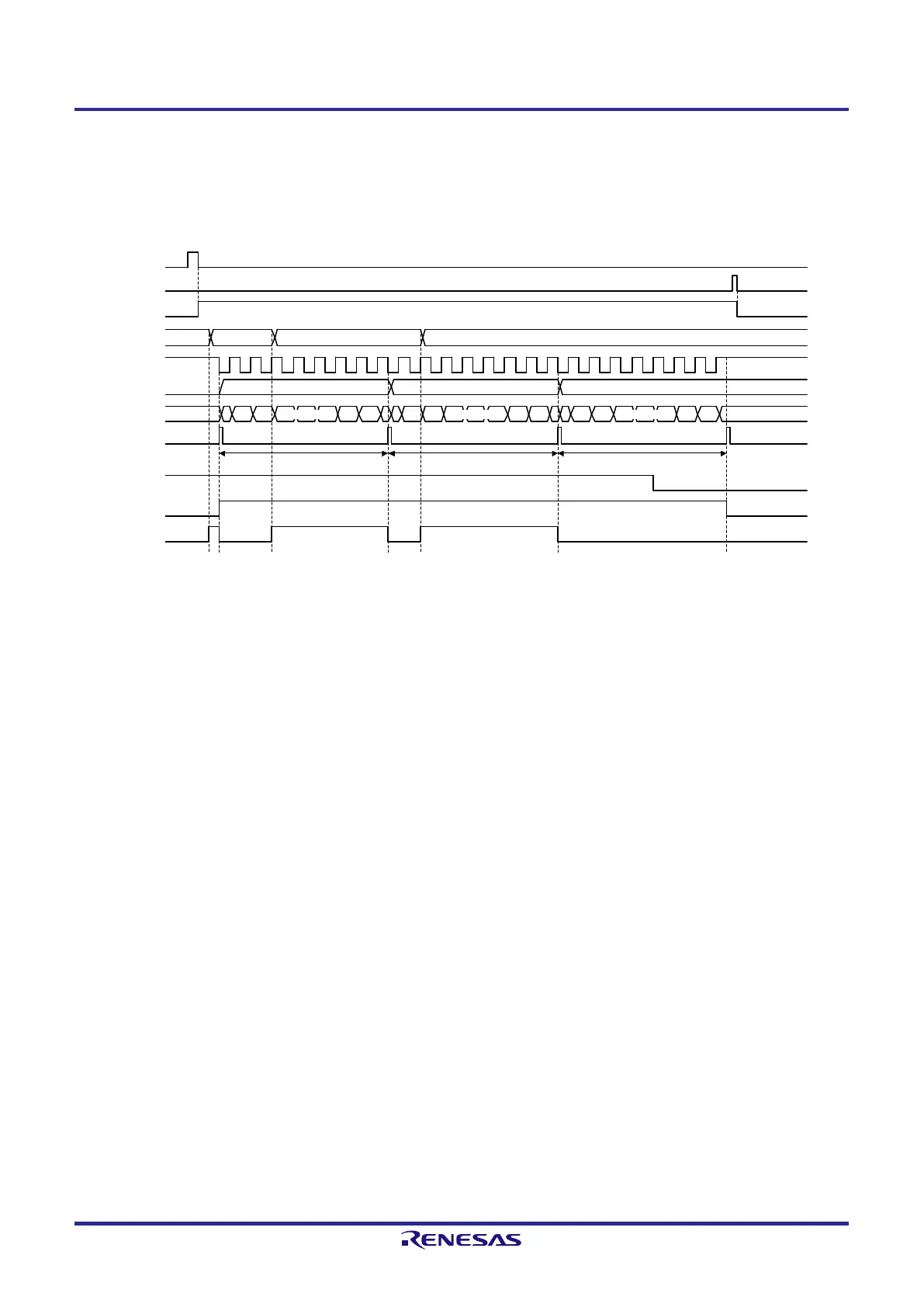

(4) Processing flow (in continuous transmission mode)

Figure 12-27. Timing Chart of Master Transmission (in Continuous Transmission Mode) (Type 1: DAPmn = 0, CKPmn =

0)

Shift

register mn

SO

p pin

SCKp pin

Data transmissionData transmissionData transmission

SSmn

STmn

SEmn

SDRmn

INTCSIp

TSFmn

Transmit data 1

Transmit data

2

Transmit data

3

Transmit data 1 Transmit data

2 Transmit data

3

Shift operation Shift operation

Shift operation

BFFmn

MDmn0

<1>

<

6>

<

4>

<2><3> <2> <3

> <2> <3>

<5>

Note 1

Note 1. If transmit data is written to the SDRmn register while the BFFmn bit of serial status register mn (SSRmn) is 1

(valid data is stored in serial data register mn (SDRmn)), the transmit data is overwritten.

Caution The MDmn0 bit of serial mode register mn (SMRmn) can be rewritten even during operation.

However, rewrite it before transfer of the last bit is started, so that it has been rewritten before the

transfer end interrupt of the last transmit data.

Remark m: Unit number (m = 0), n: Channel number (n = 0, 1), p: CSI number (p = 00, 01), mn = 00, 01

Loading...

Loading...