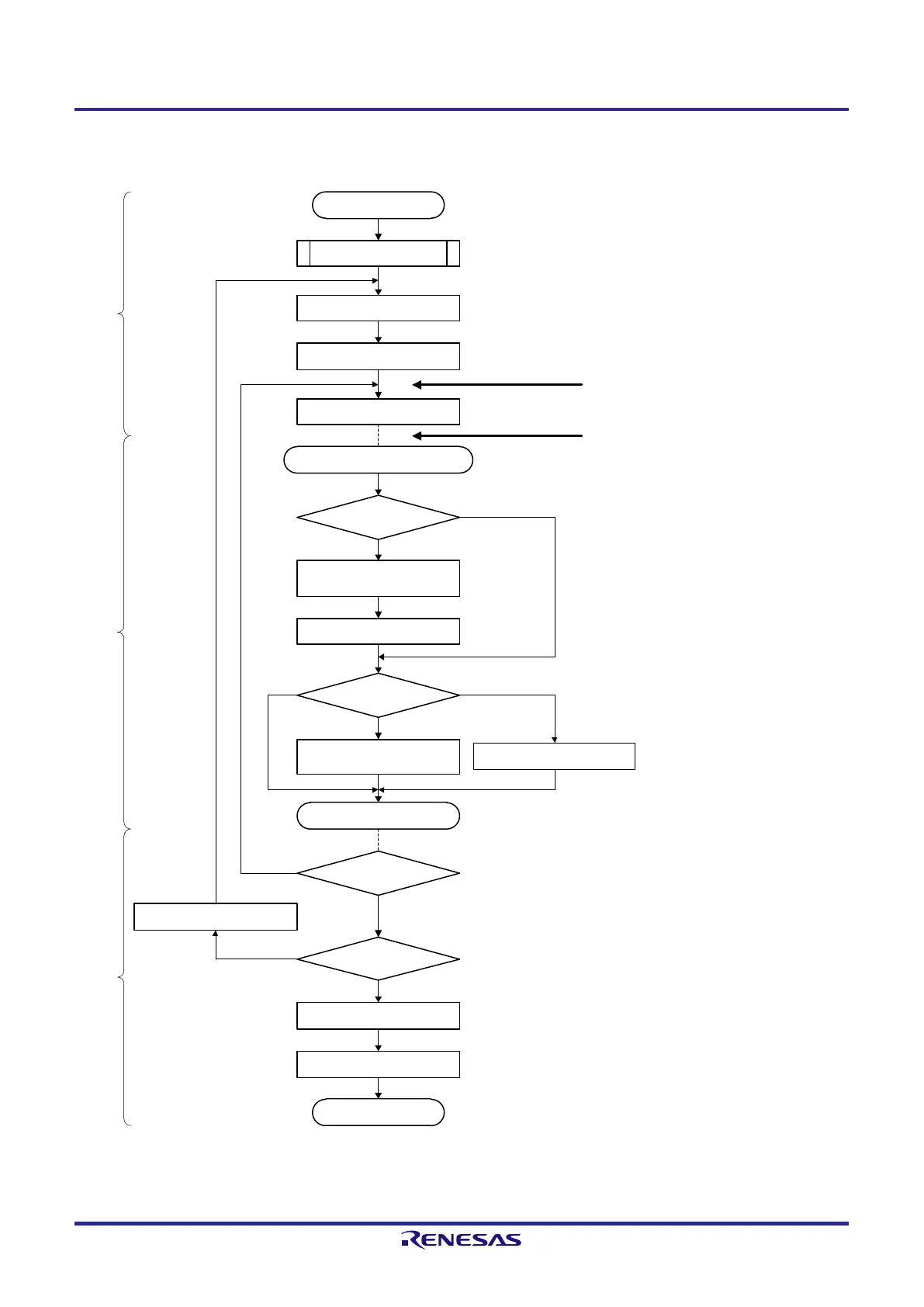

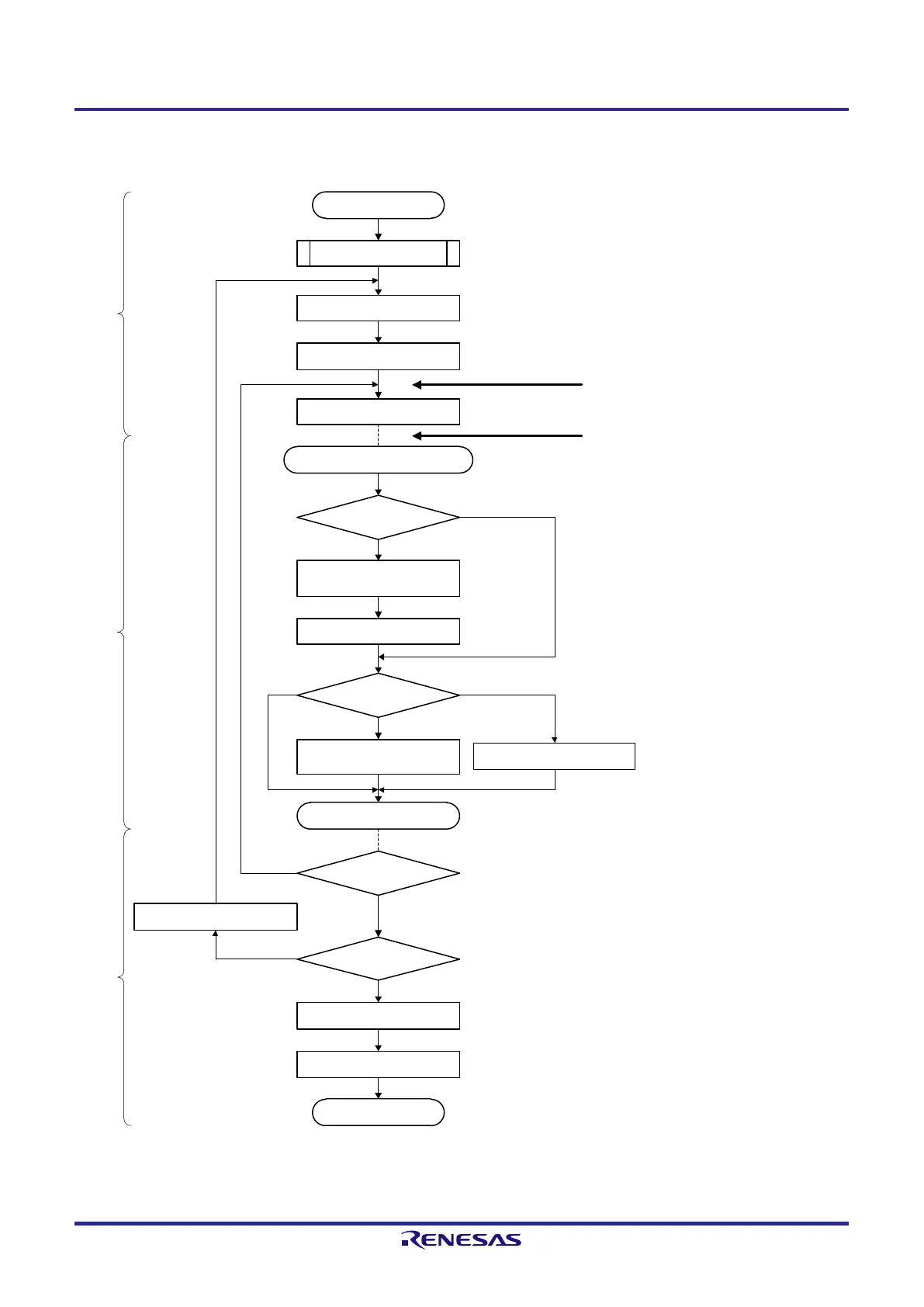

Starting setting

End of communication

Disable interrupt (MASK)

Setting storage area and number of data for transmission/reception data

(Storage area, Transmission/reception data pointer, and number of

communication data are optionally set on the internal RAM by the software)

Clear interrupt request flag (xxIF), reset interrupt mask (xxMK), and

set interrupt enable (EI)

Wait for transmission completes

Subtract –1 from number of

communication data

Read receive data from SIOp

(= SDRmn [7:0])

Number of

communication data

= 0?

RETI

Number of

communication

data?

Buffer empty/transfer end interrupt

SAU initial setting

No

Set STmn bit to 1

Communication continued?

Set MDmn0 bit to 1

Yes

Yes

No

Main routine Interrupt processing routine Main routine

<1>

<3> <6>

<8>

BFFmn = 1?

≥ 2

<4>

<7>

Enables interrupt

Setting transmission/reception data

When buffer empty/transfer end interrupt is generated,

it moves interrupt processing routine

Clear MDmn0 bit to 0

Writing transmit data to SIOp

(= SDRmn [7:0])

<5>

= 1= 0

No

Other than the first interrupt, read reception data then

writes to storage area, update receive data pointer

If transmit data is left (number of communication data ≥ 2),

read it from the storage area and write it to SIOp. Update

storage pointer.

If transmit is completed (number of communication data = 1),

the flow is changed to the transmission completion interrupt.

Start communication when master start providing

the clock

Loading...

Loading...