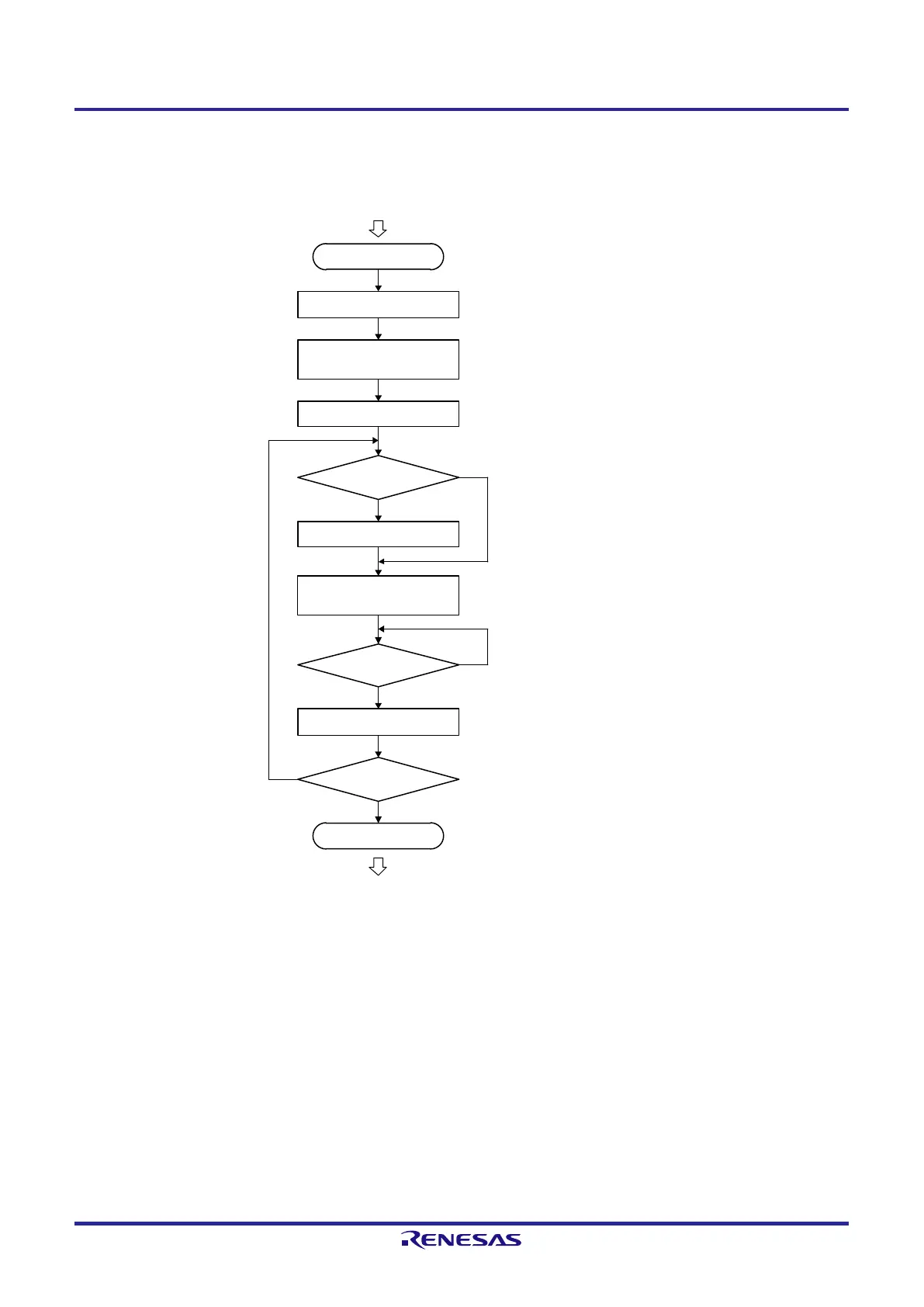

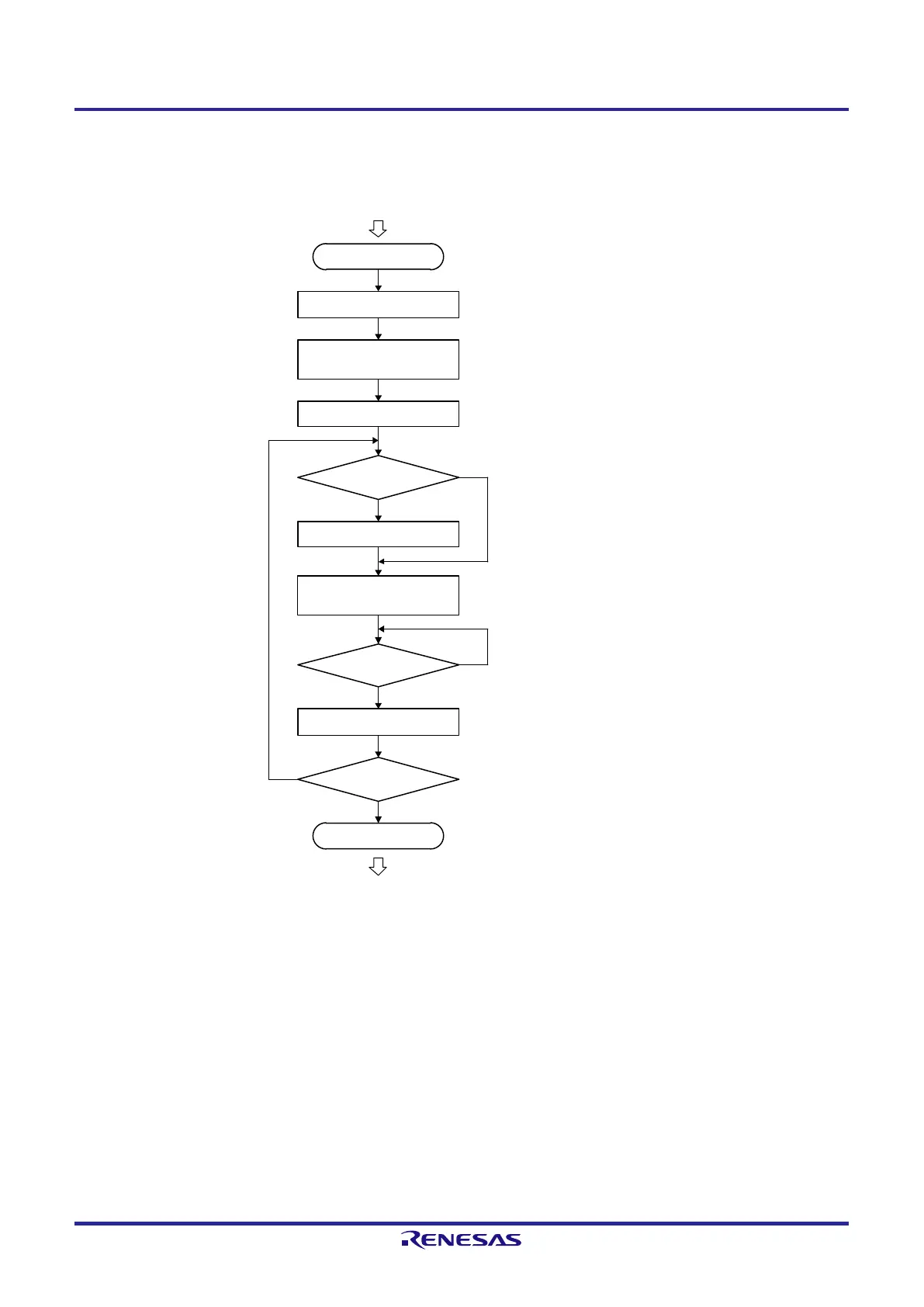

Writing dummy data (FFH) to

SIOr (SDRmn[7:0])

Data transfer completed?

Yes

Stop condition generation

Transfer end interrupt

generated?

No

No

Yes

Data reception completed

Data reception

No

Wait for the completion of reception.

(Clear the interrupt request flag)

Address field transmission

completed

Reading SIOr (SDRmn[7:0])

Writing 0 to the SOEmn bit

Last byte received?

Yes

Writing 1 to the SSmn bit

Writing 0 to the TXEmn bit, and

1 to the RXEmn bit

Writing 1 to the STmn bit

Reading receive data, perform processing

(stored in the RAM etc.).

Starting reception operation

Disable output so that not the ACK

response to the last received data.

Operation restart

Set the operation of the channel to receive-

only mode.

Stop operation for rewriting SCRmn register.

Loading...

Loading...