RL78/G15 CHAPTER 13 SERIAL INTERFACE IICA

R01UH0959EJ0110 Rev.1.10 Page 522 of 765

Mar 7, 2023

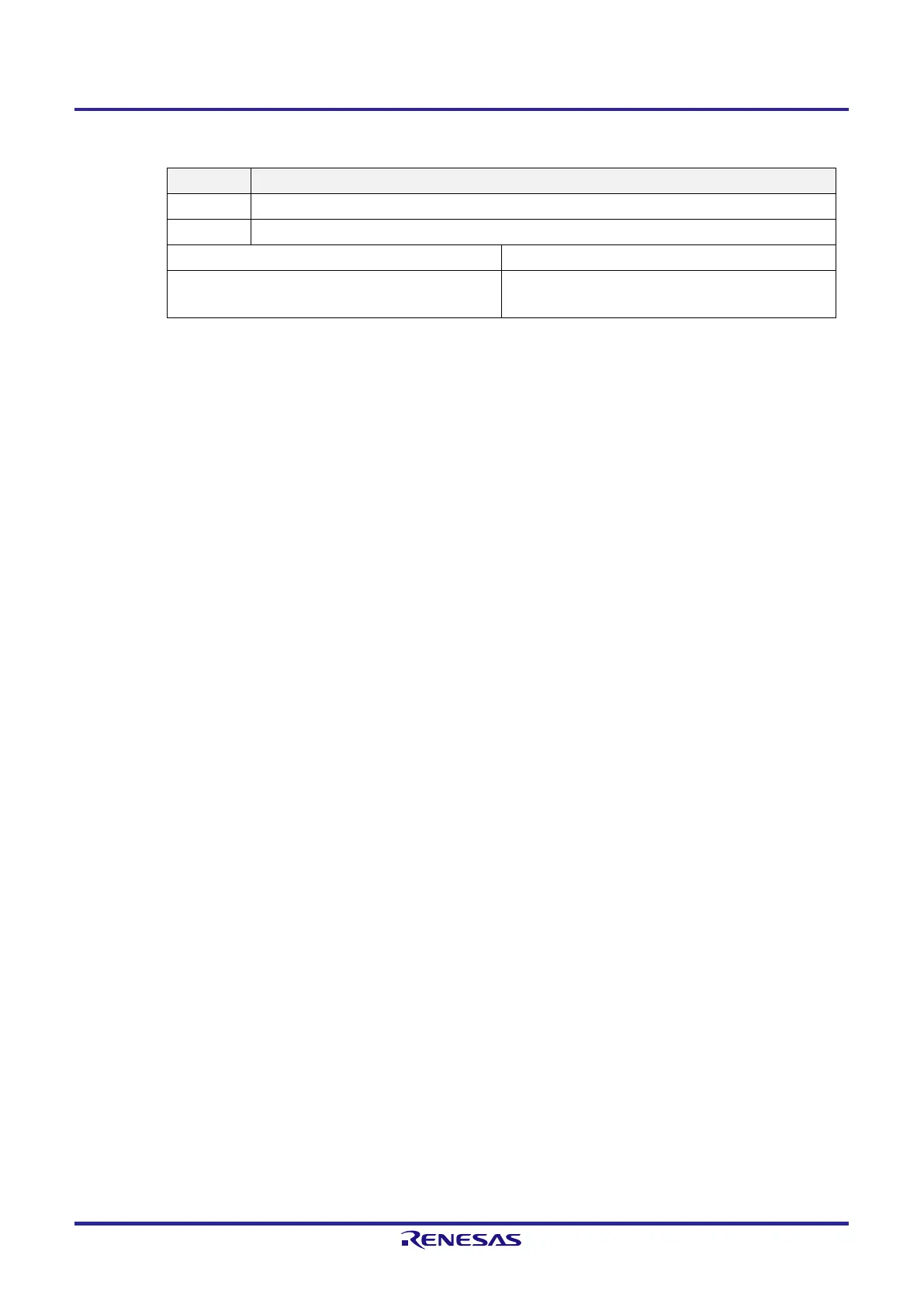

Figure 13-8. Format of IICA Flag Register 0 (IICF0) (2/2)

IICRSV0 Communication reservation function disable bit

0 Enable communication reservation.

1 Disable communication reservation.

Condition for clearing (IICRSV0 = 0) Condition for setting (IICRSV0 = 1)

●

Cleared by instruction

●

Reset

●

Set by instruction

Note 1. Bits 7 and 6 are read-only.

Caution 1. Write to the STCEN0 bit only when the operation is stopped (IICE0 = 0).

Caution 2. When STCEN0 = 1, the bus released state (IICBSY0 = 0) is recognized regardless of the actual bus

state. Therefore, when generating a first start condition (STT0 = 1), it is necessary to verify that

third party communications are not being conducted in order to prevent other communications

from being destroyed.

Caution 3. Write to the IICRSV0 bit only when the operation is stopped (IICE0 = 0).

Remark STT0: Bit 1 of IICA control register 00 (IICCTL00)

IICE0: Bit 7 of IICA control register 00 (IICCTL00)

Loading...

Loading...