RL78/G15 CHAPTER 13 SERIAL INTERFACE IICA

R01UH0959EJ0110 Rev.1.10 Page 557 of 765

Mar 7, 2023

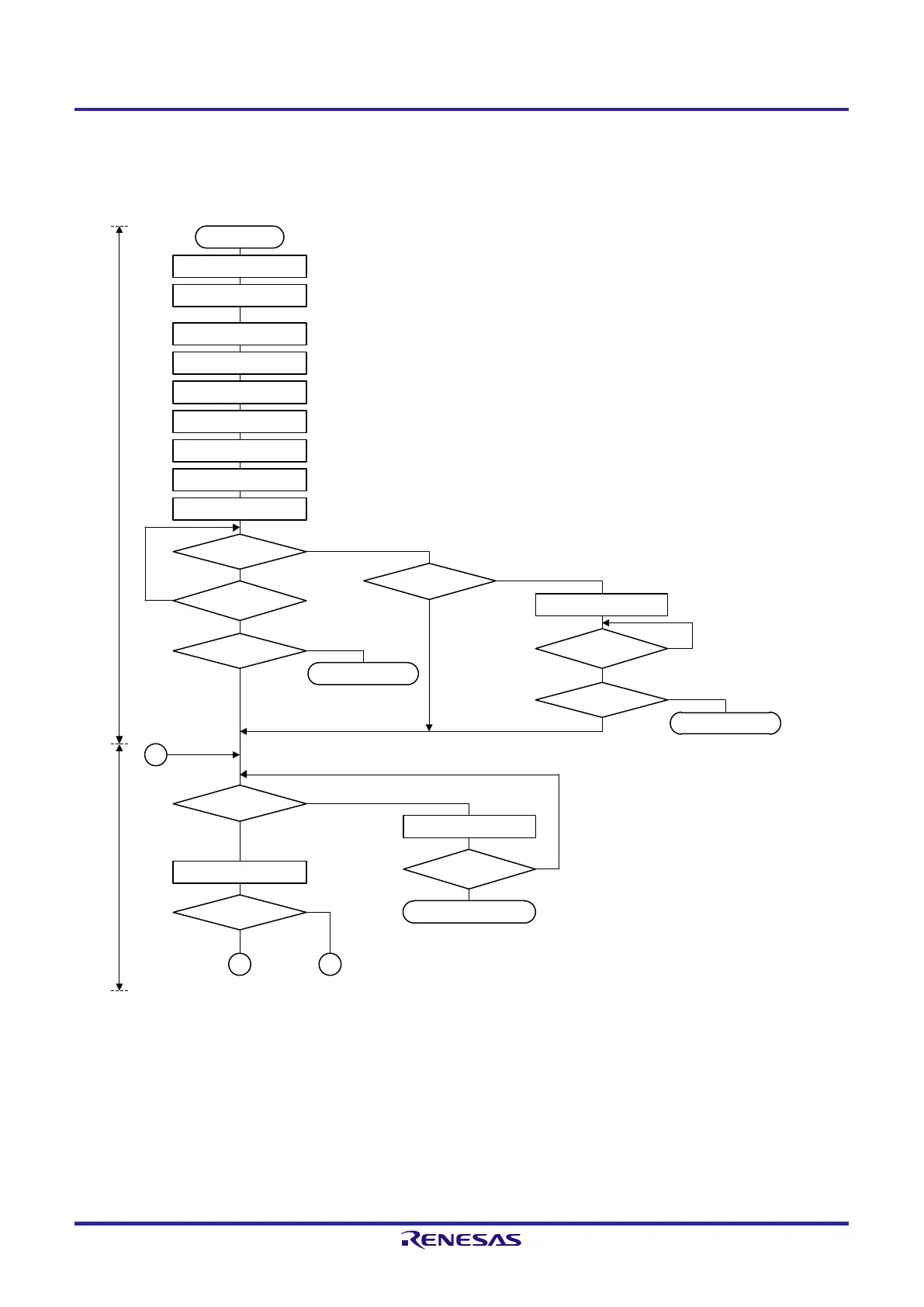

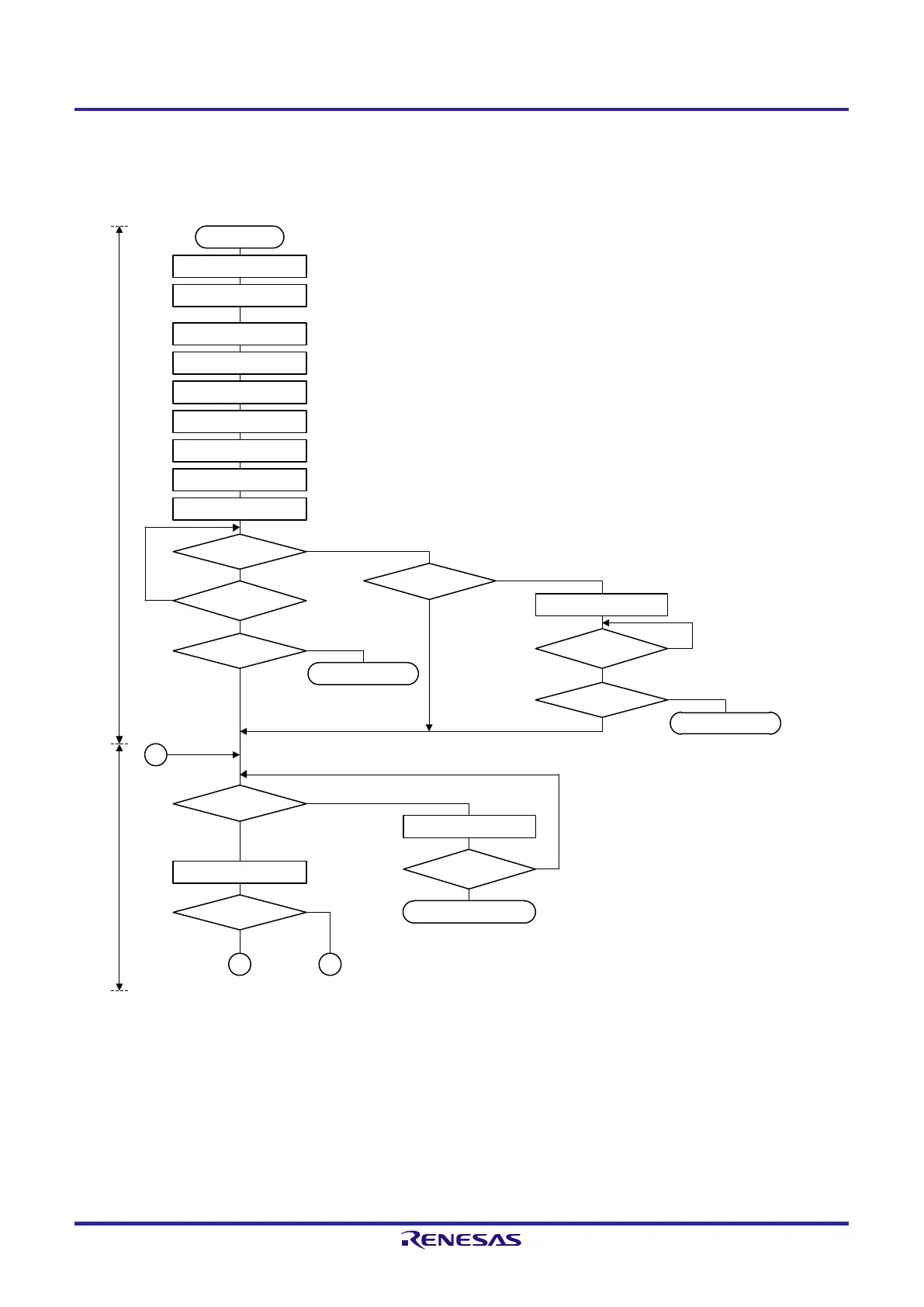

(2) Master operation in multi-master system

Figure 13-28. Master operation in Multi-master System (1/3)

Release serial interface IICA0 from the reset state

and start clock supply.

START

Set the PER0 register

Set the port

IICWL0, IICWH0 ← xxH

SVA0 ← xxH

IICF0 ← 0xH

Set STCEN0 and IICRSV0

Set IICCTL01

IICCTL00 ← 0xx111xxB

ACKE0 = WTIM0 = SPIE0 = 1

IICCTL00 ← 1xx111xxB

IICE0 = 1

Set the port

INTIICA0 interrupt

occurred?

SPD0 = 1?

Start master operation?

IICRSV0 = 0?

Setting of the port multiplexed with the pin to be used

First, set the port to input mode and the output latch to 0

(see 13.3.8 Registers controlling port functions of IICA serial input/output pins).

Set the transfer clock

Set the local address

Set the start condition

Set the port from input mode to output mode and enable the output of the I

2

C bus

(see 13.3.8 Registers controlling port functions of IICA serial input/output pins).

Yes

INTIICA0 interrupt

occurred?

Yes

No

No

SPIE0 = 0

SPT0 = 1

Wait for communication Initial settings

The bus state is

being checked

Check the bus state

Note 1

STCEN0 = 1?

The bus is released for

a certain period

SPD0 = 1?

Yes

No

Slave operation

INTIICA0 interrupt

occurred?

Yes

Yes

No

Slave operation

Wait for detection of the stop

condition

Prepare for starting communication

(generate a stop condition)

Wait for specification of the slave by the other master

Wait for a communication start request (user program dependent)

No

(No communication

start request)

Yes

(Communication start request)

Slave operation

SPIE0 = 1

No

A B

Yes

Enable

communication

reservation

Disable

communication

reservation

No

Wait for a communication request

Yes

No

1

Note 1. Confirm that the bus is released (CLD0 bit = 1, DAD0 bit = 1) for a certain period (for example, for a period of

one frame). If the SDAA0 pin is constantly at the low level, decide whether to release the I

2

C bus (SCLA0 and

SDAA0 pins = high level) in conformance with the specifications of the product that is communicating.

Loading...

Loading...