RL78/G15 CHAPTER 13 SERIAL INTERFACE IICA

R01UH0959EJ0110 Rev.1.10 Page 558 of 765

Mar 7, 2023

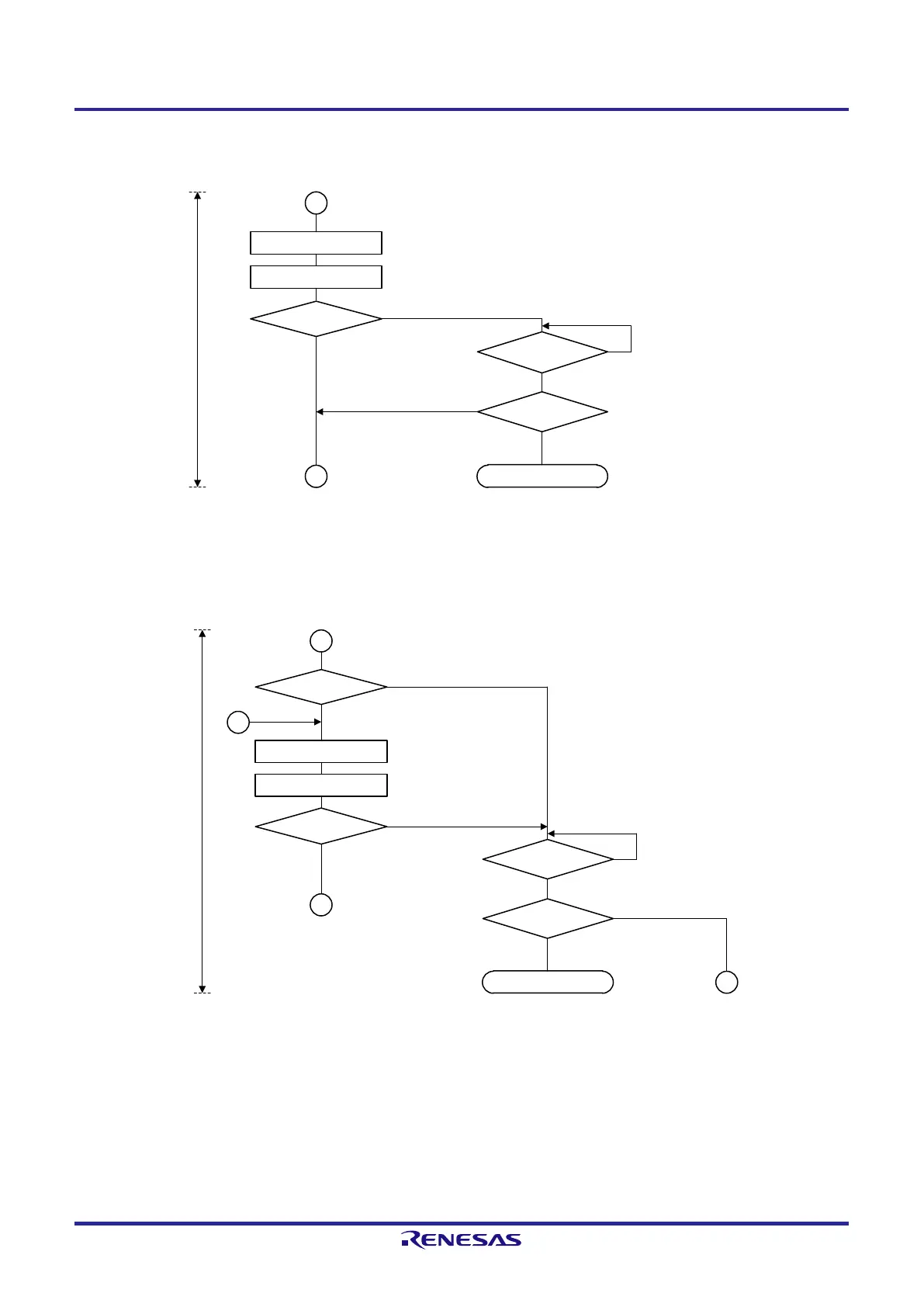

Figure 13-28. Master Operation in Multi-master System (2/3)

INTIICA0 interrupt

occurred?

Yes

Communication processing

MSTS0

=

1

?

Yes

No

Slave operation

STT0

=

1

A

Enable communication reservation

No

Wait for bus release

(communication being reserved)

Wait

EXC0 = 1 or COI0 = 1?

Prepare for starting communication

(generate a start condition)

Secure the wait time

Note 1

by software

C

After the stop condition was detected,

the wait state is entered following the

generation of a start condition by the

communication reservation

Yes

Note 1. A wait time is as follows.

(IICWL0 setting value + IICWH0 setting value + 4)/f

CLK

+ t

F

× 2

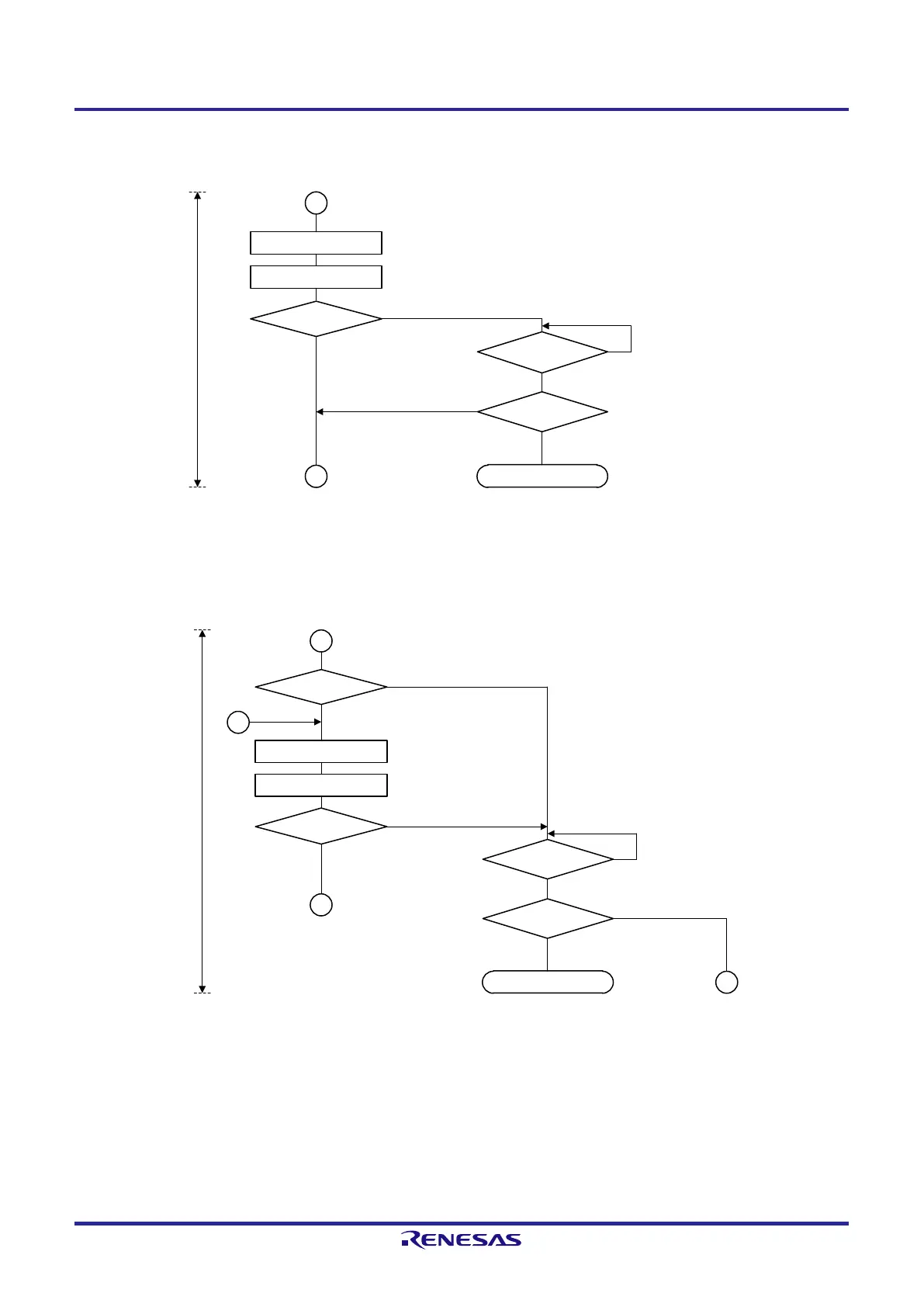

INTIICA0 interrupt

occurred?

Yes

Communication processing

STCF0

= 0?

Yes

No

Slave operation

STT0 = 1

B

Disable communication reservation

No

Wait for bus release

Wait

EXC0 = 1 or COI0 = 1?

Prepare for starting communication

(generate a start condition)

Wait for 5 clock cycles of f

CLK

C

Yes

IICBSY0 = 0?

D

Yes

No

Detect the stop condition

No

D

Remark IICWL0: IICA low-level width setting register 0

IICWH0: IICA high-level width setting register 0

t

F

: SDAA0 and SCLA0 signal falling time

f

CLK

: CPU/peripheral hardware clock frequency

Loading...

Loading...