RL78/G15 CHAPTER 16 RESET FUNCTION

R01UH0959EJ0110 Rev.1.10 Page 638 of 765

Mar 7, 2023

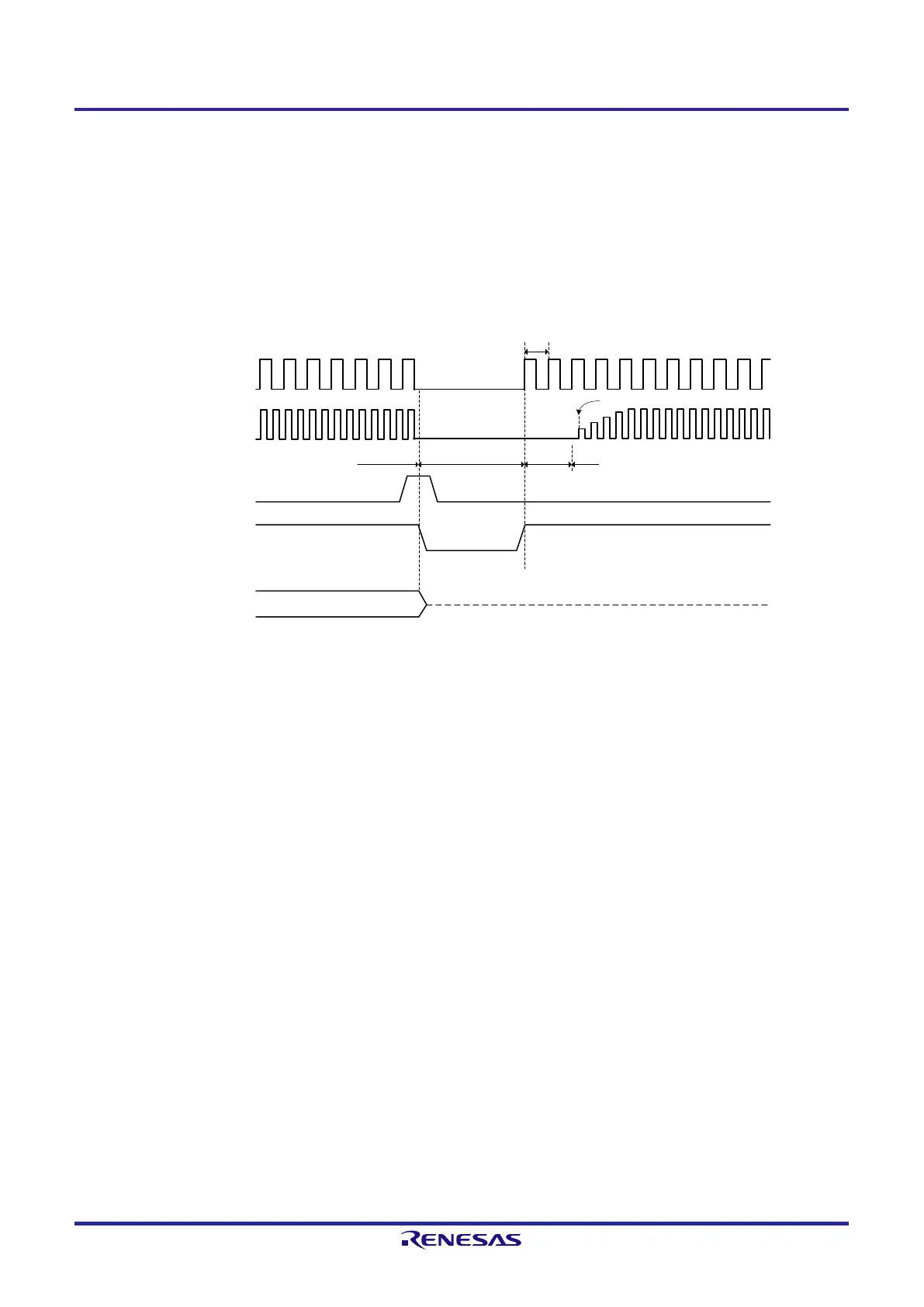

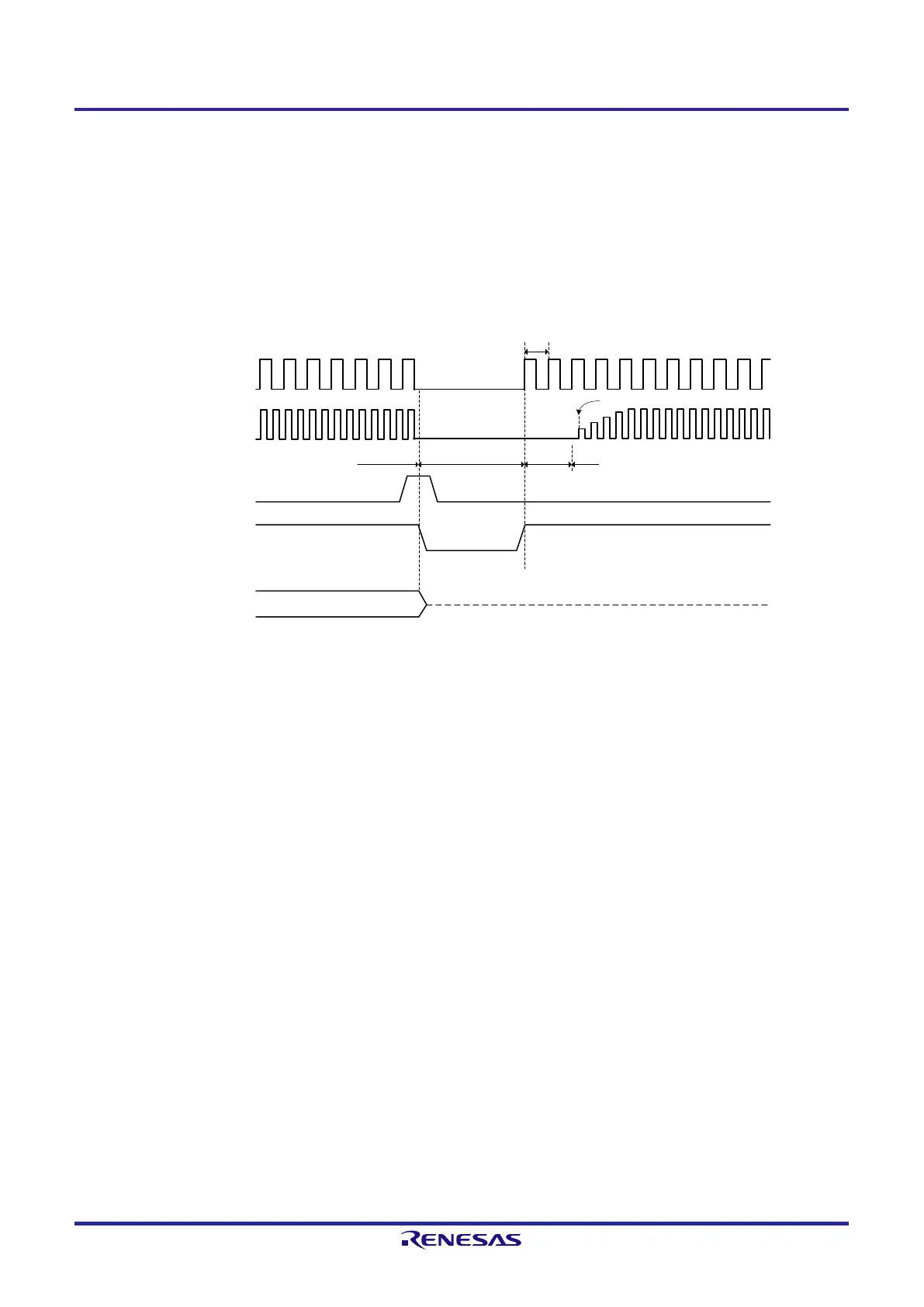

Release from the reset state is automatic in the case of a reset due to a watchdog timer overflow, execution of an illegal

instruction, or detection of illegal memory access. After reset processing, execution of the program with the high-speed

on-chip oscillator clock as the operating clock starts.

Figure 16-3. Timing of Reset Due to Watchdog Timer Overflow, Execution of Illegal Instruction, or Detection of Illegal

Memory Access

Normal operation

Hi-Z

Note 2

Normal operation (high-speed on-chip oscillator clock)

Wait for oscillation

accuracy stabilization

Reset

processing

50 µs (typ.)

High-speed on-chip

oscillator clock

High-speed system clock

(when X1 oscillation is

selected)

Note 1

CPU status

Execution of illegal instruction/

Watchdog timer overflow/

Detection of illegal memory access

________________

Internal reset signal

Port pin

Starting X1 oscillation is specified by software

Reset period

(oscillation stop)

Note 1. 16-pin and 20-pin products only.

Note 2. Statuses of port pins P40 and P125 pins are as follows.

High level during reset period or after receiving a reset (connected to the internal pull-up resistor).

Remark For the reset timing due to the voltage detection by the selectable power-on-reset (SPOR) circuit, see

CHAPTER 17 SELECTABLE POWER-ON-RESET CIRCUIT.

Loading...

Loading...