RL78/G15 CHAPTER 22 INSTRUCTION SET

R01UH0959EJ0110 Rev.1.10 Page 701 of 765

Mar 7, 2023

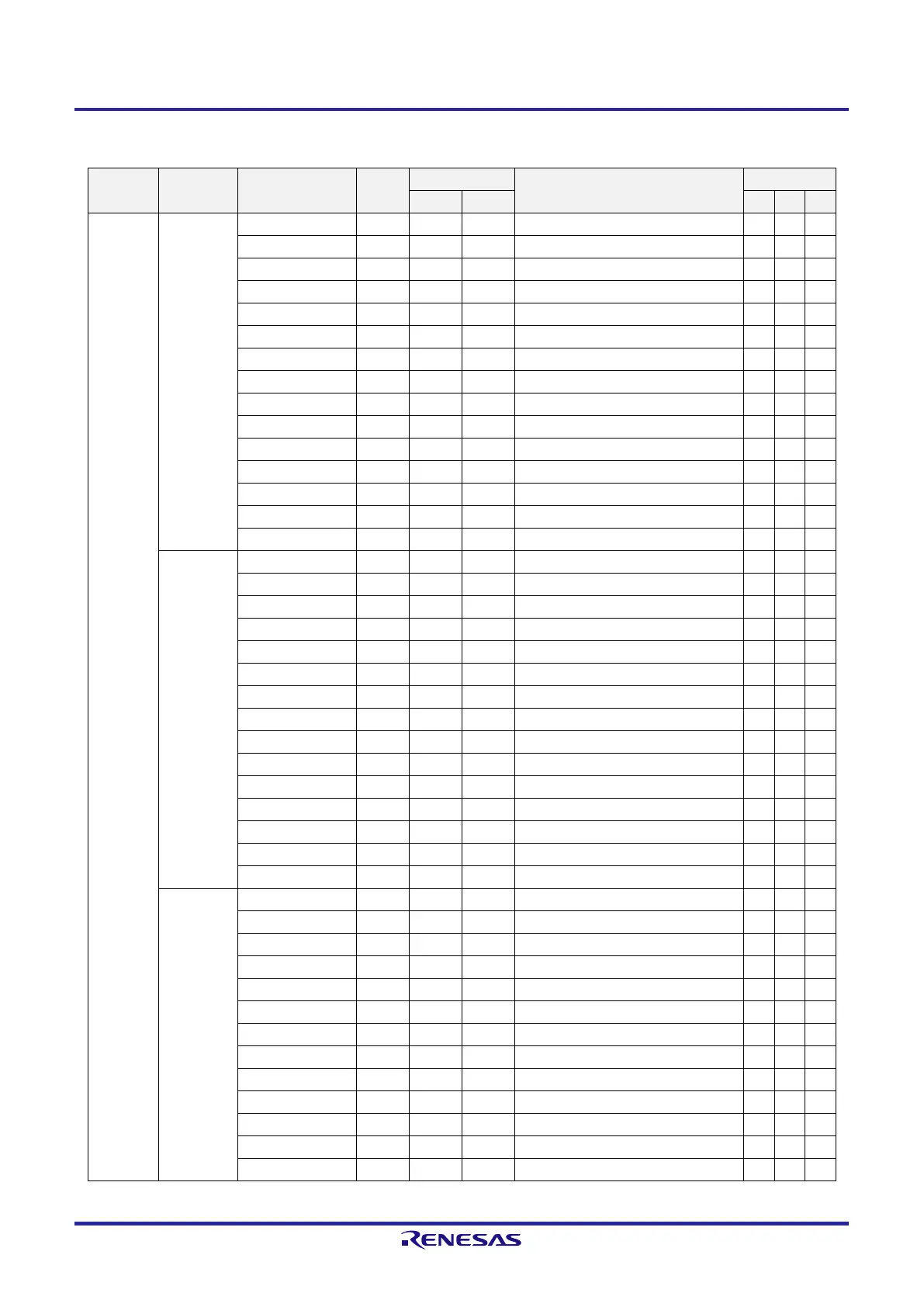

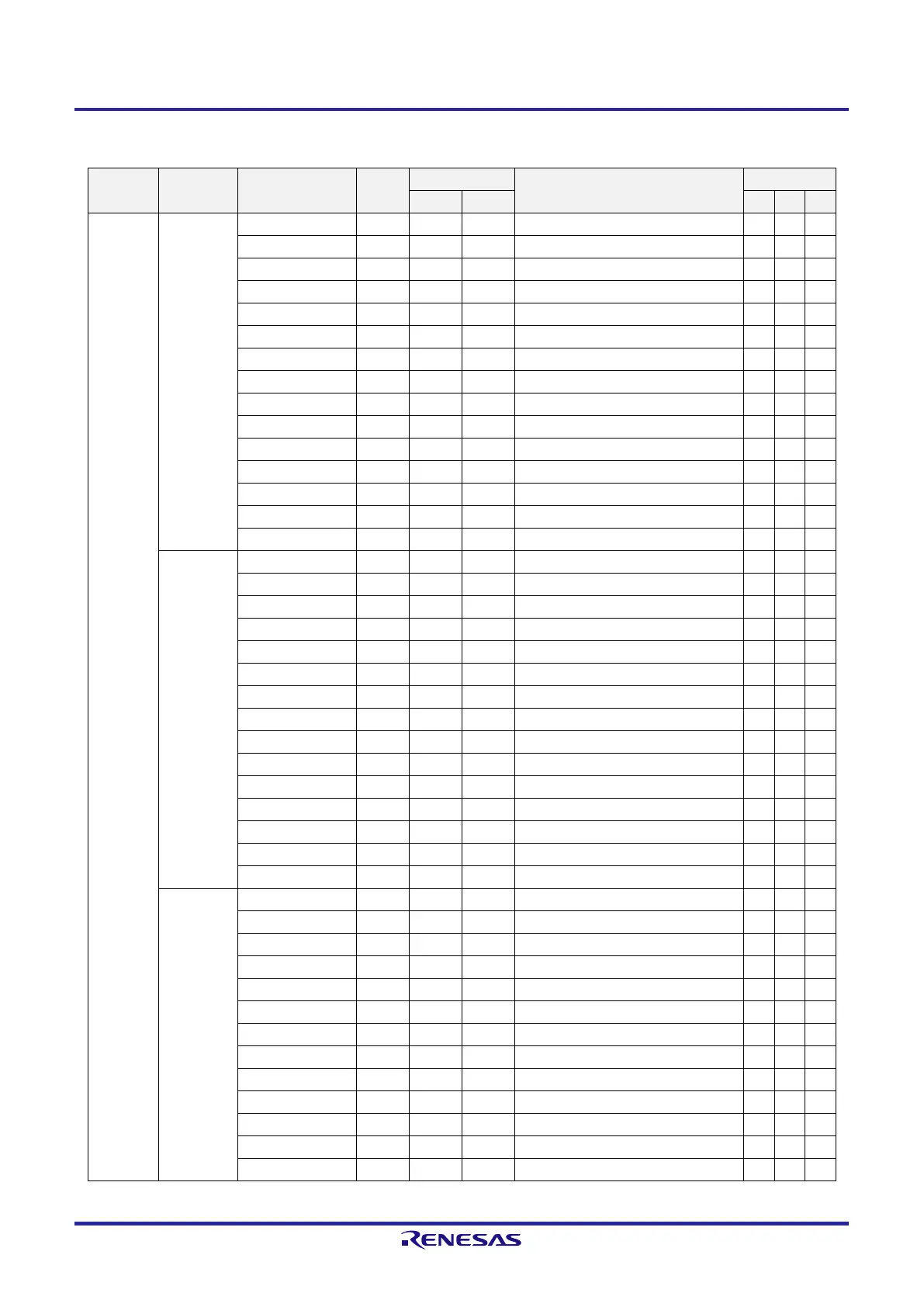

Table 22-5. Operation List (6/13)

Instruction

Group

Mnemonic Operand Bytes Clock Operation Flag

Note 1 Note 2

Z AC CY

8-bit

operation

SUB A, #byte 2 1 — A, CY ← A − byte × × ×

saddr, #byte 3 2 — (saddr), CY ← (saddr) − byte × × ×

A, r

Note 3

2 1 — A, CY ← A − r × × ×

r, A 2 1 — r, CY ← r − A × × ×

A, !addr16 3 1 4 A, CY ← A − (addr16) × × ×

A, ES:!addr16 4 2 5 A, CY ← A − (ES, addr16) × × ×

A, saddr 2 1 — A, CY ← A − (saddr) × × ×

A, [HL] 1 1 4 A, CY ← A − (HL) × × ×

A, ES:[HL] 2 2 5 A, CY ← A − (ES, HL) × × ×

A, [HL+byte] 2 1 4 A, CY ← A − (HL + byte) × × ×

A, ES:[HL+byte] 3 2 5 A, CY ← A − ((ES, HL) + byte) × × ×

A, [HL+B] 2 1 4 A, CY ← A − (HL + B) × × ×

A, ES:[HL+B] 3 2 5 A, CY ← A − ((ES, HL) + B) × × ×

A, [HL+C] 2 1 4 A, CY ← A − (HL + C) × × ×

A, ES:[HL+C] 3 2 5 A, CY ← A − ((ES, HL) + C) × × ×

SUBC A, #byte 2 1 — A, CY ← A − byte − CY × × ×

saddr, #byte 3 2 — (saddr), CY ← (saddr) − byte − CY × × ×

A, r

Note 3

2 1 — A, CY ← A − r − CY × × ×

r, A 2 1 — r, CY ← r − A − CY × × ×

A, !addr16 3 1 4 A, CY ← A − (addr16) − CY × × ×

A, ES:!addr16 4 2 5 A, CY ← A − (ES, addr16) − CY × × ×

A, saddr 2 1 — A, CY ← A − (saddr) − CY × × ×

A, [HL] 1 1 4 A, CY ← A − (HL) − CY × × ×

A, ES:[HL] 2 2 5 A, CY ← A − (ES, HL) − CY × × ×

A, [HL+byte] 2 1 4 A, CY ← A − (HL + byte) − CY × × ×

A, ES:[HL+byte] 3 2 5 A, CY ← A − ((ES, HL) + byte) − CY × × ×

A, [HL+B] 2 1 4 A, CY ← A − (HL + B) − CY × × ×

A, ES:[HL+B] 3 2 5 A, CY ← A − ((ES, HL) + B) − CY × × ×

A, [HL+C] 2 1 4 A, CY ← A − (HL + C) − CY × × ×

A, ES:[HL+C] 3 2 5 A, CY ← A − ((ES:HL) + C) − CY × × ×

AND A, #byte 2 1 — A ← A ∧ byte ×

saddr, #byte 3 2 — (saddr) ← (saddr) ∧ byte ×

A, r

Note 3

2 1 — A ← A ∧ r ×

r, A 2 1 — r ← r ∧ A ×

A, !addr16 3 1 4 A ← A ∧ (addr16) ×

A, ES:!addr16 4 2 5 A ← A ∧ (ES:addr16) ×

A, saddr 2 1 — A ← A ∧ (saddr) ×

A, [HL] 1 1 4 A ← A ∧ (HL) ×

A, ES:[HL] 2 2 5 A ← A ∧ (ES:HL) ×

A, [HL+byte] 2 1 4 A ← A ∧ (HL + byte) ×

A, ES:[HL+byte] 3 2 5 A ← A ∧ ((ES:HL) + byte) ×

A, [HL+B] 2 1 4 A ← A ∧ (HL + B) ×

A, ES:[HL+B] 3 2 5 A ← A ∧ ((ES:HL) + B) ×

Loading...

Loading...