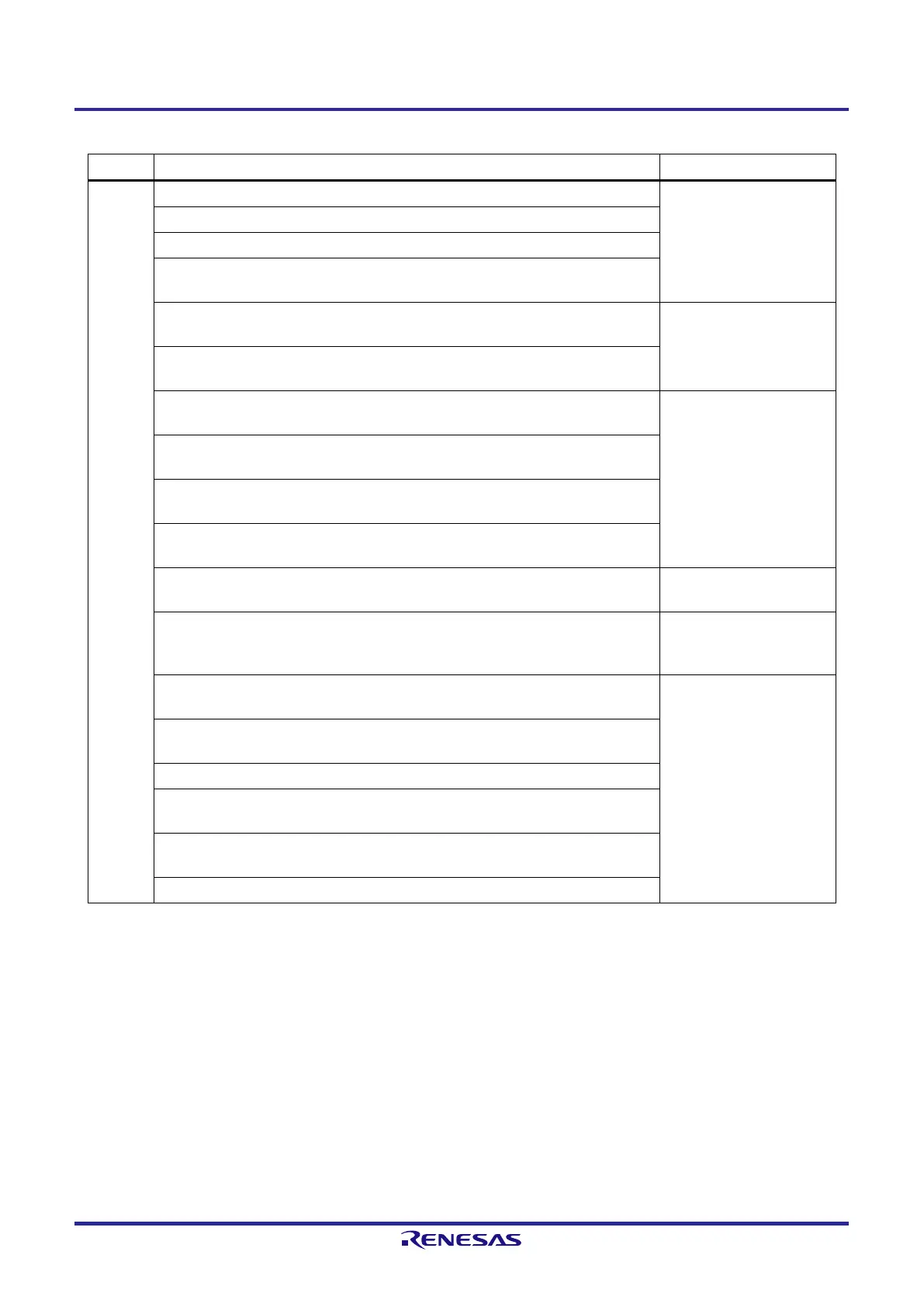

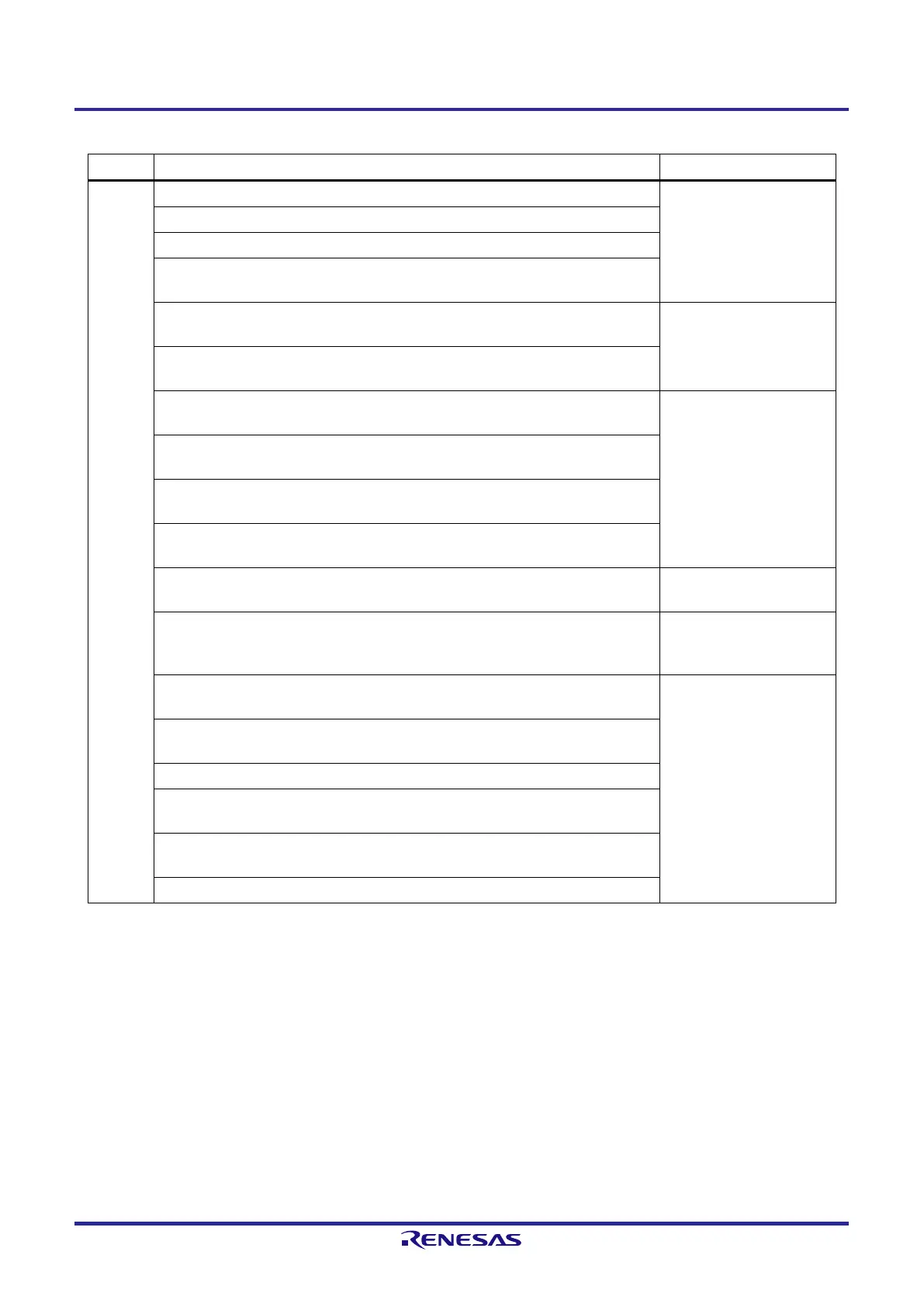

RL78/G15 APPENDIX A REVISION HISTORY

R01UH0959EJ0110 Rev.1.10 Page 762 of 765

Mar 7, 2023

(3/4)

Edition Description Chapter

Rev.1.00 13.5.14 Communication reservation: The description in (1) for the wait time, modified

CHAPTER 13 SERIAL

INTERFACE IICA

Figure 13-26. Communication Reservation Procedure: Note 1, modified

Figure 13-28. Master Operation in Multi-master System (2/3): Note 1, modified

Figure 13-29. Slave Operation Procedure (1): The processing in “Clear the

communication mode flag WREL0 = 1”, modified

Table 14-1. Interrupt Source List: Default Priority 0, 9, 10, 16 to 19, 21 to 24, modified.

Note 4, added.

CHAPTER 14 INTERRUPT

FUNCTIONS

Table 14-2. Flags Corresponding to Interrupt Request Sources (2/2): Targets of 16-pin to

8-pin, changed

15.1 Overview, 1) HALT mode: The description, modified

CHAPTER 15 STANDBY

FUNCTION

Figure 15-3. STOP Mode Release by Interrupt Request Generation (1/3): Note 2,

modified

Figure 15-3. STOP Mode Release by Interrupt Request Generation (2/3): Note 2,

modified

Figure 15-3. STOP Mode Release by Interrupt Request Generation (3/3): Note 2,

modified

Figure 16-2. Timing of Reset by RESET

¯¯¯¯¯¯

Input: Note 2, modified

CHAPTER 16 RESET

FUNCTION

Figure 17-2. Timing of Internal Reset Signal Generation: SPOR reset processing time,

modified

CHAPTER 17 SELECTABLE

POWER-ON-RESET

CIRCUIT

Figure 19-2. Communication with Dedicated Flash Memory Programmer: Note (Note 1),

added to EMV

DD

CHAPTER 19 FLASH

MEMORY

19.2 Writing to Flash Memory by Using External Device (that Incorporates UART): The

description, modified

Table 19-7. Flash Memory Control Commands: Writing after erasure, added

Figure 19-8. Format of Flash Address Pointer Registers H and L (FLAPH, FLAPL): The

bit name of the FLAPL register, modified

Figure 19-14. Format of Flash Memory Sequencer Status Registers H and L (FSASTH,

FSASTL): <Clearing condition> for the WRER and ERER bits, modified

19.6.3 Notes on self-programming: The description in (5), modified

Loading...

Loading...