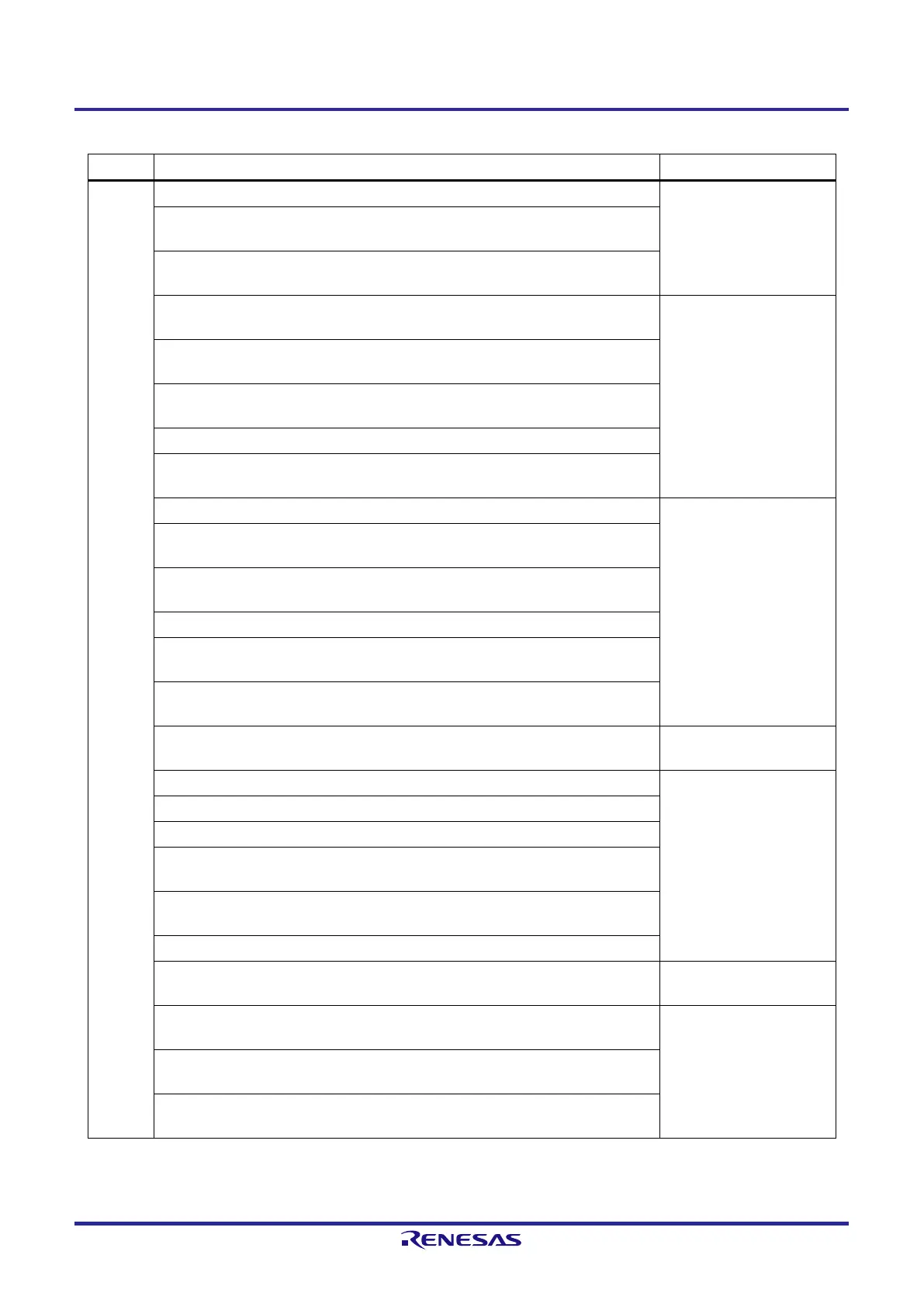

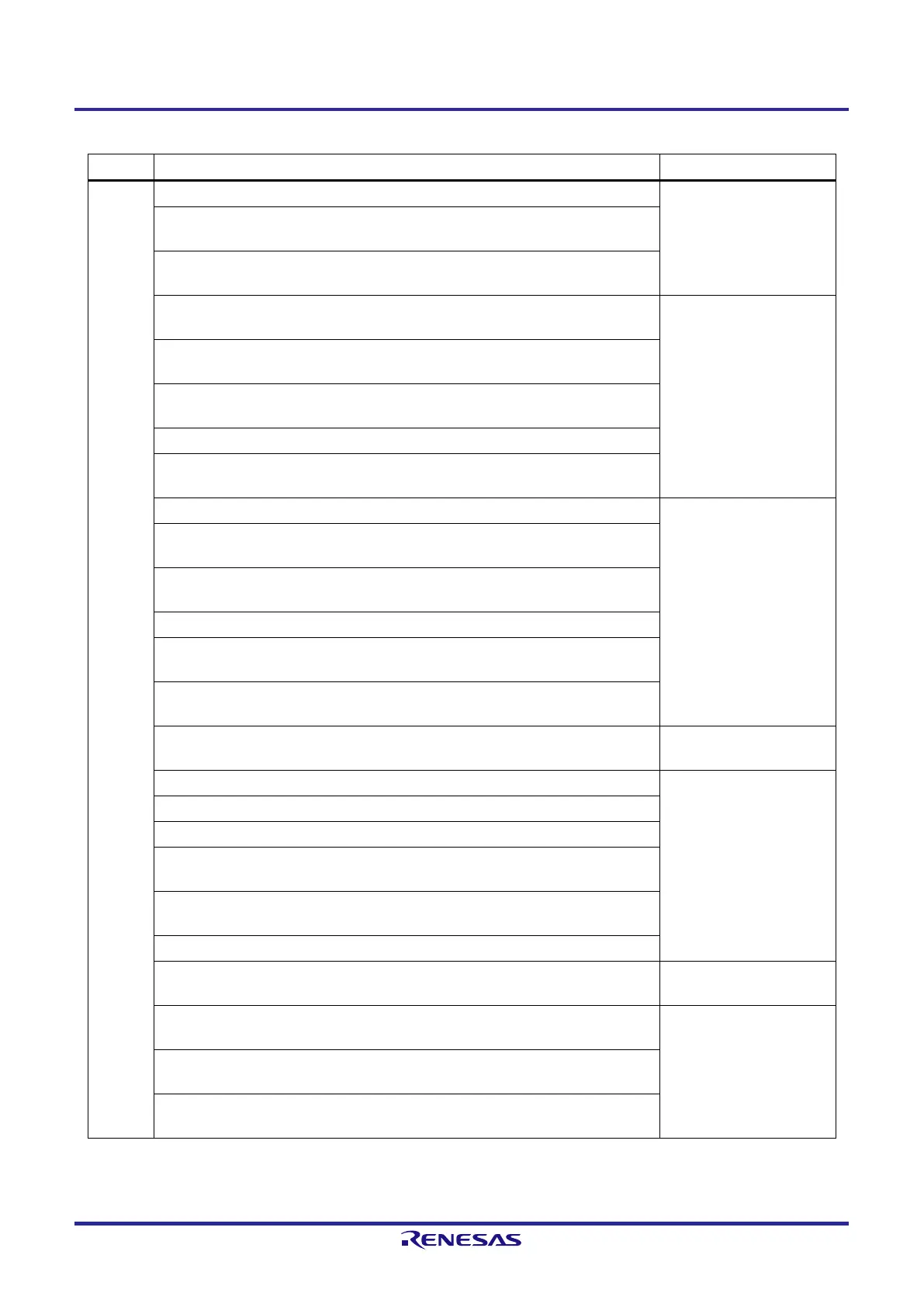

RL78/G15 APPENDIX A REVISION HISTORY

R01UH0959EJ0110 Rev.1.10 Page 761 of 765

Mar 7, 2023

(2/4)

Edition Description Chapter

Rev.1.00 4.5.1 Basic concept when using alternate function: The description, modified

CHAPTER 4 PORT

FUNCTIONS

Table 4-7. Setting Examples of Registers and Output Latches When Using Pin Function

(3/10): POMp setting for (TxD0) and TxD0, modified

Table 4-7. Setting Examples of Registers and Output Latches When Using Pin Function

(4/10): POMp setting for (TxD0), modified

5.3 Registers Controlling Clock Generator, 1) 8-pin and 10-pin products: High-speed on-

chip oscillator trimming register (HIOTRM), added

CHAPTER 5 CLOCK

GENERATOR

Figure 5-2. Format of Clock Operation Mode Control Register (CMC): The description of

setting 1 of the AMPH bit, modified

Table 5-2. Conditions Before Clock Oscillation Is Stopped and Flag Settings: The table

title, modified

5.3.5 Oscillation stabilization time select register (OSTS): The description, modified

Figure 5-12. Examples of Incorrect Resonator Connection (2/2): The figure in (g) Signals

are fetched, modified

Independent channel operation function: Note 1, modified

CHAPTER 6 TIMER ARRAY

UNIT

6.1.1 Independent channel operation function, 1) Interval timer to 6) Measurement of

high-/low-level width of input signal: Remark 1 and Remark 2, added

6.1.1 Independent channel operation function, 4) Divider function (channels 0 and 3 only):

Channel 3, added. The channel number, changed to index (n).

Figure 6-20. Format of Input Switch Control Register (ISC): RXD0 → RxD0, modified

6.8.3 Operation as frequency divider (channels 0 and 3 only): Channel 3, added. The

channel number, changed to index (n). Remark, added.

Figure 6-50. Example of Set Contents of Registers During Operation as Frequency

Divider (1/2): Setting of SPLIT0n bit (channel 3), added. Note 1, added.

9.4.1 Controlling operation of watchdog timer, <1> When the watchdog timer is used, its

operation is specified by the option byte (000C0H): The description, modified

CHAPTER 9 WATCHDOG

TIMER

Figure 10-3. Format of A/D Converter Mode Register 0 (ADM0): Note 2, modified

CHAPTER 10 A/D

CONVERTER

Figure 10-4. Timing Chart when A/D Voltage Comparator Is Used: Note 1, modified

10.6 A/D Converter Operation Modes: The description in <2>, modified

Figure 10-14. Setting up ANI0 to ANI10 for A/D Conversion: The processing in “Count the

A/D voltage stabilization wait time”, modified

Figure 10-15. Setting up Internal Reference Voltage for A/D Conversion: The processing

in “Count the A/D voltage stabilization wait time”, modified

10.9.8 Conversion results just after A/D conversion start: The description, modified

Figure 11-4. Format of Comparator Filter Control Register (COMPFIR): The description in

Note 6, modified

CHAPTER 11

COMPARATOR

Figure 12-4. Format of Serial Clock Select Register m (SPSm): The operation clock for

f

CLK

/2

5

to f

CLK

/2

10

, modified. The operation clock for f

CLK

/2

13

, modified.

CHAPTER 12 Serial Array

Unit

Figure 12-76. Example of Contents of Registers for UART Reception of UART (UART0)

(2/2): Remark 2, modified

Table 12-3. Selection of Operation Clock For UART: The SPSm register value of the

operation clock for f

CLK

/2

12

to f

CLK

/2

15

, modified

Loading...

Loading...