5–42 Chapter 5: Clock Networks and PLLs in Cyclone IV Devices

Document Revision History

Cyclone IV Device Handbook, October 2012 Altera Corporation

Volume 1

Document Revision History

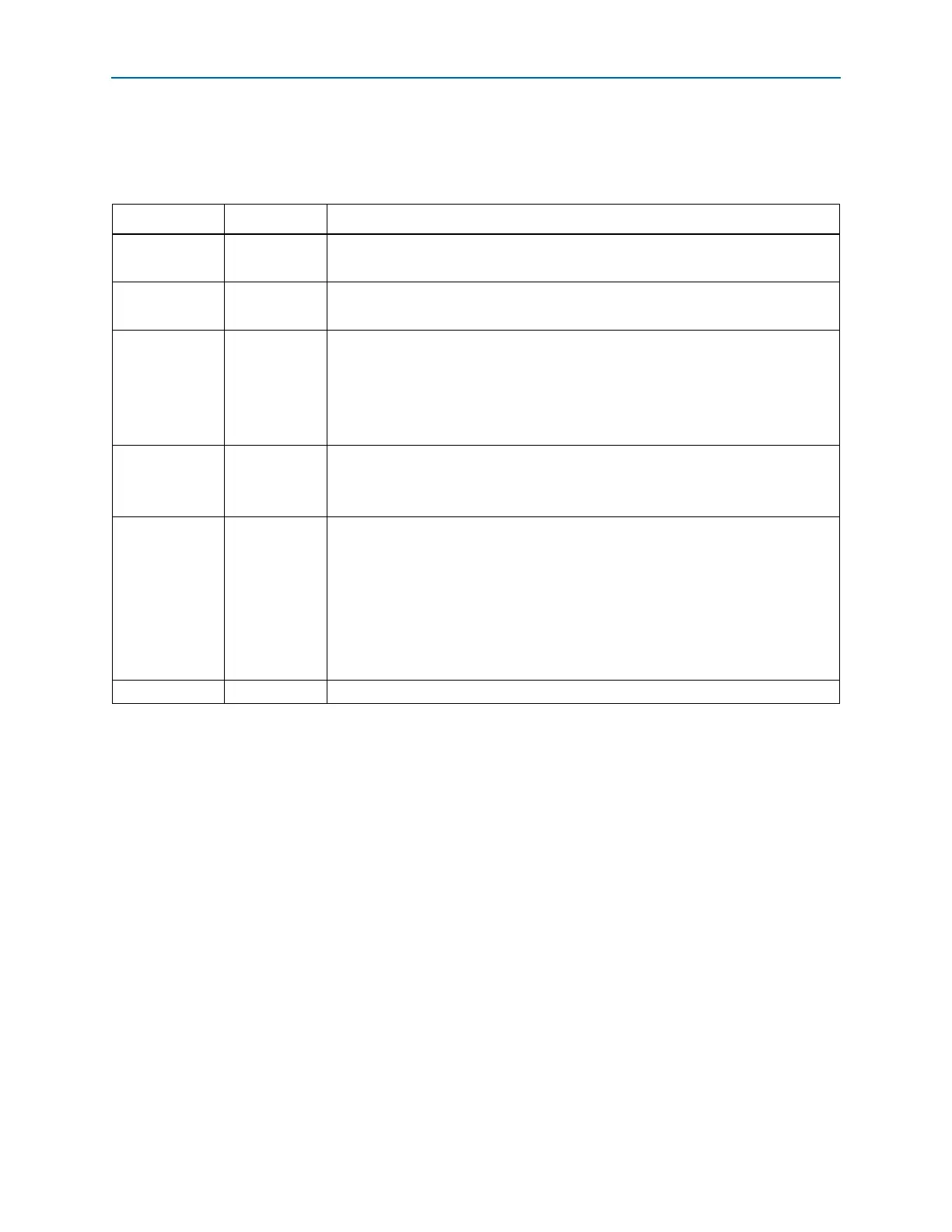

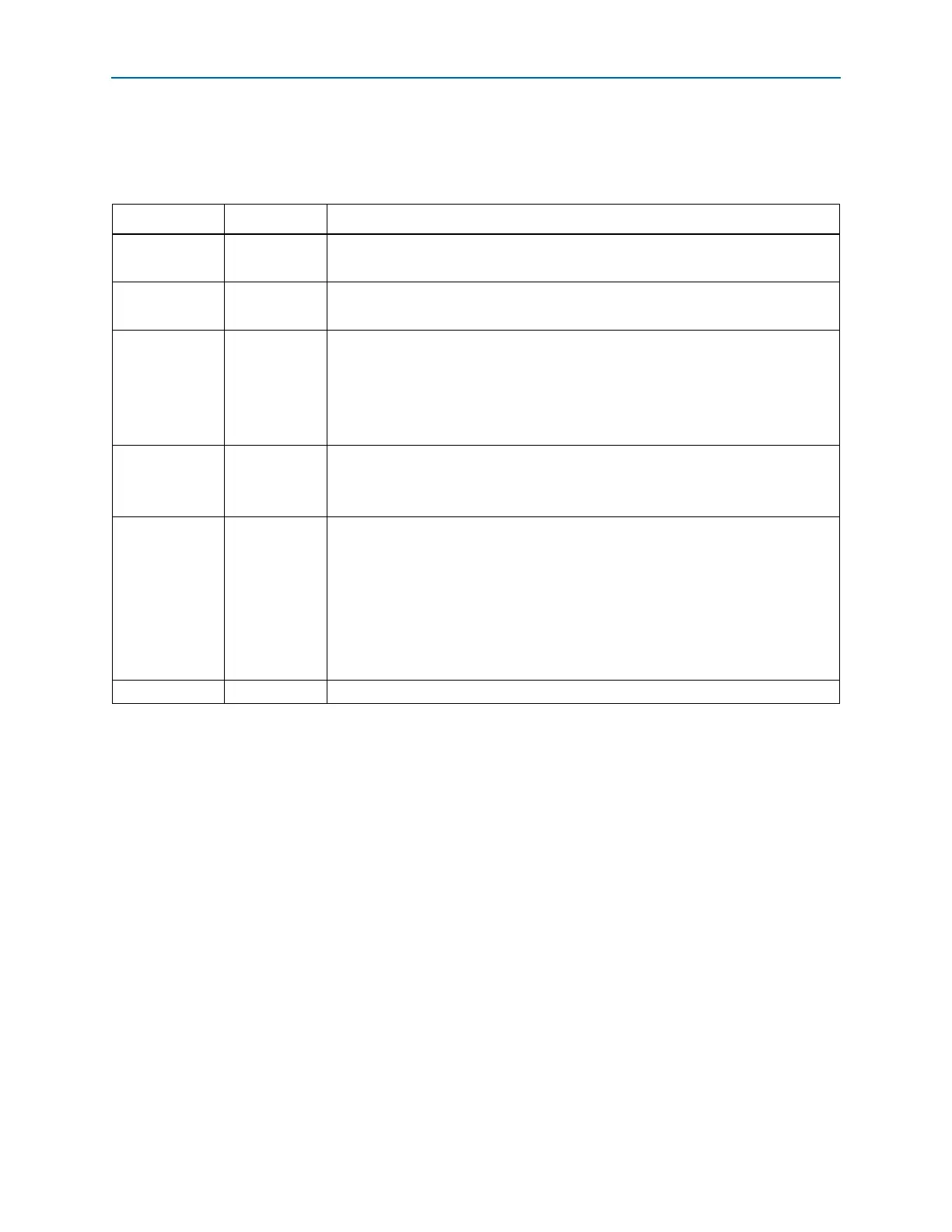

Tab le 5 –1 4 lists the revision history for this chapter.

Table 5–14. Document Revision History

Date Version Changes

October 2012 2.4

■ Updated “Manual Override” and “PLL Cascading” sections.

■ Updated Figure 5–9.

November 2011 2.3

■ Updated the “Dynamic Phase Shifting” section.

■ Updated Figure 5–26.

December 2010 2.2

■ Updated for the Quartus II software version 10.1 release.

■ Updated Figure 5–3 and Figure 5–10.

■ Updated “GCLK Network Clock Source Generation”, “PLLs in Cyclone IV Devices”,

and “Manual Override” sections.

■ Minor text edits.

July 2010 2.1

■ Updated Figure 5–2, Figure 5–3, Figure 5–4, and Figure 5–10.

■ Updated Table 5–1, Table 5–2, and Table 5–5.

■ Updated “Clock Feedback Modes” section.

February 2010 2.0

■ Added Cyclone IV E devices information for the Quartus II software version 9.1 SP1

release.

■ Updated “Clock Networks” section.

■ Updated Table 5–1 and Table 5–2.

■ Added Table 5–3.

■ Updated Figure 5–2, Figure 5–3, and Figure 5–9.

■ Added Figure 5–4 and Figure 5–10.

November 2009 1.0 Initial release.

Loading...

Loading...