Chapter 2: Cyclone IV Reset Control and Power Down 2–19

Dynamic Reconfiguration Reset Sequences

September 2014 Altera Corporation Cyclone IV Device Handbook,

Volume 2

Dynamic Reconfiguration Reset Sequences

When using dynamic reconfiguration in data rate divisions in PLL reconfiguration or

channel reconfiguration mode, use the following reset sequences.

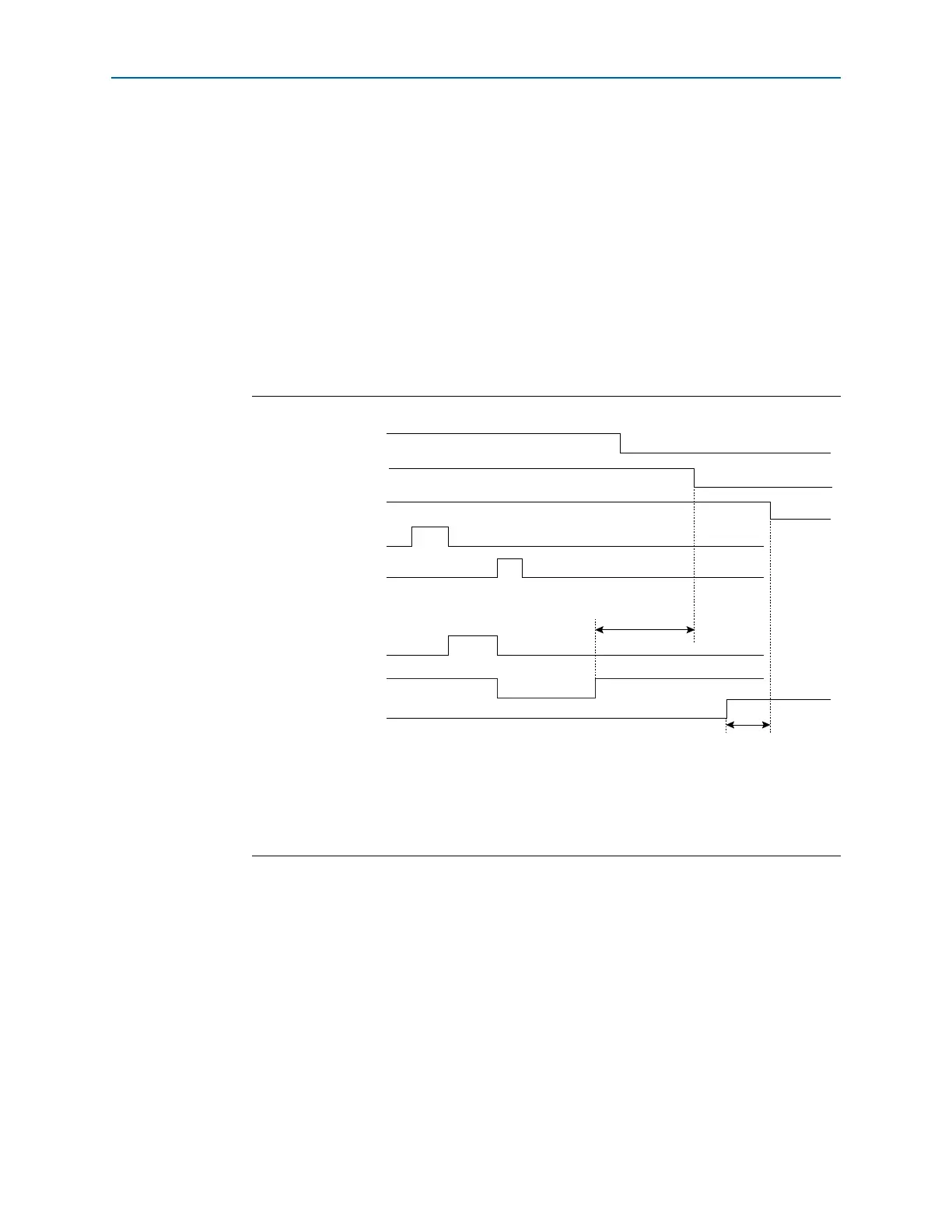

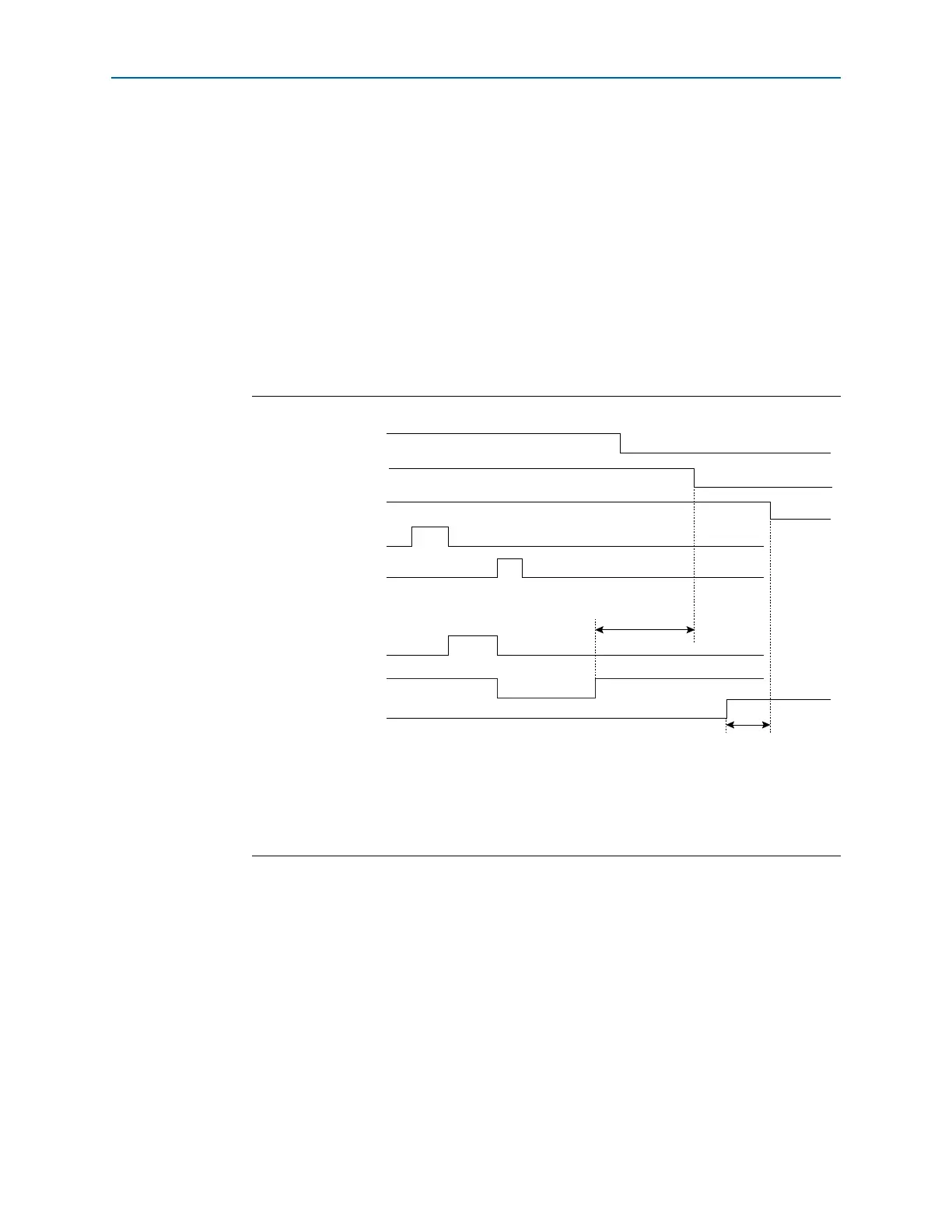

Reset Sequence in PLL Reconfiguration Mode

Use the example reset sequence shown in Figure 2–11 when you use the PLL dynamic

reconfiguration controller to change the data rate of the transceiver channel. In this

example, PLL dynamic reconfiguration is used to dynamically reconfigure the data

rate of the transceiver channel configured in Basic ×1 mode with the receiver CDR in

automatic lock mode.

As shown in Figure 2–11, perform the following reset procedure when using the PLL

dynamic reconfiguration controller to change the configuration of the PLLs in the

transmitter channel:

1. Assert the

tx_digitalreset

,

rx_analogreset

, and

rx_digitalreset

signals. The

pll_configupdate

signal is asserted (marker 1) by the ALTPLL_RECONFIG

megafunction after the final data bit is sent out. The

pll_reconfig_done

signal is

asserted (marker 2) to inform the ALTPLL_RECONFIG megafunction that the scan

chain process is completed. The ALTPLL_RECONFIG megafunction then asserts

the

pll_areset

signal (marker 3) to reset the transceiver PLL.

Figure 2–11. Reset Sequence When Using the PLL Dynamic Reconfiguration Controller to Change

the Data Rate of the Transceiver Channel

Notes to Figure 2–11:

(1) The

pll_configupdate

and

pll_areset

signals are driven by the ALTPLL_RECONFIG megafunction. For more

information, refer to AN 609: Implementing Dynamic Reconfiguration in Cyclone IV GX Devices and the Cyclone IV

Dynamic Reconfiguration chapter.

(2) For t

LTD_Auto

duration, refer to the Cyclone IV Device Datasheet chapter.

Output Status Signals

pll_reconfig_done

5

tx_digitalreset

pll_configupdate (1)

Reset and Control Signals

rx_analogreset

8

rx_digitalreset

pll_locked

3

pll_areset (1)

1

2

6

t

LT D _ Au t o

(2)

4

Five parallel clock cycles

rx_freqlocked

7

Loading...

Loading...