Chapter 3: Memory Blocks in Cyclone IV Devices 3–5

Overview

November 2011 Altera Corporation Cyclone IV Device Handbook,

Volume 1

Address Clock Enable Support

Cyclone IV devices M9K memory blocks support an active-low address clock enable,

which holds the previous address value for as long as the

addressstall

signal is high

(

addressstall

=

'1'

). When you configure M9K memory blocks in dual-port mode,

each port has its own independent address clock enable.

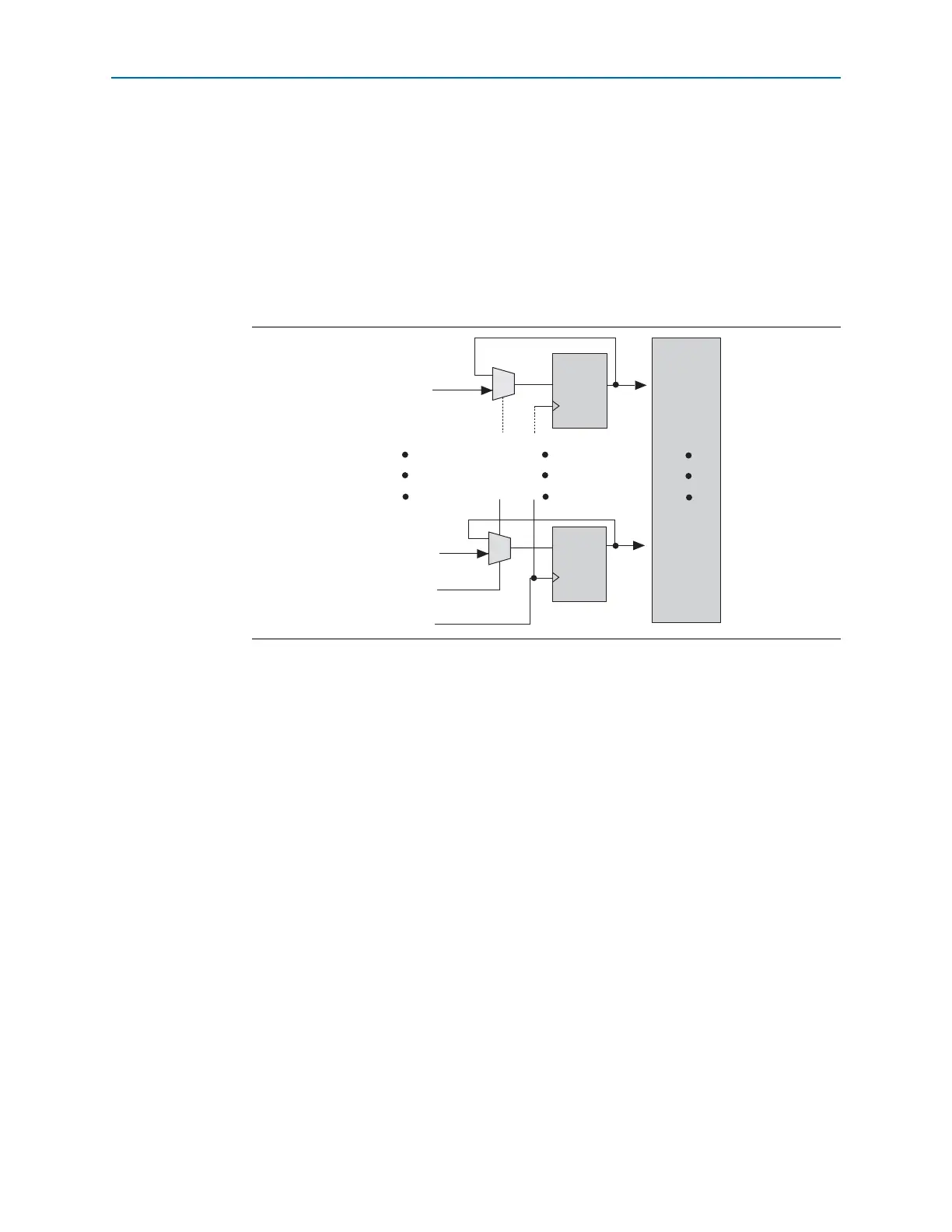

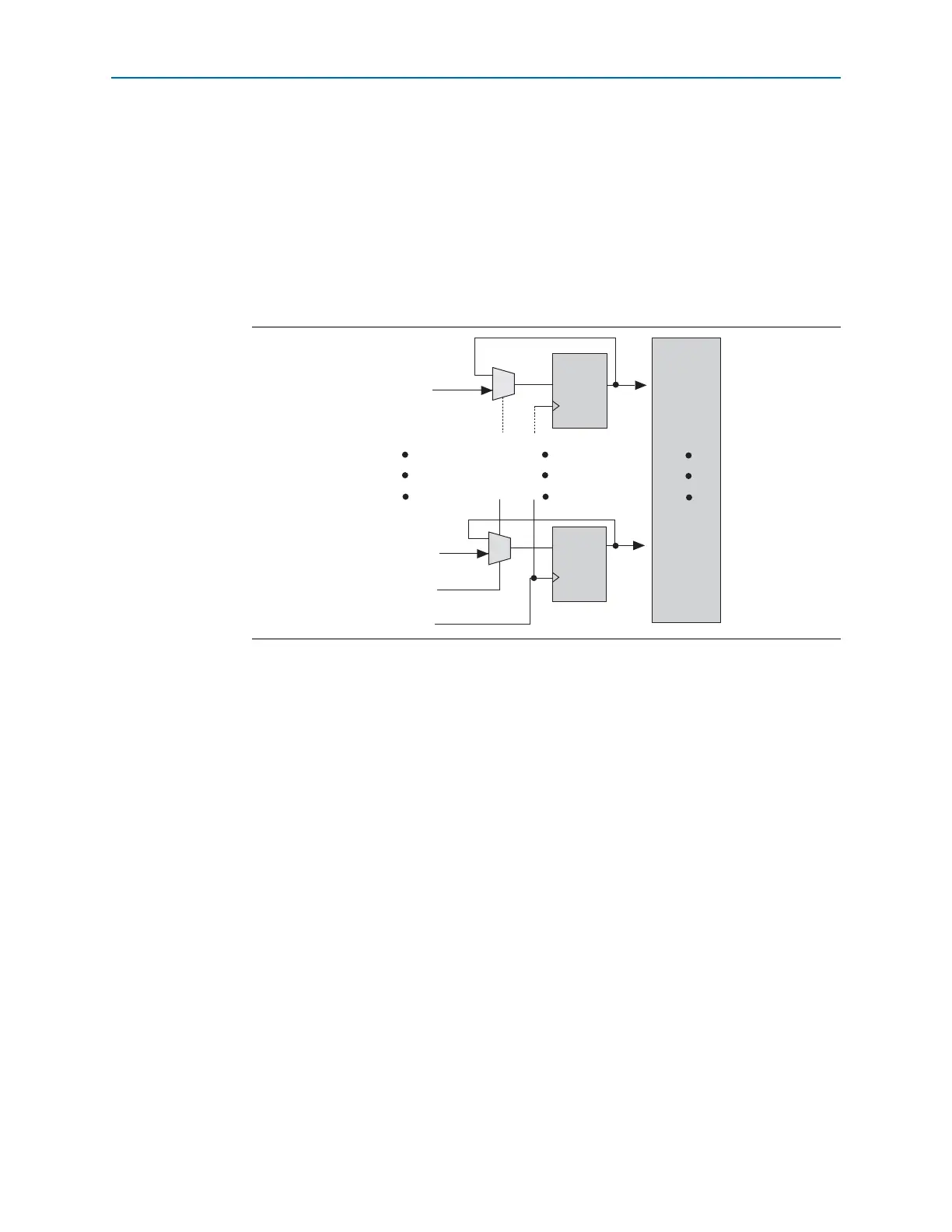

Figure 3–2 shows an address clock enable block diagram. The address register output

feeds back to its input using a multiplexer. The multiplexer output is selected by the

address clock enable (

addressstall

) signal.

The address clock enable is typically used to improve the effectiveness of cache

memory applications during a cache-miss. The default value for the address clock

enable signals is low.

Figure 3–2. Cyclone IV Devices Address Clock Enable Block Diagram

address[0]

address[N]

addressstall

clock

address[0]

register

address[N]

register

address[N]

address[0]

Loading...

Loading...