Chapter 2: Cyclone IV Reset Control and Power Down 2–3

User Reset and Power-Down Signals

September 2014 Altera Corporation Cyclone IV Device Handbook,

Volume 2

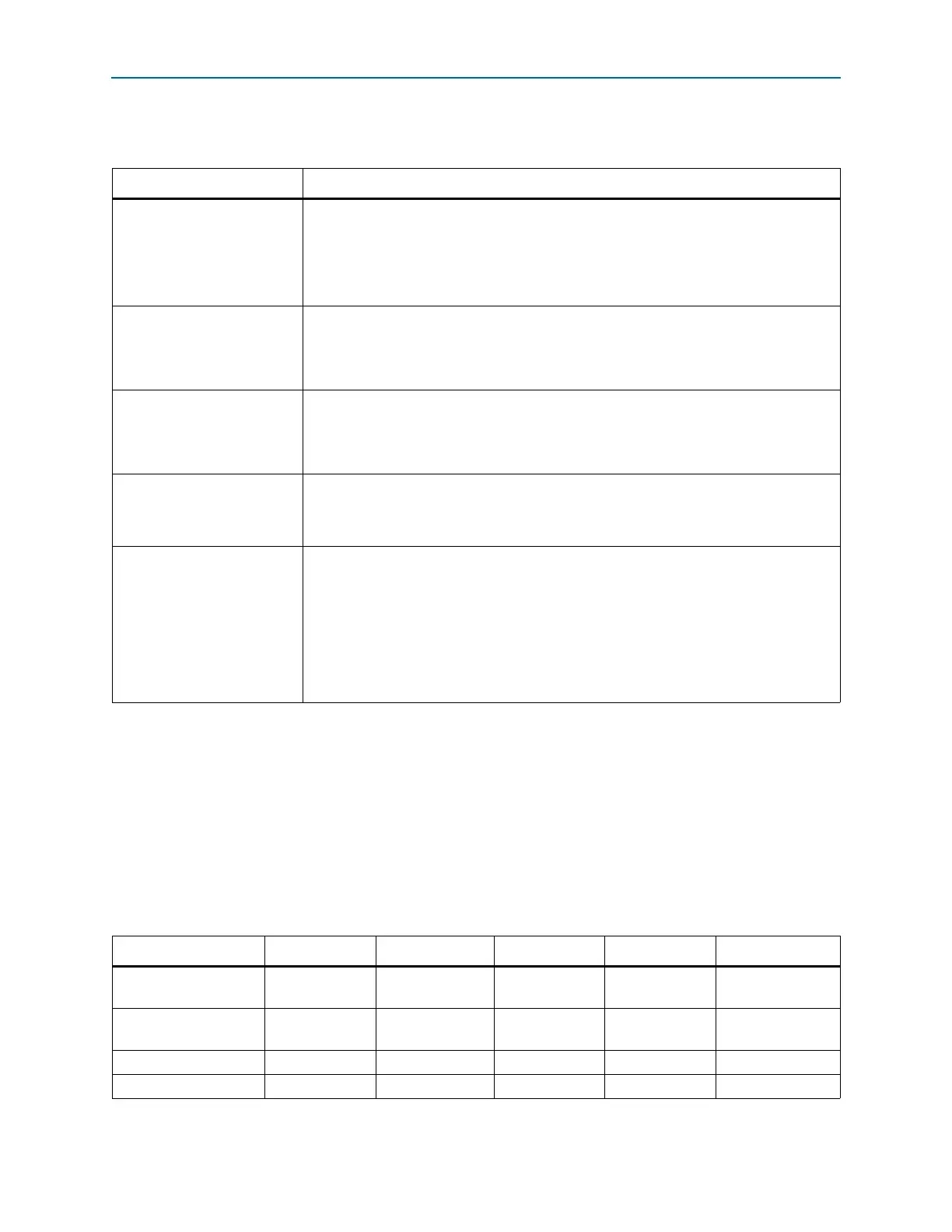

Table 2–2 lists the power-down signals available for each transceiver block.

1 For more information about offset cancellation, refer to the Cyclone IV Dynamic

Reconfiguration chapter.

1 If none of the channels is instantiated in a transceiver block, the Quartus

®

II software

automatically powers down the entire transceiver block.

Blocks Affected by the Reset and Power-Down Signals

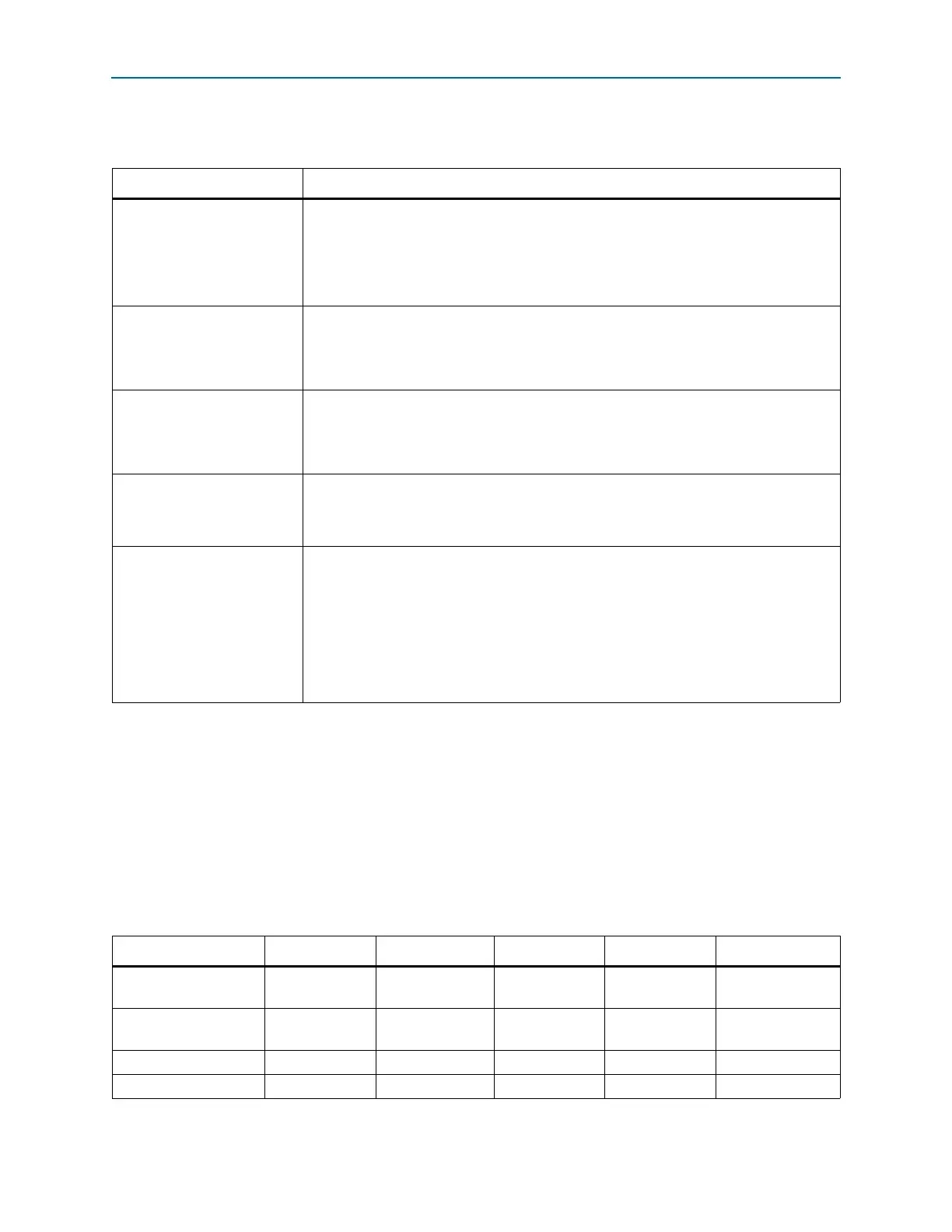

Table 2–3 lists the blocks that are affected by specific reset and power-down signals.

Table 2–2. Transceiver Block Power-Down Signals

Signal Description

pll_areset

Resets the transceiver PLL. The

pll_areset

signal is asserted in two conditions:

■ During reset sequence, the signal is asserted to reset the transceiver PLL. This signal is

controlled by the user.

■ After the transceiver PLL is reconfigured, the signal is asserted high by the

ALTPLL_RECONFIG controller. This signal is not controlled by the user.

gxb_powerdown

Powers down the entire transceiver block. When this signal is asserted, this signal powers

down the PCS and PMA in all the transceiver channels.

This signal operates independently from the other reset signals. This signal is common to

the transceiver block.

pll_locked

A status signal. Indicates the status of the transmitter multipurpose PLLs or general

purpose PLLs.

■ A high level—indicates the multipurpose PLL or general purpose PLL is locked to the

incoming reference clock frequency.

rx_freqlocked

A status signal. Indicates the status of the receiver CDR lock mode.

■ A high level—the receiver is in lock-to-data mode.

■ A low level—the receiver CDR is in lock-to-reference mode.

busy

A status signal. An output from the ALTGX_RECONFIG block indicates the status of the

dynamic reconfiguration controller. This signal remains low for the first

reconfig_clk

clock cycle after power up. It then gets asserted from the second

reconfig_clk

clock

cycle. Assertion on this signal indicates that the offset cancellation process is being

executed on the receiver buffer as well as the receiver CDR. When this signal is deasserted,

it indicates that offset cancellation is complete.

This busy signal is also used to indicate the dynamic reconfiguration duration such as in

analog reconfiguration mode and channel reconfiguration mode.

Table 2–3. Blocks Affected by Reset and Power-Down Signals (Part 1 of 2)

Transceiver Block rx_digitalreset rx_analogreset tx_digitalreset pll_areset gxb_powerdown

multipurpose PLLs and

general purpose PLLs

———v —

Transmitter Phase

Compensation FIFO

——v — v

Byte Serializer — — v — v

8B/10B Encoder — — v — v

Loading...

Loading...