1–50 Chapter 1: Cyclone IV Transceivers Architecture

Transceiver Functional Modes

Cyclone IV Device Handbook, February 2015 Altera Corporation

Volume 2

Rate Match FIFO Operation in Basic Mode

In Basic mode, the rate match FIFO performs the following operations:

■ Deletes a maximum of four skip patterns from a cluster, if there is one skip pattern

left in the cluster after deletion

■ Insert a maximum of four skip patterns in a cluster, if there are less than five skip

patterns in the cluster after deletion

■ Automatically deletes the data byte that causes the FIFO to go full and asserts the

rx_rmfifofull

flag synchronous to the subsequent data byte

■ Automatically inserts /K30.7/ (9’h1FE) after the data byte that causes the FIFO to

go empty and asserts the

rx-fifoempty

flag synchronous to the inserted /K30.7/

(9’h1FE)

Additional Options in Basic Mode

In Basic mode, the transceiver supports the following additional options:

■ low-latency PCS operation

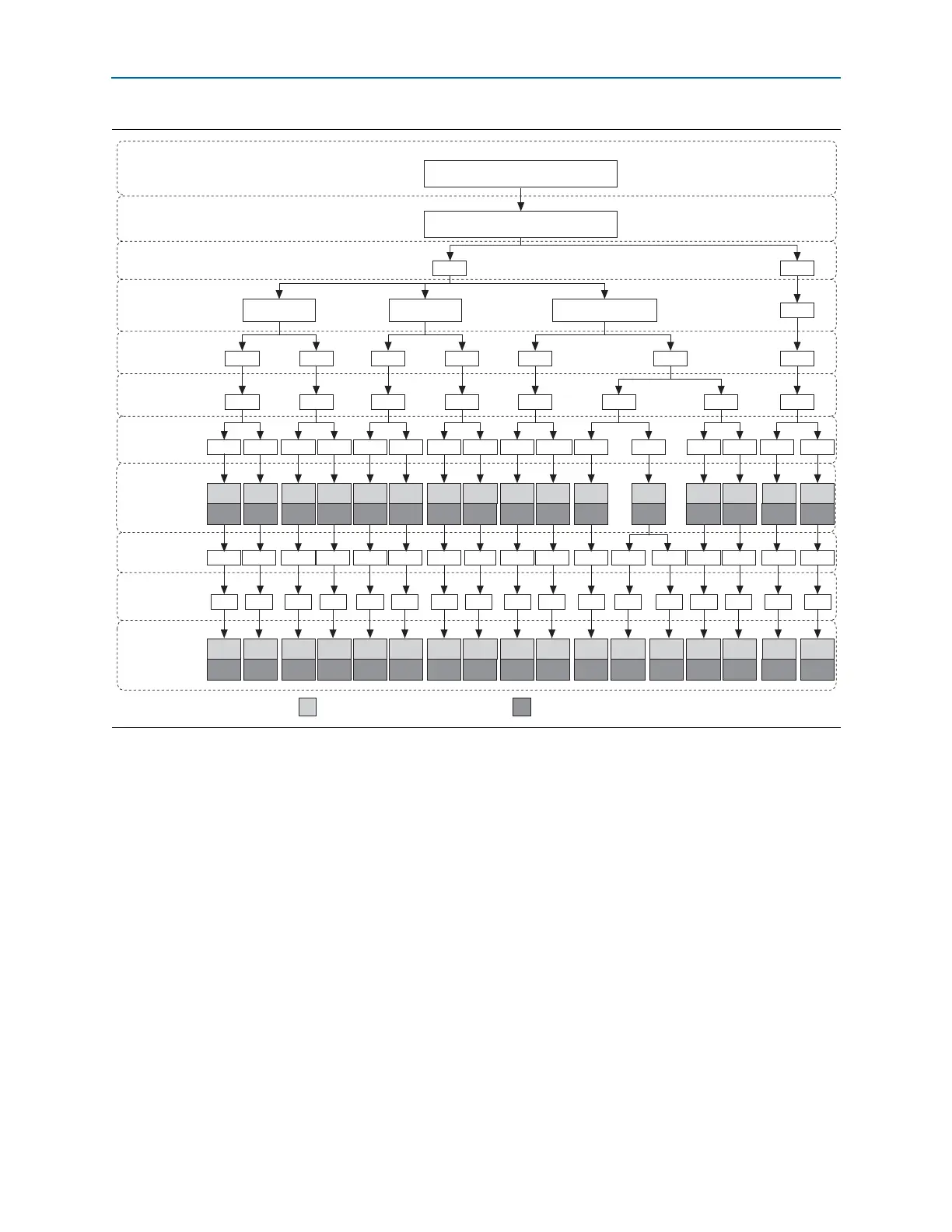

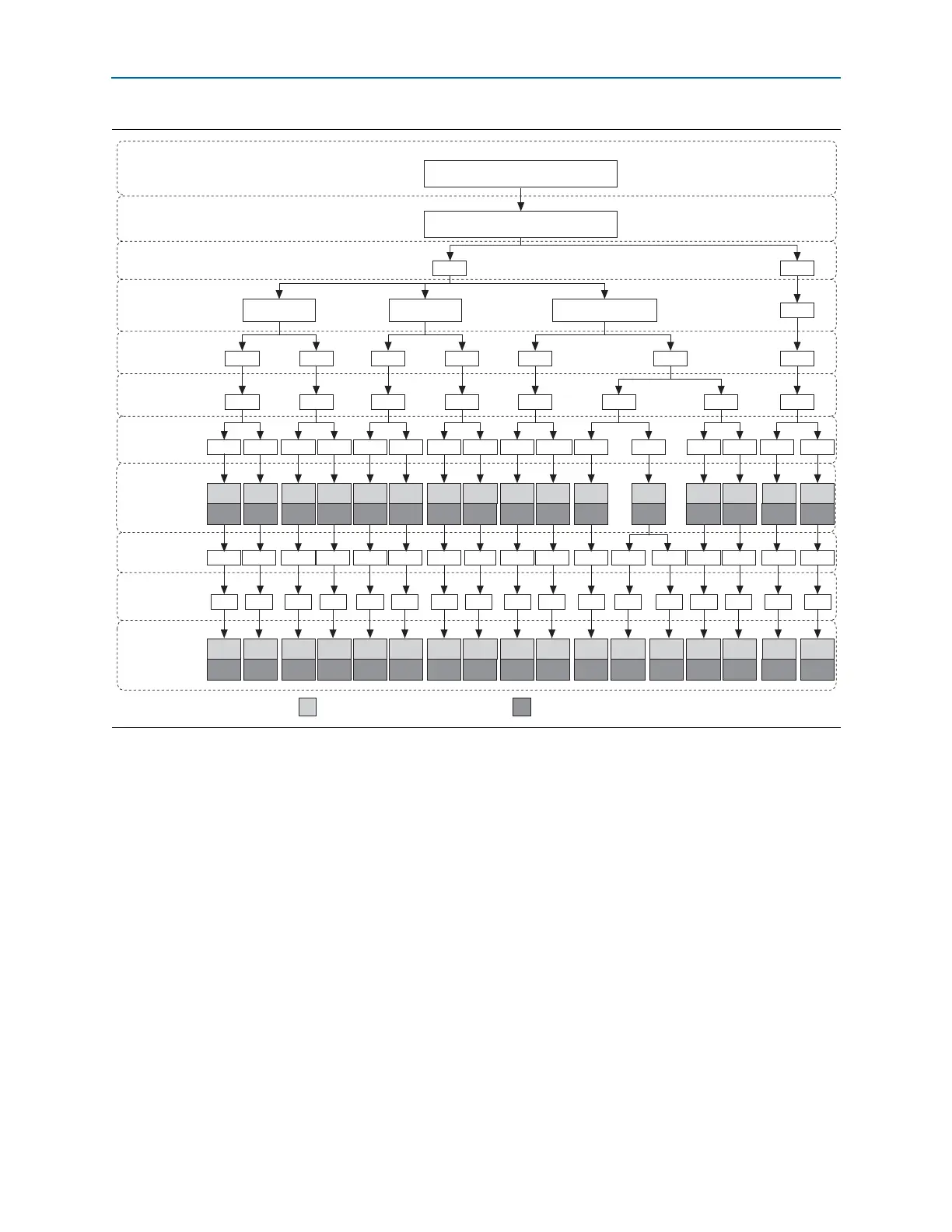

Figure 1–46. Transceiver Configurations in Basic Mode with a 10-Bit Wide PMA-to-PCS Interface

Functional Mode

Channel Bonding

Low-Latency PCS

Word Aligner

(Pattern Length)

8B/10B

Encoder/Decoder

Rate Match FIFO

Byte SERDES

Byte Ordering

FPGA Fabric-to-

Transceiver

Interface Width

FPGA Fabric-to-

Transceiver

Interface

Fredquency (MHz)

Disabled Enabled

Manual Alignment

(7-Bit, 10-Bit)

Disabled

8-Bit 16-Bit

DisabledDisabled

Disabled

Enabled

Bit Slip

(7-Bit, 10-Bit)

Disabled

Enabled

Disabled

10-Bit 20-Bit

Basic (10-Bit PMA-PCS Interface Width)

×1, ×2, ×4

Disabled Disabled

Disabled Enabled

Disabled

Disabled

Disabled Enabled

10-Bit 20-Bit

DisabledDisabled

Disabled

Disabled Enabled

Disabled

8-Bit 16-Bit

DisabledDisabled

Disabled

Enabled

Disabled Enabled

10-Bit 20-Bit

DisabledDisabled

Disabled

Automatic Synchronization

State Machine (7-Bit, 10-Bit)

Disabled Enabled

Disabled

8-Bit 16-Bit

DisabledDisabled

Disabled

Enabled

Disabled Enabled

10-Bit 20-Bit

DisabledDisabled

Disabled

Enabled

16-Bit

Disabled Enabled

8-Bit 16-Bit

DisabledDisabled

Enabled

Data Rate (Gbps)

Applicable for devices in

F324 and smaller packages

Applicable for devices in

F484 and larger packages

0.6-

1.25

0.6-

1.5625

0.6-

2.5

0.6-

3.125

0.6-

1.25

0.6-

1.5625

0.6-

2.5

0.6-

3.125

0.6-

1.25

0.6-

1.5625

0.6-

2.5

0.6-

3.125

0.6-

1.25

0.6-

1.5625

0.6-

2.5

0.6-

3.125

0.6-

1.25

0.6-

1.5625

0.6-

2.5

0.6-

3.125

0.6-

1.25

0.6-

1.5625

0.6-

2.5

0.6-

3.125

0.6-

1.25

0.6-

1.5625

0.6-

2.5

0.6-

3.125

0.6-

1.25

0.6-

1.5625

0.6-

2.5

0.6-

3.125

60-

125

60-

156.25

30-

125

30-

156.25

60-

125

60-

156.25

30-

125

30-

156.25

60-

125

60-

156.25

30-

125

30-

156.25

60-

125

60-

156.25

30-

125

30-

156.25

60-

125

60-

156.25

30-

125

30-

156.25

60-

125

60-

156.25

30-

125

30-

156.25

60-

125

60-

156.25

30-

125

30-

156.25

60-

125

60-

156.25

30-

125

30-

156.25

30-

125

30-

156.25

Loading...

Loading...