Chapter 6: I/O Features in Cyclone IV Devices 6–3

I/O Element Features

March 2016 Altera Corporation Cyclone IV Device Handbook,

Volume 1

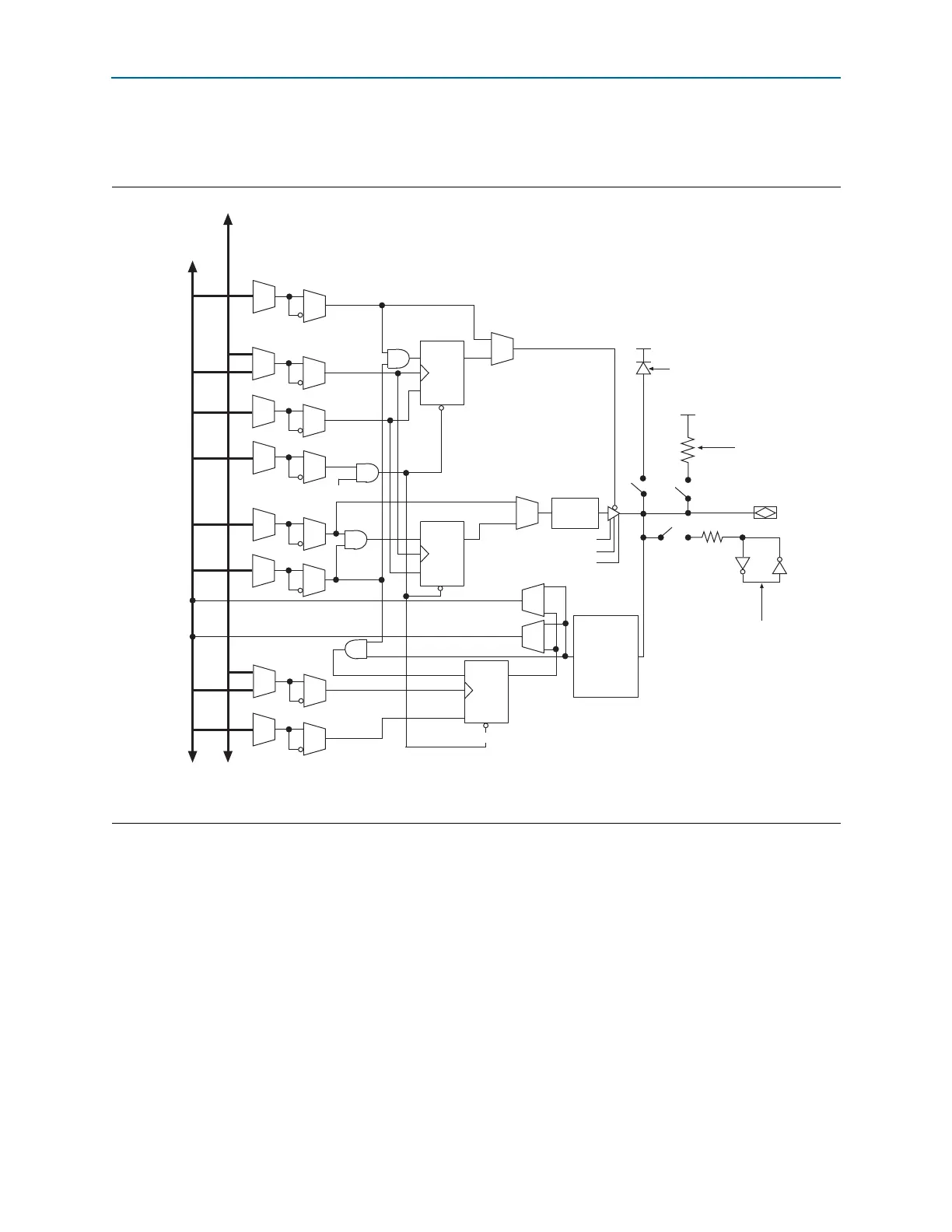

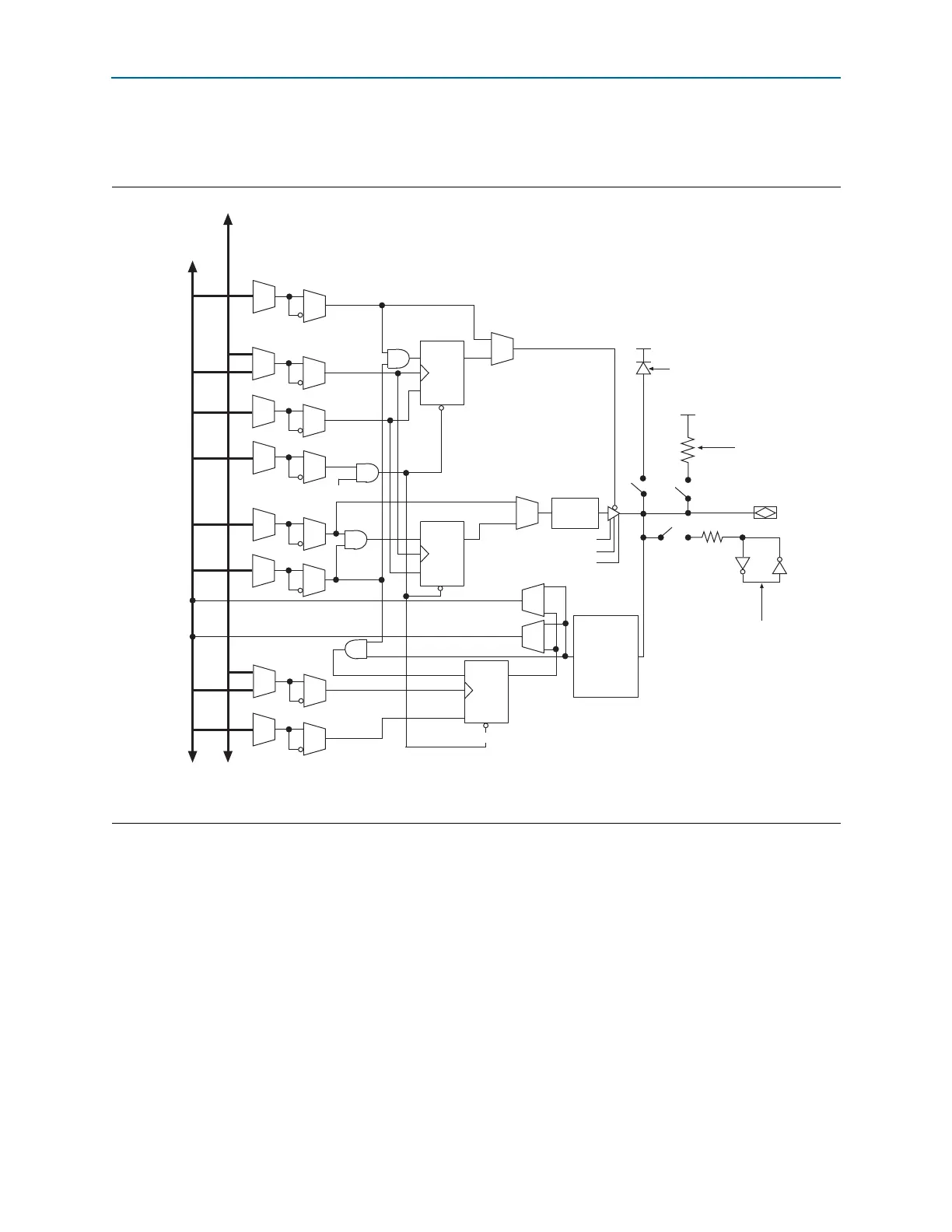

Figure 6–1 shows the Cyclone IV devices IOE structure for single data rate (SDR)

operation.

I/O Element Features

The Cyclone IV IOE offers a range of programmable features for an I/O pin. These

features increase the flexibility of I/O utilization and provide a way to reduce the

usage of external discrete components, such as pull-up resistors and diodes.

Programmable Current Strength

The output buffer for each Cyclone IV I/O pin has a programmable current strength

control for certain I/O standards.

The LVTTL, LVCMOS, SSTL-2 Class I and II, SSTL-18 Class I and II, HSTL-18 Class I

and II, HSTL-15 Class I and II, and HSTL-12 Class I and II I/O standards have several

levels of current strength that you can control.

Figure 6–1. Cyclone IV IOEs in a Bidirectional I/O Configuration for SDR Mode

Note to Figure 6–1:

(1) Tri-state control is not available for outputs configured with true differential I/O standards.

D Q

ENA

D Q

ENA

V

CCIO

V

CCIO

Optional

PCI Clamp

Programmabl

Pull-Up

Resistor

Bus Hold

Input Pin to

Input Register

Delay

or Input Pin to

Logic Array

Delay

Output

Pin Delay

clkin

oe_in

data_in0

data_in1

sclr/

preset

Chip-Wide Reset

aclr/prn

oe_out

clkout

OE

OE Register

Current Strength Control

Open-Drain Out

Column

or Row

Interconnect

io_clk[5..0]

Slew Rate Control

ACLR

/PRN

ACLR

/PRN

Output Register

D Q

ENA

ACLR

/PRN

Input Register

(1)

Loading...

Loading...