3–26 Chapter 3: Cyclone IV Dynamic Reconfiguration

Dynamic Reconfiguration Modes

Cyclone IV Device Handbook, November 2011 Altera Corporation

Volume 2

Data Rate Reconfiguration Mode Using RX Local Divider

The RX local divider resides in the RX PMA block for every channels. This is a

hardware feature where a /2 divider is available in each of the receiver channel for the

supported device. You can use this RX local divider to reconfigure the data rate at the

receiver channel. This can be used for protocols such as SDI that has data rates in

divisions of 2.

By using this RX local divider, you can support two different data rates without using

additional transceiver PLLs. This dynamic reconfiguration mode is available only for

the receiver and not applicable to the transmitter. This reconfiguration mode using the

RX local divider (/2) is only supported and available in EP4CGX30 (F484 package),

EP4CGX50, and EP4CGX75 devices.

f For more information about this RX local divider, refer to the Cyclone IV GX

Transceiver Architecture chapter.

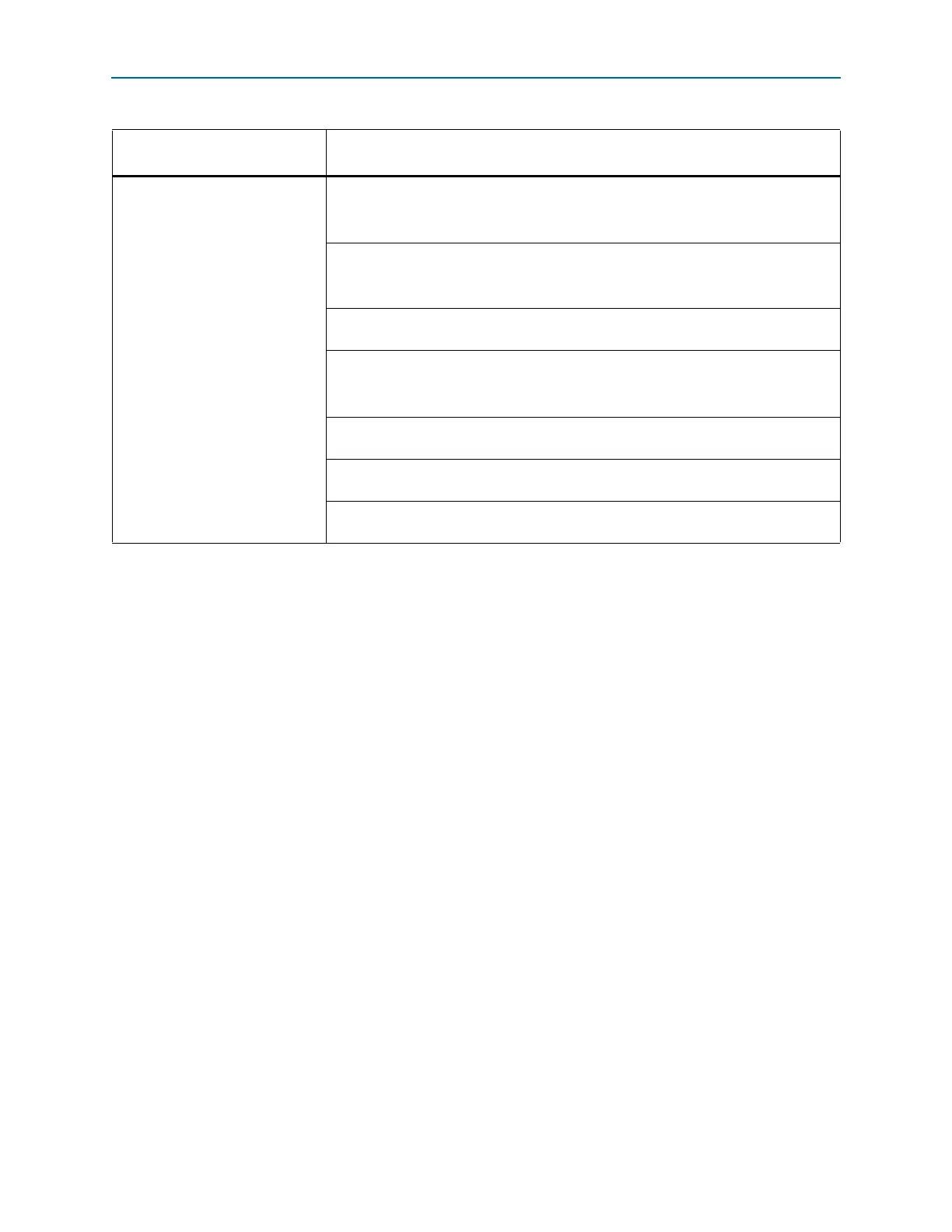

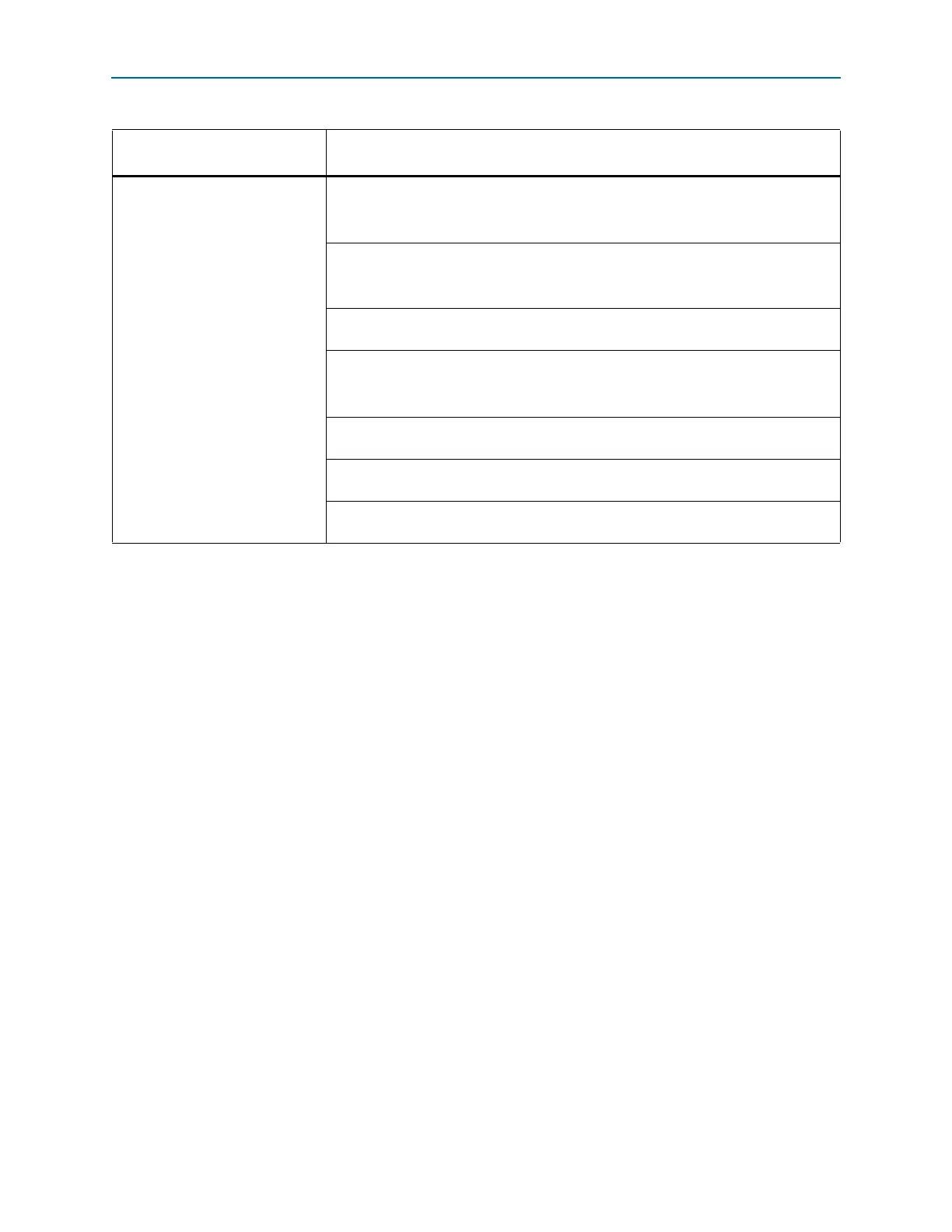

20-bit FPGA fabric-Transceiver

Channel Interface with PCS-PMA

set to 10 bits

Two 10-bit Data (

rx_dataout

)

rx_dataoutfull[9:0]

-

rx_dataout

(LSByte) and

rx_dataoutfull[25:16]

-

rx_dataout

(MSByte)

wo Receiver Sync Status Bits

rx_dataoutfull[10]

-

rx_syncstatus

(LSB) and

rx_dataoutfull[26]

-

rx_syncstatus

(MSB)

rx_dataoutfull[11]

and

rx_dataoutfull[27]

: 8B/10B disparity error indicator

(

rx_disperr

)

Two Receiver Pattern Detect Bits

rx_dataoutfull[12]

-

rx_patterndetect

(LSB) and

rx_dataoutfull[28]

-

rx_patterndetect

(MSB)

rx_dataoutfull[13]

and

rx_dataoutfull[29]

: Rate Match FIFO deletion status

indicator (

rx_rmfifodatadeleted

) in non-PCI Express (PIPE) functional modes

rx_dataoutfull[14]

and

rx_dataoutfull[30]

: Rate Match FIFO insertion status

indicator (

rx_rmfifodatainserted

) in non-PCI Express (PIPE) functional modes

rx_dataoutfull[15]

and

rx_dataoutfull[31]

: 8B/10B running disparity

indicator (

rx_runningdisp

)

Table 3–5. rx_dataoutfull[31..0] FPGA Fabric-Transceiver Channel Interface Signal Descriptions (Part 3 of 3)

FPGA Fabric-Transceiver Channel

Interface Description

Receive Signal Description (Based on Cyclone IV GX Supported FPGA

Fabric-Transceiver Channel Interface Widths)

Loading...

Loading...