1–52 Chapter 1: Cyclone IV Transceivers Architecture

Transceiver Functional Modes

Cyclone IV Device Handbook, February 2015 Altera Corporation

Volume 2

Receiver Spread Spectrum Clocking

Asynchronous SSC is not supported in Cyclone IV devices. You can implement only

synchronous SSC for SATA, V-by-One, and Display Port protocols in Basic mode.

PCI Express (PIPE) Mode

PIPE mode provides the transceiver channel datapath configuration that supports ×1,

×2, and ×4 initial lane width for PCIe Gen1 signaling rate with PIPE interface

implementation. The Cyclone IV GX transceiver provides following features in PIPE

mode:

■ PIPE interface

■ receiver detection circuitry

■ electrical idle control

■ signal detect at receiver

■ lane synchronization with compliant state machine

■ clock rate compensation with rate match FIFO

■ Low-Latency Synchronous PCIe

■ fast recovery from P0s state

■ electrical idle inference

■ compliance pattern transmission

■ reset requirement

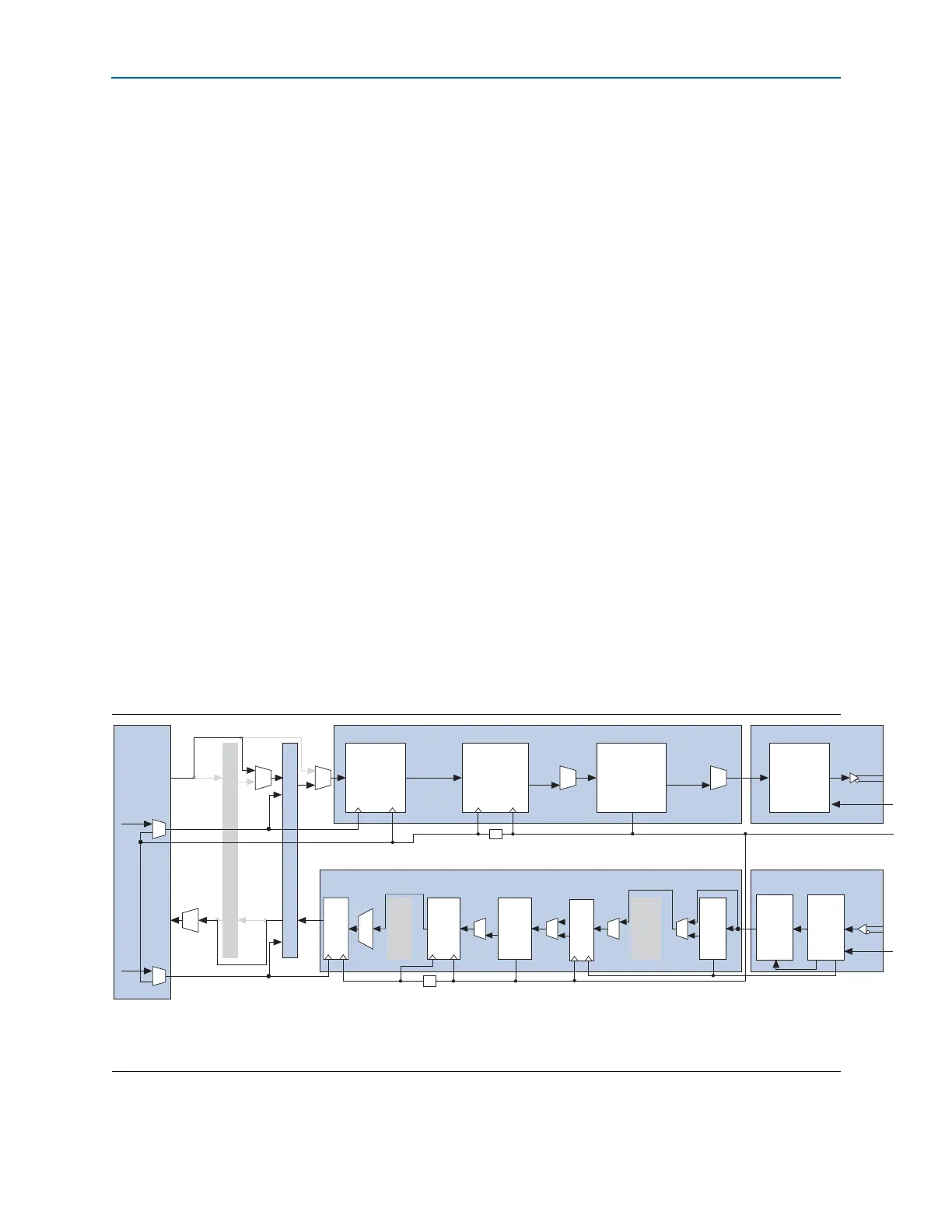

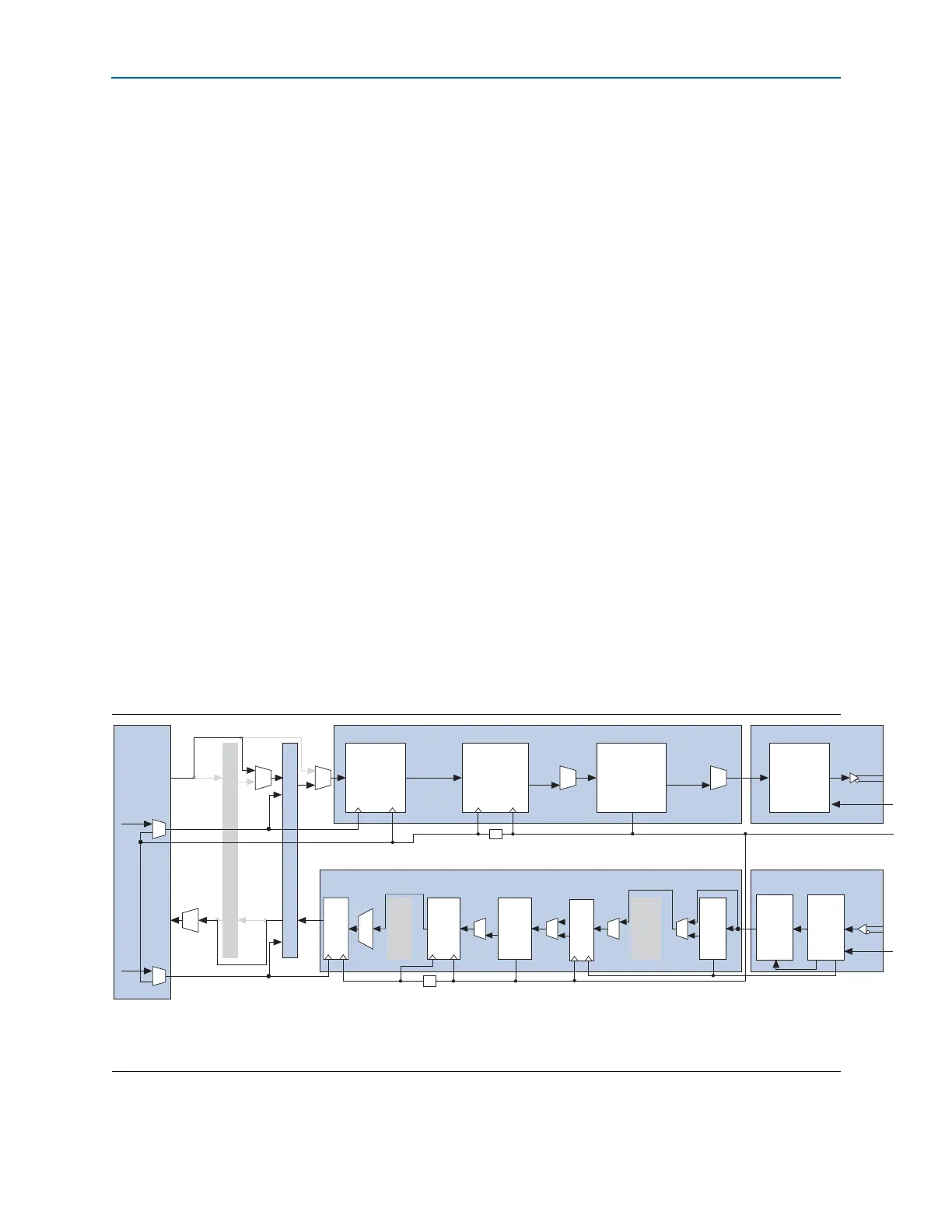

Figure 1–48 shows the transceiver channel datapath and clocking when configured in

PIPE mode with ×1 channel configuration.

.

Figure 1–48. Transceiver Channel Datapath and Clocking when Configured in PIPE Mode with ×1 Channel Configuration

Notes to Figure 1–48:

(1) Low-speed recovered clock.

(2) High-speed recovered clock.

Byte Serializer

8B/10B Encoder

Transmitter Channel PCS Transmitter Channel PMA

Serializer

FPGA

Fabric

PIPE Interface

Tx Phase

Comp

FIFO

tx_datain

tx_dataout

wr_clk rd_clk wr_clk rd_clk

high-speed

clock

low-speed clock

tx_coreclk

tx_clkout

/2

rx_coreclk

Receiver Channel PCS Receiver Channel PMA

rx_dataout

rx_datain

Deserial-

izer

CDR

Byte

De-

serializer

Byte

Order-

ing

Deskew

FIFO

8B/10B

Decoder

Rate

Match

FIFO

CDR clock

/2

Word

Aligner

Rx

Phase

Comp

FIFO

(2)

(1)

PCIe Hard IP

Loading...

Loading...