Chapter 5: Clock Networks and PLLs in Cyclone IV Devices 5–29

Hardware Features

October 2012 Altera Corporation Cyclone IV Device Handbook,

Volume 1

20%. This feature is useful when clock sources can originate from multiple cards

on the backplane, requiring a system-controlled switchover between frequencies

of operation. Choose the secondary clock frequency so the VCO operates in the

recommended frequency range. Also, set the M, N, and C counters accordingly to

keep the VCO operating frequency in the recommended range.

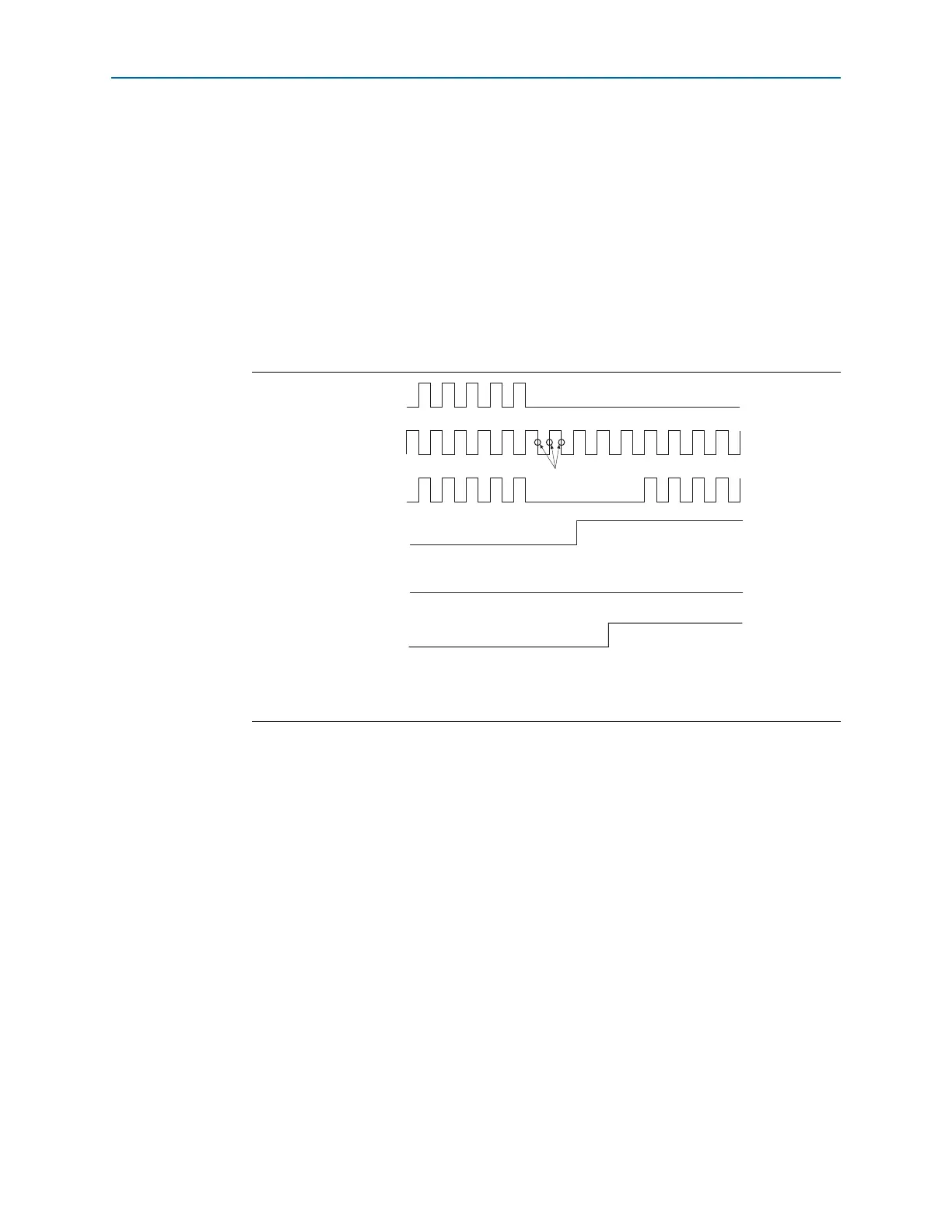

Figure 5–18 shows a waveform example of the switchover feature when using

automatic loss of clock detection. Here, the

inclk0

signal remains low. After the

inclk0

signal remains low for approximately two clock cycles, the clock-sense

circuitry drives the

clkbad0

signal high. Also, because the reference clock signal is not

toggling, the switchover state machine controls the multiplexer through the

clksw

signal to switch to

inclk1

.

Manual Override

If you are using the automatic switchover, you must switch input clocks with the

manual override feature with the

clkswitch

input.

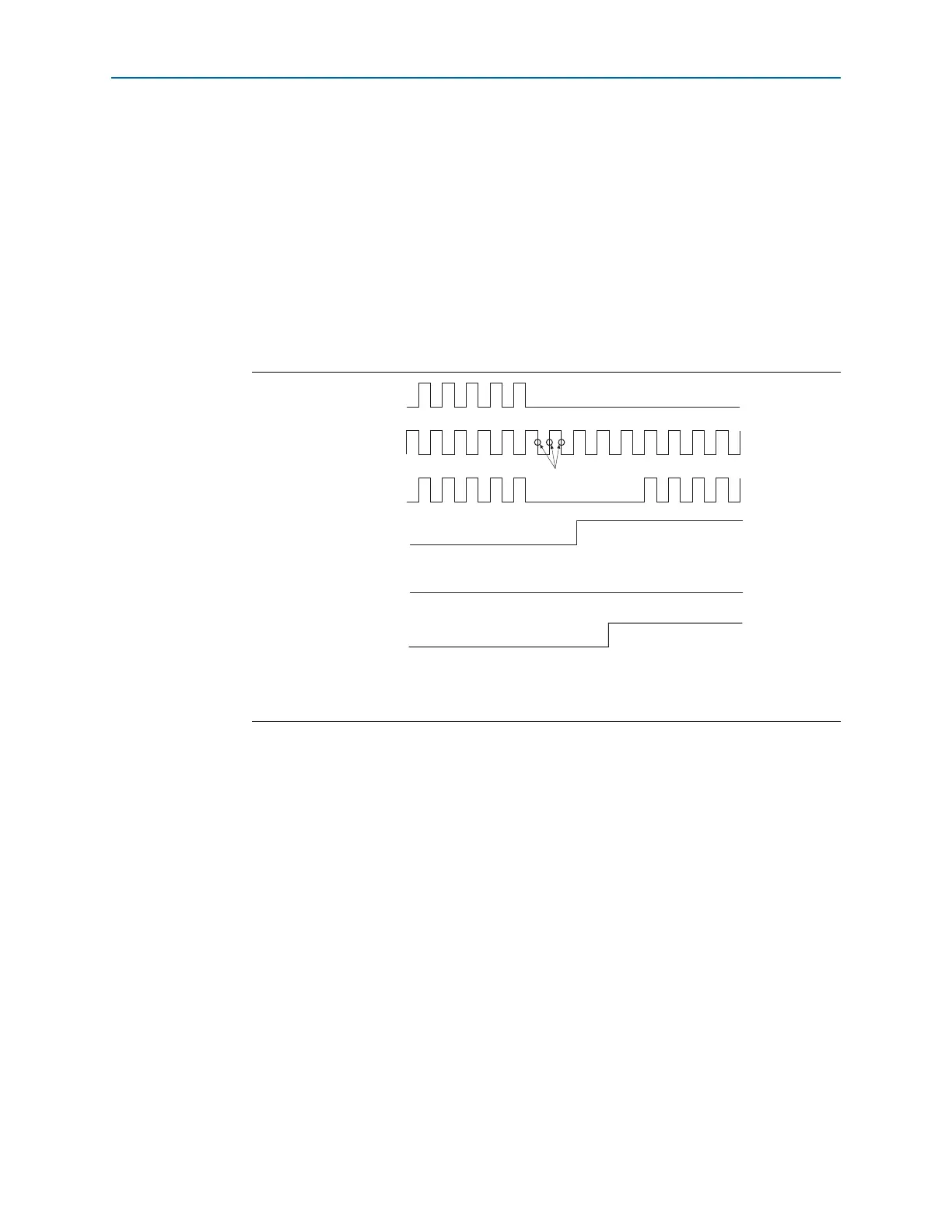

Figure 5–19 shows an example of a waveform illustrating the switchover feature

when controlled by

clkswitch

. In this case, both clock sources are functional and

inclk0

is selected as the reference clock. A low-to-high transition of the

clkswitch

signal starts the switchover sequence. The

clkswitch

signal must be high for at least

three clock cycles (at least three of the longer clock period if

inclk0

and

inclk1

have

different frequencies). On the falling edge of

inclk0

, the reference clock of the counter,

muxout

, is gated off to prevent any clock glitching. On the falling edge of

inclk1

, the

reference clock multiplexer switches from

inclk0

to

inclk1

as the PLL reference, and

the

activeclock

signal changes to indicate which clock is currently feeding the PLL.

Figure 5–18. Automatic Switchover Upon Clock Loss Detection

(1)

Note to Figure 5–18:

(1) Switchover is enabled on the falling edge of

inclk0

or

inclk1

, depending on which clock is available. In this figure,

switchover is enabled on the falling edge of

inclk1

.

inclk0

inclk1

muxout

clkbad0

clkbad1

(1)

activeclock

Loading...

Loading...