Chapter 9: SEU Mitigation in Cyclone IV Devices 9–3

Automated SEU Detection

May 2013 Altera Corporation Cyclone IV Device Handbook,

Volume 1

In user mode, Cyclone IV devices support the

CHANGE_EDREG

JTAG instruction, that

allows you to write to the 32-bit storage register. You can use Jam

™

STAPL files (.jam)

to automate the testing and verification process. You can only execute this instruction

when the device is in user mode, and it is a powerful design feature that enables you

to dynamically verify the CRC functionality in-system without having to reconfigure

the device. You can then use the CRC circuit to check for real errors induced by an

SEU.

Tab le 9 –1 describes the

CHANGE_EDREG

JTAG instructions.

1 After the test completes, Altera recommends that you power cycle the device.

Automated SEU Detection

Cyclone IV devices offer on-chip circuitry for automated checking of SEU detection.

Applications that require the device to operate error-free at high elevations or in close

proximity to earth’s north or south pole require periodic checks to ensure continued

data integrity. The error detection cyclic redundancy code feature controlled by the

Device and Pin Options dialog box in the Quartus II software uses a 32-bit CRC

circuit to ensure data reliability and is one of the best options for mitigating SEU.

You can implement the error detection CRC feature with existing circuitry in

Cyclone IV devices, eliminating the need for external logic. The CRC is computed by

the device during configuration and checked against an automatically computed CRC

during normal operation. The

CRC_ERROR

pin reports a soft error when configuration

CRAM data is corrupted. You must decide whether to reconfigure the FPGA by

strobing the

nCONFIG

pin low or ignore the error.

CRC_ERROR Pin

A specific

CRC_ERROR

error detection pin is required to monitor the results of the error

detection circuitry during user mode. Table 9–2 describes the

CRC_ERROR

pin.

f The

CRC_ERROR

pin information for Cyclone IV devices is reported in the Cyclone IV

Devices Pin-Outs on the Altera

®

website.

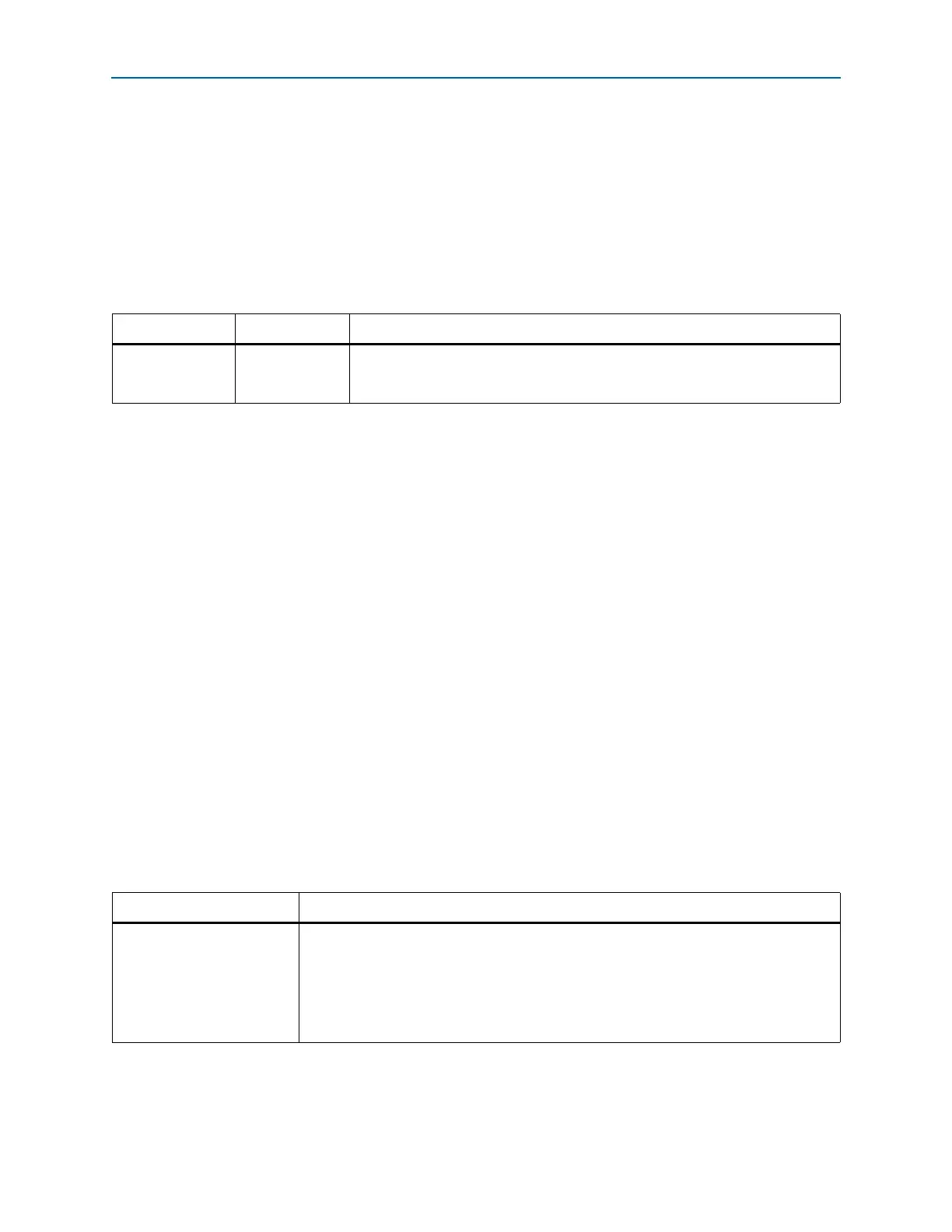

Table 9–1. CHANGE_EDREG JTAG Instruction

JTAG Instruction Instruction Code Description

CHANGE_EDREG

00 0001 0101

This instruction connects the 32-bit CRC storage register between

TDI

and

TDO

.

Any precomputed CRC is loaded into the CRC storage register to test the operation

of the error detection CRC circuitry at the

CRC_ERROR

pin.

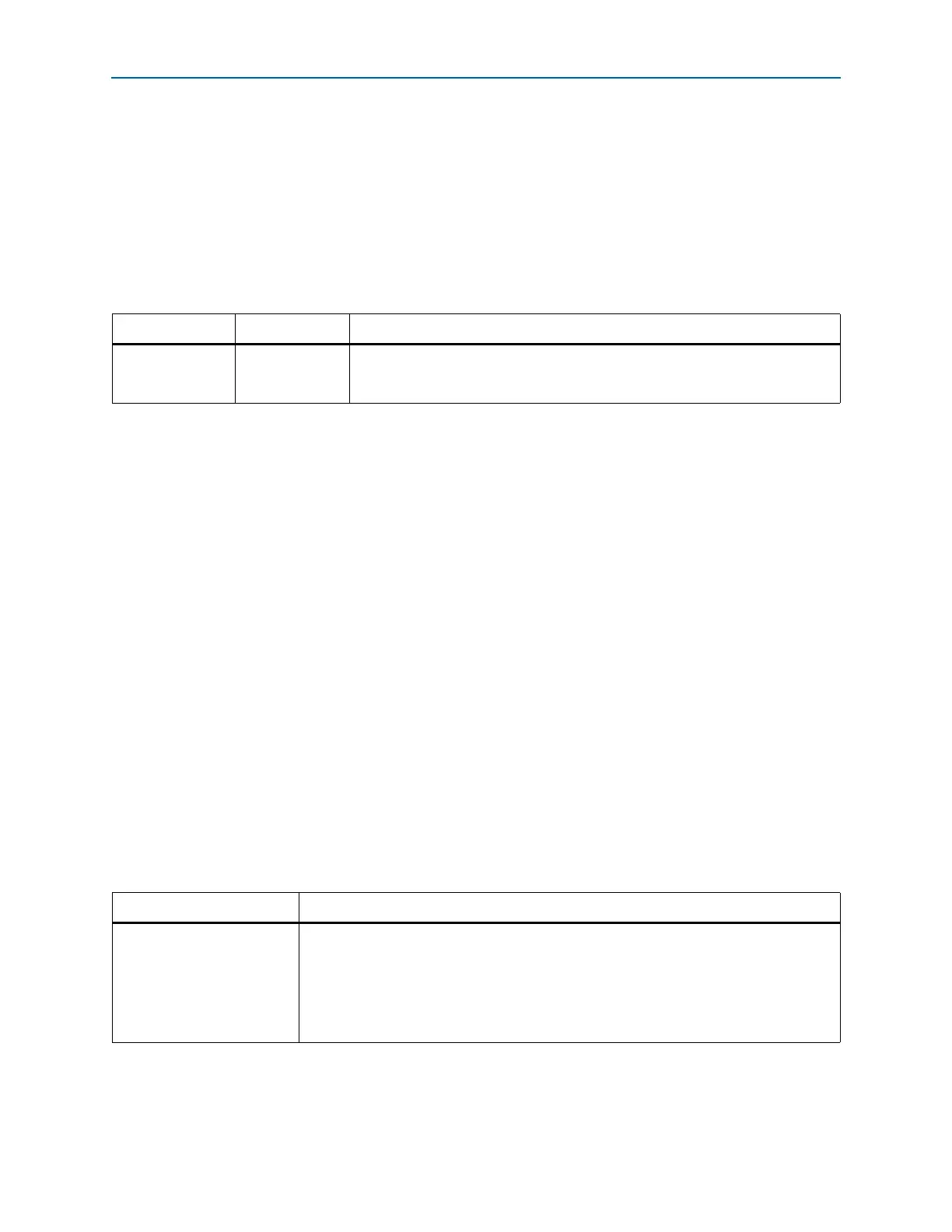

Table 9–2. Cyclone IV Device CRC_ERROR Pin Description

CRC_ERROR Pin Type Description

I/O, Output (open-drain)

Active high signal indicates that the error detection circuit has detected errors in the

configuration SRAM bits. This pin is optional and is used when the CRC error detection

circuit is enabled in the Quartus II software from the Error Detection CRC tab of the Device

and Pin Options dialog box.

When using this pin, connect it to an external 10-k pull-up resistor to an acceptable

voltage that satisfies the input voltage of the receiving device.

Loading...

Loading...