1–58 Chapter 1: Cyclone IV Transceivers Architecture

Transceiver Functional Modes

Cyclone IV Device Handbook, February 2015 Altera Corporation

Volume 2

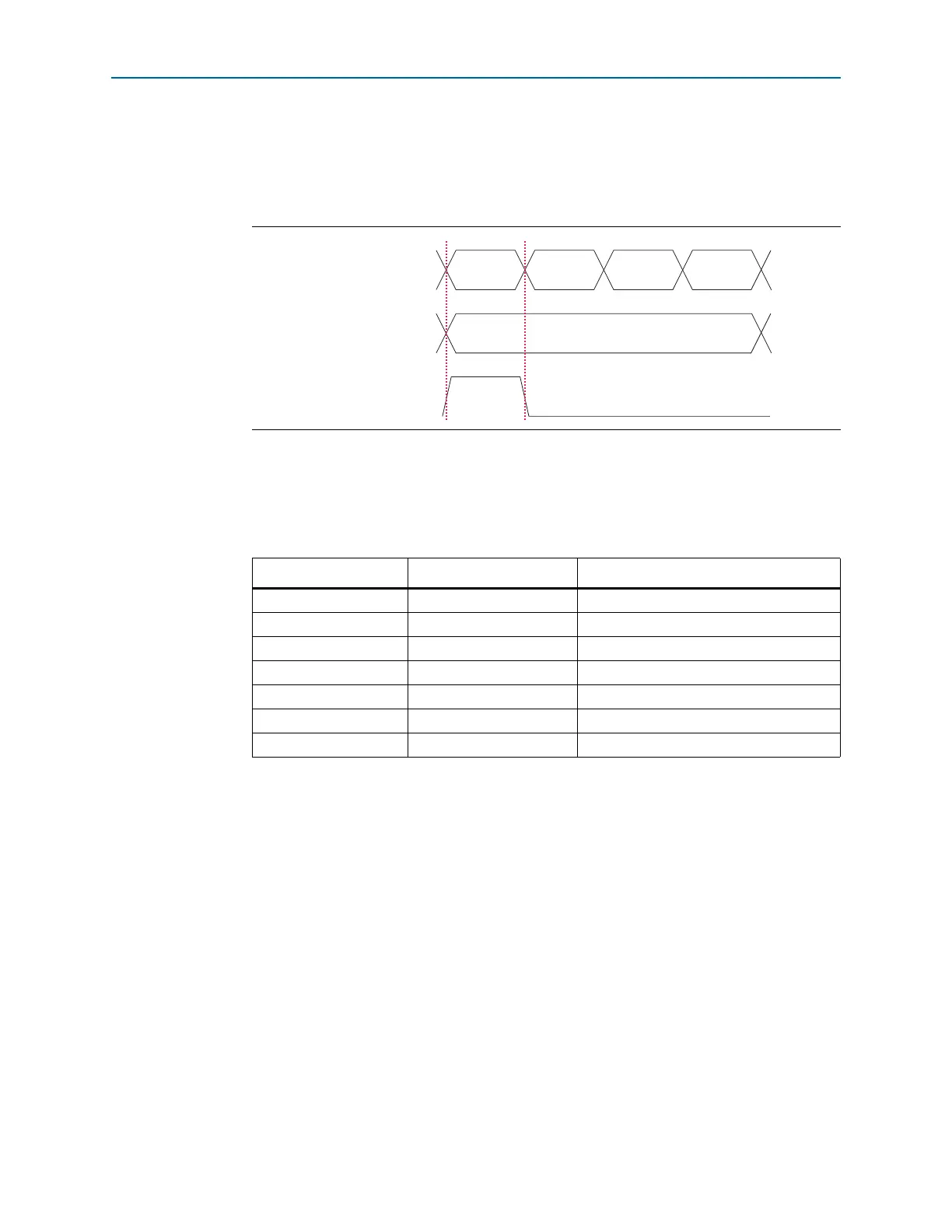

The compliance pattern is a repeating sequence of the four code groups: /K28.5/;

/D21.5/; /K28.5/; /D10.2/. Figure 1–53 shows the compliance pattern transmission

where the

tx_forcedispcompliance

port must be asserted in the same parallel clock

cycle as /K28.5/D21.5/ of the compliance pattern on

tx_datain[15..0]

port.

Reset Requirement

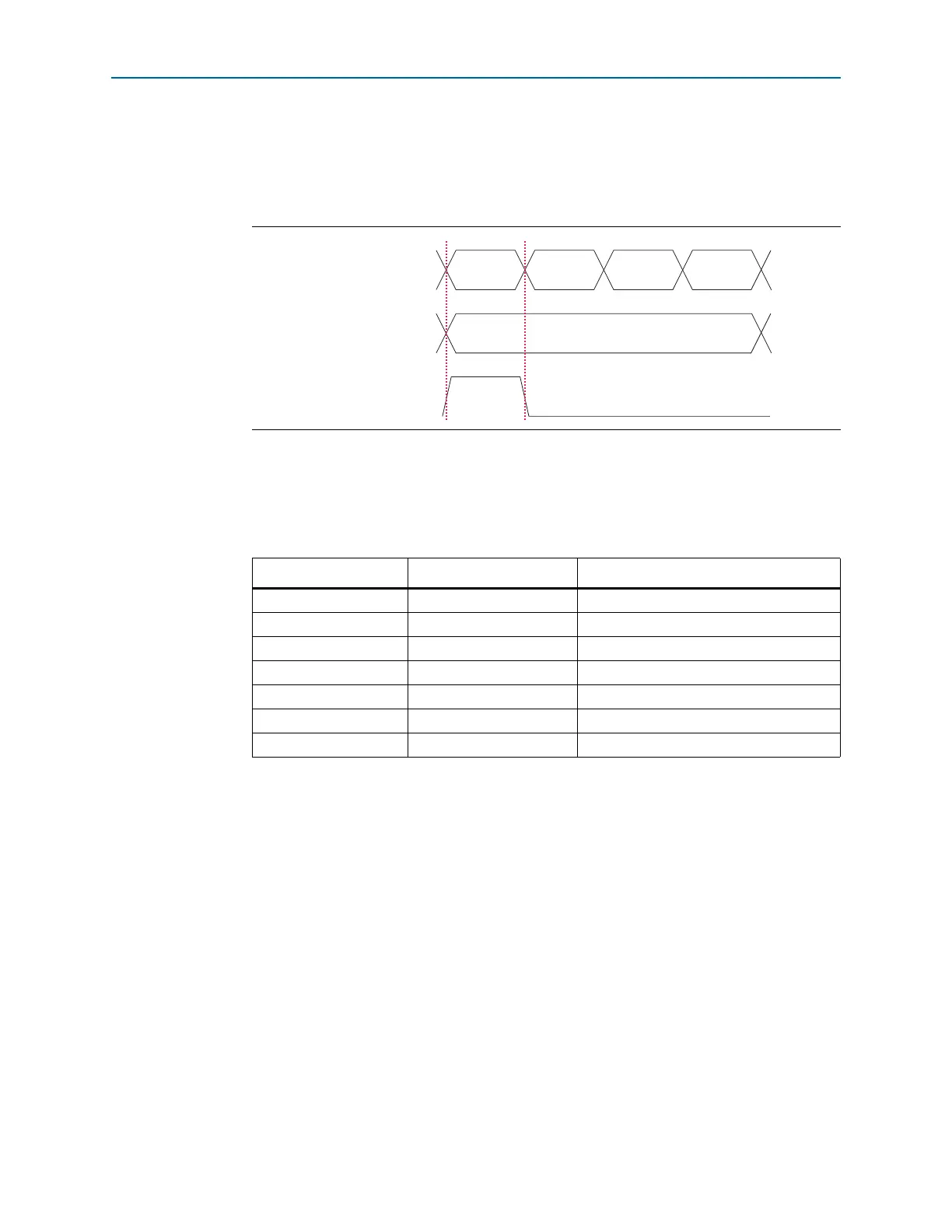

Cyclone IV GX devices meets the PCIe reset time requirement from device power up

to the link active state with the configuration schemes listed in Table 1–17.

GIGE Mode

GIGE mode provides the transceiver channel datapath configuration for GbE

(specifically the 1000 Base-X physical layer device (PHY) standard) protocol

implementation. The Cyclone IV GX transceiver provides the PMA and the following

PCS functions as defined in the IEEE 802.3 specification for 1000 Base-X PHY:

■ 8B/10B encoding and decoding

■ synchronization

If you enabled the auto-negotiation state machine in the FPGA core with the rate

match FIFO, refer to “Clock Frequency Compensation” on page 1–63.

Figure 1–53. Compliance Pattern Transmission Support in PCI Express (PIPE) Mode

Table 1–18. Electrical Idle Inference Conditions

Device Configuration Scheme Configuration Time (ms)

EP4CGX15 Passive serial (PS) 51

EP4CGX22 PS 92

EP4CGX30

(1)

PS 92

EP4CGX50 Fast passive parallel (FPP) 41

EP4CGX75 FPP 41

EP4CGX110 FPP 70

EP4CGX150 FPP 70

Note to Table 1–18:

(1) EP4CGX30 device in F484 package fulfills the PCIe reset time requirement using FPP configuration scheme with

configuration time of 41 ms.

tx_ctrldetect[1..0] 01

tx_forcedispcompliance

tx_datain[15..0] B5BC 4ABC B5BC 4ABC

/K28.5/D21.5/ /K28.5/D21.5//K28.5/D10.2/ /K28.5/D10.2/

Loading...

Loading...