Chapter 1: Cyclone IV Transceivers Architecture 1–93

Document Revision History

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

Document Revision History

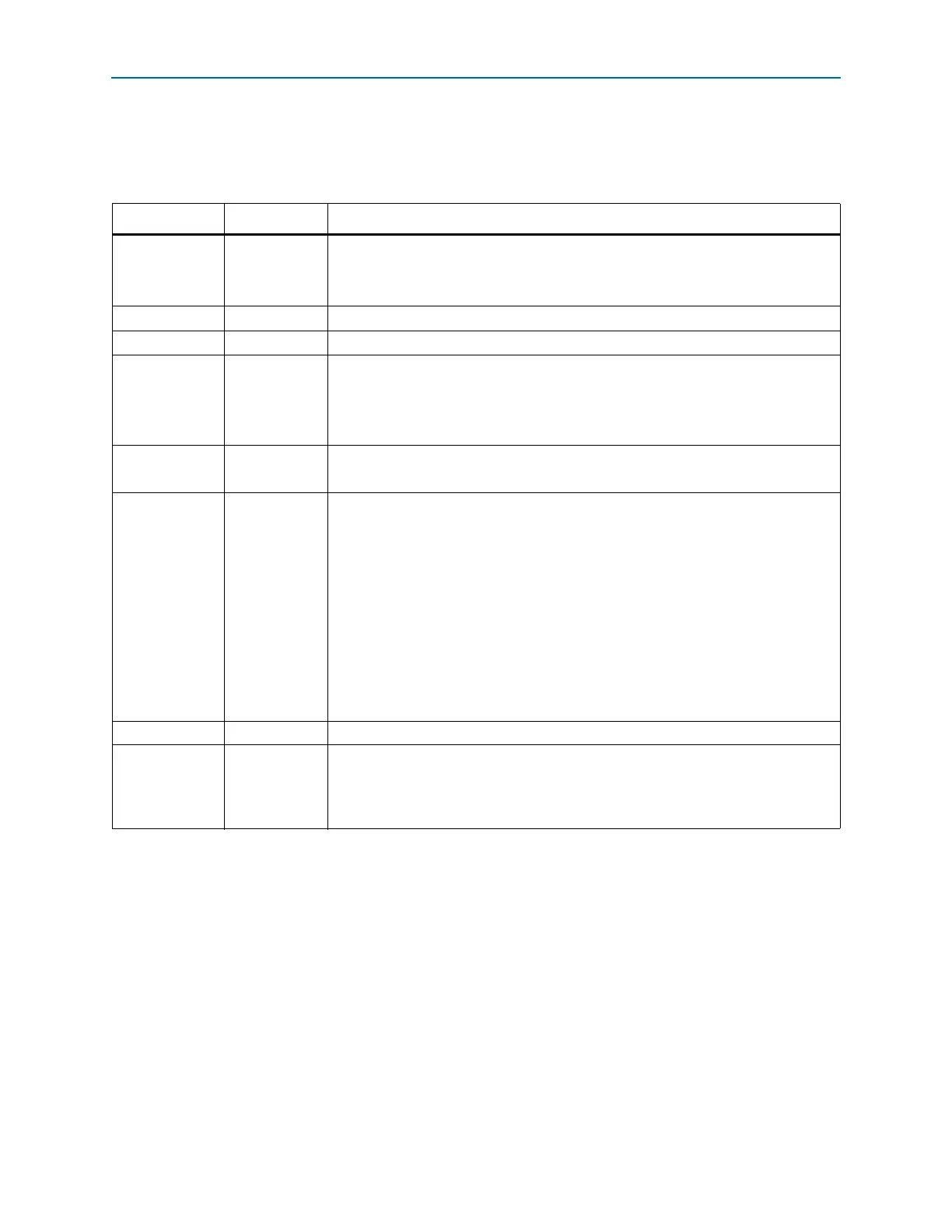

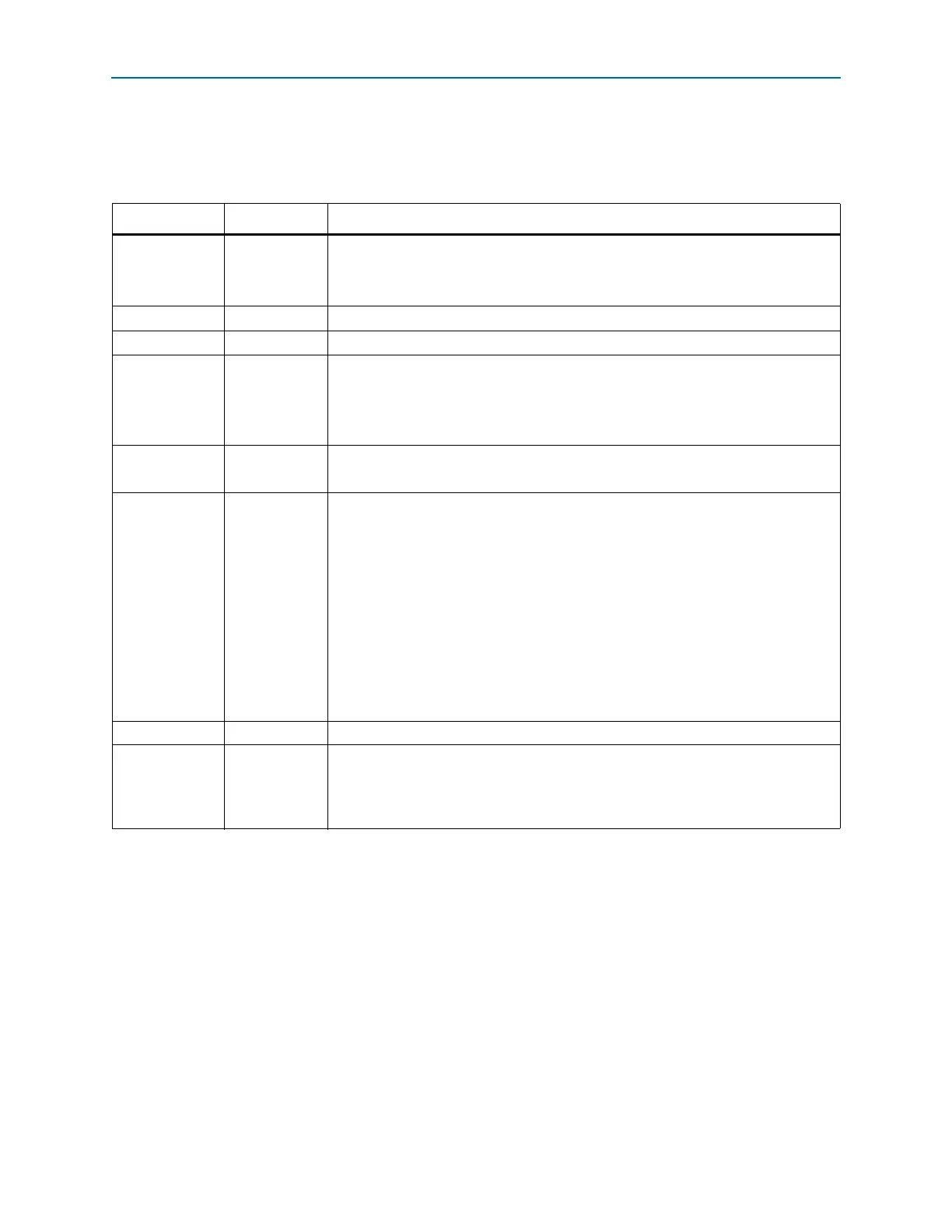

Table 1–30 lists the revision history for this chapter.

Table 1–30. Document Revision History

Date Version Changes

February 2015 3.7

■ Updated the GiGE row in Table 1–14.

■ Updated the “GIGE Mode” section.

■ Updated the note in the “Clock Frequency Compensation” section.

October 2013 3.6 Updated Figure 1–15 and Table 1–4.

May 2013 3.5 Updated Table 1–27 by setting “rx_locktodata” and “rx_locktorefclk” to “Input”

October 2012 3.4

■ Updated the data rate for the V-by-one protocol and the F324 package support in

HD-SDI in Table 1–1.

■ Updated note (1) to Figure 1–27.

■ Added latency information to Figure 1–67.

November 2011 3.3

■ Updated “Word Aligner” and “Basic Mode” sections.

■ Updated Figure 1–37.

December 2010 3.2

■ Updated for the Quartus II software version 10.1 release.

■ Updated Table 1–1, Table 1–5, Table 1–11, Table 1–14, Table 1–24, Table 1–25,

Table 1–26, Table 1–27, Table 1–28, and Table 1–29.

■ Updated “8B/10B Encoder”, “Transmitter Output Buffer”, “Receiver Input Buffer”,

“Clock Data Recovery”, “Miscellaneous Transmitter PCS Features”, “Miscellaneous

Receiver PCS Feature”, “Input Reference Clocking”, “PCI Express (PIPE) Mode”,

“Channel Deskewing”, “Lane Synchronization”, “Serial Loopback”, and “Self Test

Modes” sections.

■ Added Figure 1–9, Figure 1–10, Figure 1–19, Figure 1–20, and Figure 1–43.

■ Updated Figure 1–53, Figure 1–55, Figure 1–59, Figure 1–60, Figure 1–69,

Figure 1–70, Figure 1–71, Figure 1–72, Figure 1–73, and Figure 1–74.

November 2010 3.1 Updated Introductory information.

July 2010 3.0

■ Updated information for the Quartus II software version 10.0 release.

■ Reset control, power down, and dynamic reconfiguration information moved to

new Cyclone IV Reset Control and Power Down and Cyclone IV Dynamic

Reconfiguration chapters.

Loading...

Loading...