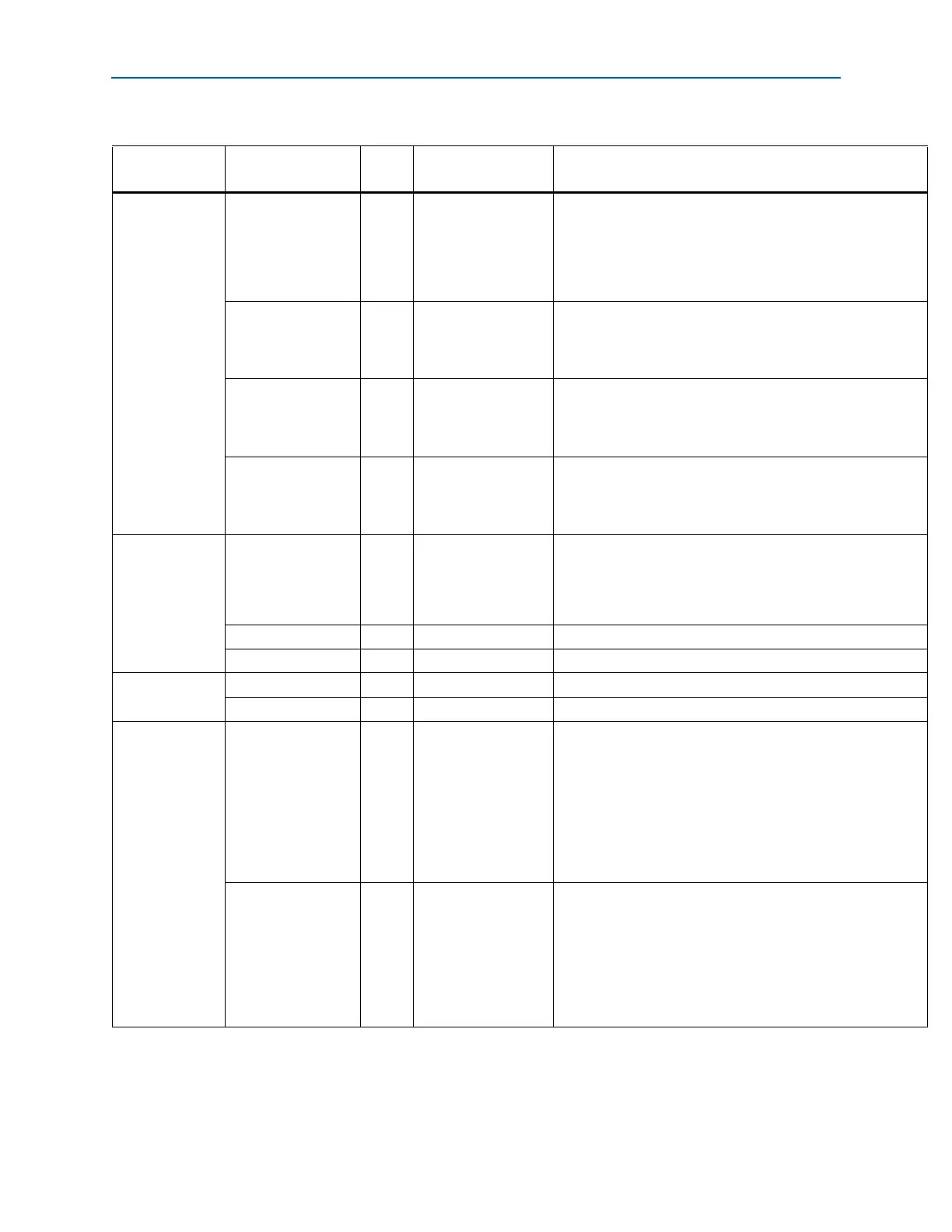

1–92 Chapter 1: Cyclone IV Transceivers Architecture

Transceiver Top-Level Port Lists

Cyclone IV Device Handbook, February 2015 Altera Corporation

Volume 2

Reset & Power

Down

gxb_powerdown Input Asynchronous signal

Transceiver block power down.

■ When asserted, all digital and analog circuitry in the PCS,

HSSI, CDR, and PCIe modules are powered down.

■ Asserting the gxb_powerdown signal does not power

down the refclk buffers.

tx_digitalreset Input

Asynchronous signal.

The minimum pulse

width is two parallel

clock cycles.

Transmitter PCS reset.

■ When asserted, the transmitter PCS blocks are reset.

rx_analogreset Input

Asynchronous signal.

The minimum pulse

width is two parallel

clock cycles.

Receiver PMA reset.

■ When asserted, analog circuitry in the receiver PMA block

is reset.

rx_digitalreset Input

Asynchronous signal.

The minimum pulse

width is two parallel

clock cycles.

Receiver PCS reset.

■ When asserted, the receiver PCS blocks are reset.

Reconfiguration

reconfig_clk Input Clock signal

Dynamic reconfiguration clock.

■ Also used for offset cancellation except in PIPE mode.

■ For the supported frequency range for this clock, refer to

the Cyclone IV Device Data Sheet chapter.

reconfig_togxb Input Asynchronous signal From the dynamic reconfiguration controller.

reconfig_fromgxb Output Asynchronous signal To the dynamic reconfiguration controller.

Calibration Block

cal_blk_clk Input Clock signal Clock for the transceiver calibration block.

cal_blk_powerdown Input Asynchronous signal Calibration block power down control.

Test Mode

rx_bistdone Output Asynchronous signal

BIST or PRBS test completion indicator.

■ A high level during BIST test mode indicates the verifier

either receives complete pattern cycle or detects an error

and stays asserted until being reset using the

rx_digitalreset port.

■ A high level during PRBS test mode indicates the verifier

receives complete pattern cycle and stays asserted until

being reset using the rx_digitalreset port.

rx_bisterr Output Asynchronous signal

BIST or PRBS verifier error indicator

■ In BIST test mode, the signal stays asserted upon detecting

an error until being reset using the rx_digitalreset

port.

■ In PRBS test mode, the signal asserts for a minimum of 3

rx_clkout clock cycles upon detecting an error and

deasserts if the following PRBS sequence contains no error.

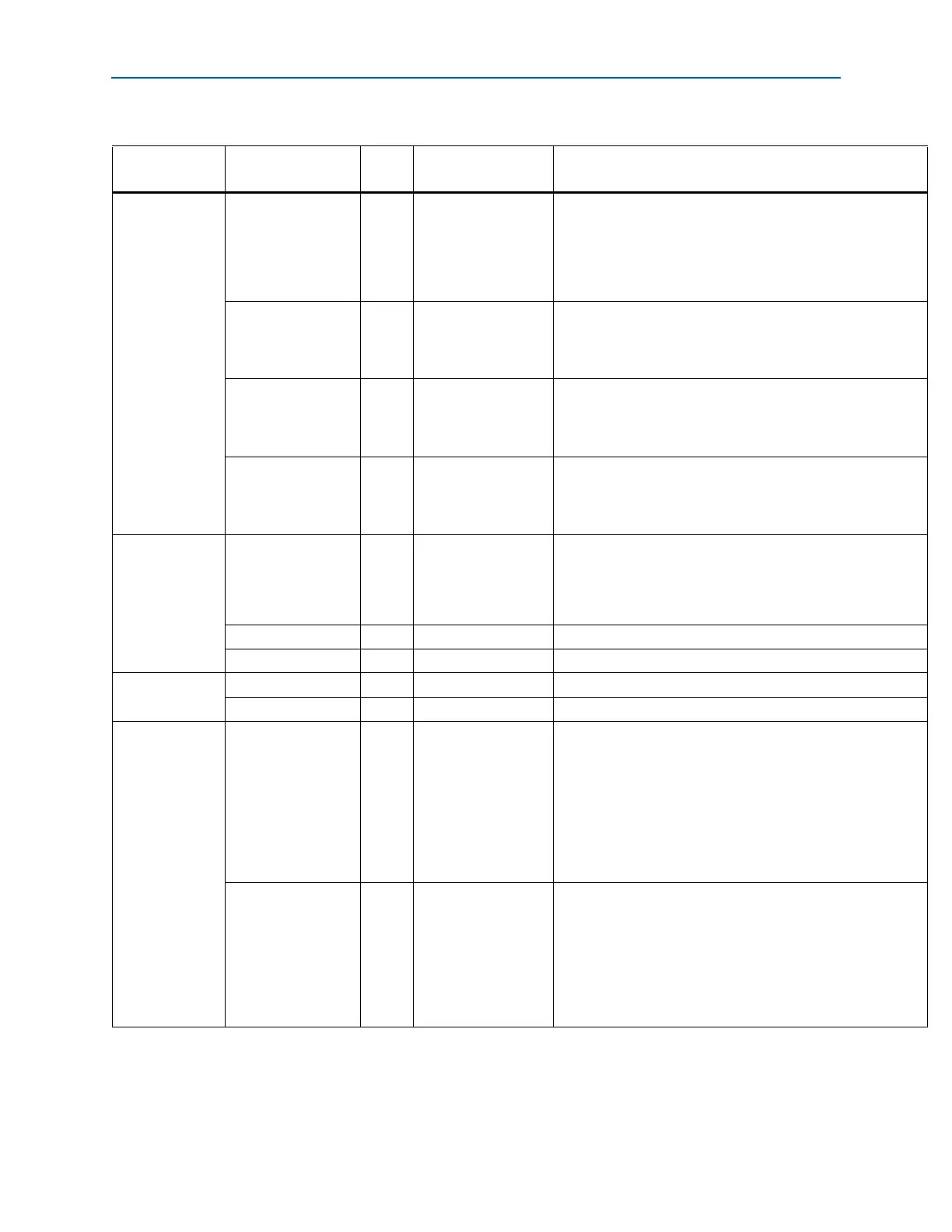

Table 1–29. Multipurpose PLL, General Purpose PLL and Miscellaneous Ports in ALTGX Megafunction for

Cyclone IV GX (Part 2 of 2)

Block Port Name

Input/

Output

Clock Domain Description

Loading...

Loading...