Chapter 1: Cyclone IV Transceivers Architecture 1–75

Transceiver Functional Modes

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

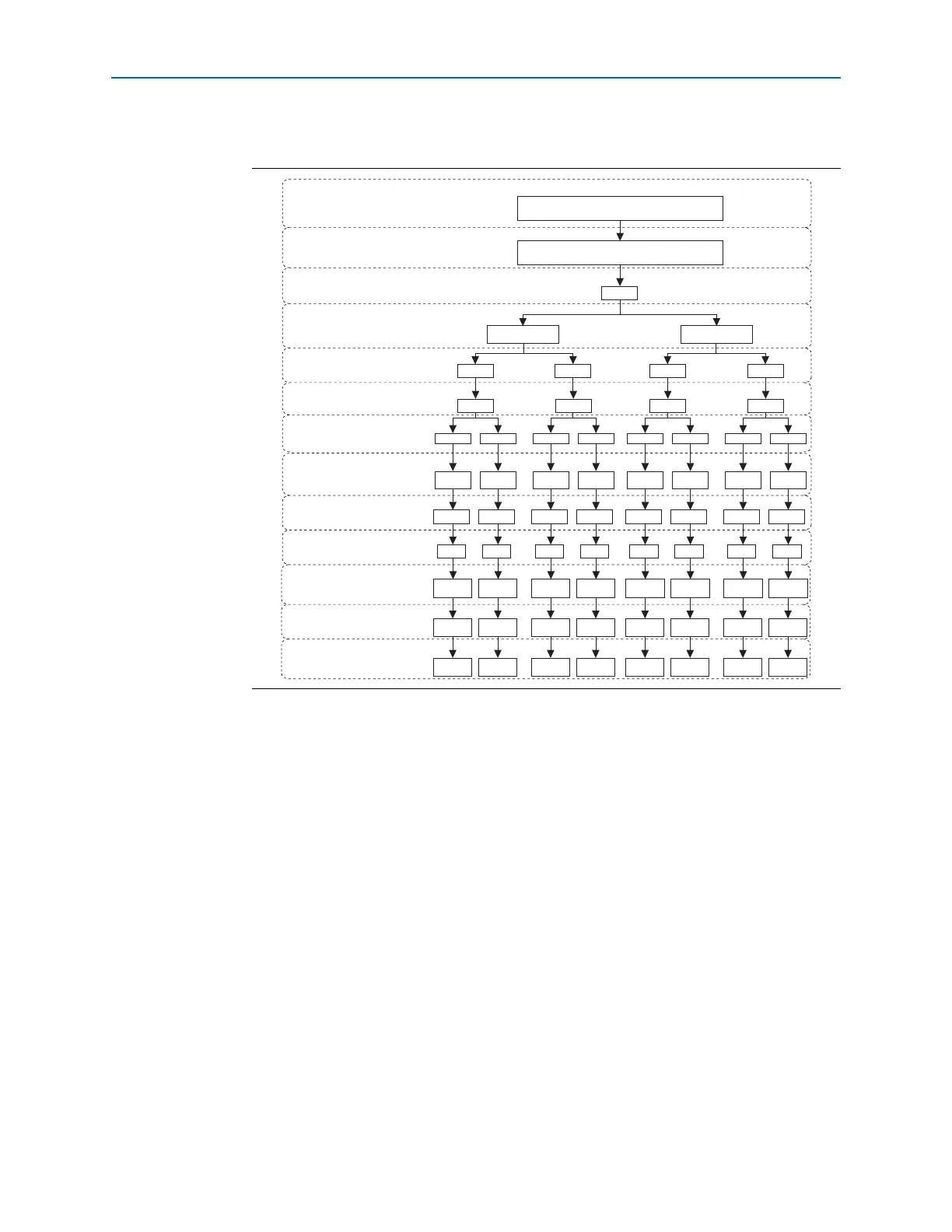

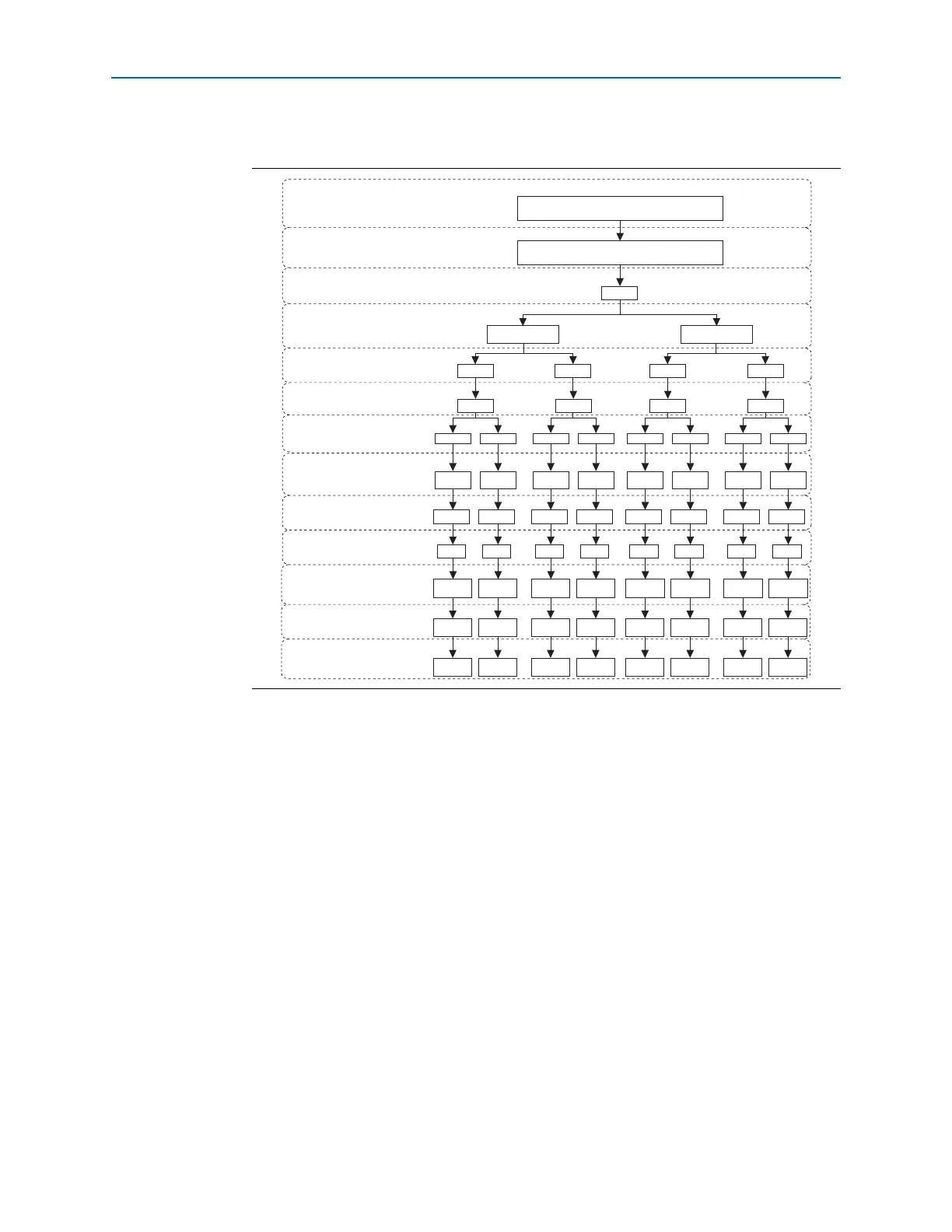

Figure 1–67 shows the transceiver configuration in Deterministic Latency mode.

Both CPRI and OBSAI protocols define the serial interface connecting the base station

component (specifically channel cards) and remote radio heads (specifically radio

frequency cards) in a radio base station system with fiber optics. The protocols require

the accuracy of round trip delay measurement for single-hop and multi-hop

connections to be within ± 16.276 ns. The Cyclone IV GX transceivers support the

following CPRI and OBSAI line rates using Deterministic Latency mode:

■ CPRI —614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps, and 3.072 Gbps

■ OBSAI—768 Mbps, 1.536 Gbps, and 3.072 Gbps

f For more information about deterministic latency implementation, refer to AN 610:

Implementing Deterministic Latency for CPRI and OBSAI Protocols in Stratix IV, HardCopy

IV, Arria II GX, and Cyclone IV Devices.

Registered Mode Phase Compensation FIFO

In Deterministic Latency mode, the RX phase compensation FIFO is set to registered

mode while the TX phase compensation FIFO supports optional registered mode.

When set into registered mode, the phase compensation FIFO acts as a register and

eliminates the latency uncertainty through the FIFOs.

Figure 1–67. Transceiver Configuration in Deterministic Latency Mode

Functional Mode

Channel Bonding

Low-Latency PCS

Word Aligner (Pattern Length)

8B/10B Encoder/Decoder

Rate Match FIFO

Byte SERDES

Byte Ordering

FPGA Fabric-to-Transceiver

Interface Width

FPGA Fabric-to-Transceiver

Interface Frequency (MHz)

TX PCS Latency (FPGA

Fabric-Transceiver Interface

Clock Cycles)

RX PCS Latency (FPGA

Fabric-Transceiver Interface

Clock Cycles)

Disabled

Deterministic Latency

×1, ×4

Data Rate (Gbps)

Disabled

Disabled

Disabled

0.6-

3.125

0.6-

1.5625

0.6-

3.125

0.6-

1.5625

0.6-

3.125

0.6-

1.5625

0.6-

3.125

0.6-

1.5625

16-Bit

Disabled

Enabled

Enabled

Disabled

Enabled

Disabled

Enabled

Disabled

Enabled

Manual Alignment

(10-Bit)

Bit Slip

(10-Bit)

8-Bit

Disabled

20-Bit

Disabled

10-Bit

Disabled

Disabled

DisabledDisabledDisabledDisabled

16-Bit

Disabled

Enabled

8-Bit

Disabled

20-Bit

Disabled

10-Bit

60-

156.25

30-

156.25

60-

156.25

30-

156.25

60-

156.25

30-

156.25

60-

156.25

30-

156.25

2.5 - 3.5 4 - 5 2.5 - 3.5 4 - 5 2.5 - 3 4 2.5 - 3 4

5 - 6 8 - 9 5 - 6 8 - 9 5 - 6 8 - 9 5 - 6 8 - 9

Loading...

Loading...