Chapter 1: Cyclone IV Transceivers Architecture 1–81

Self Test Modes

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

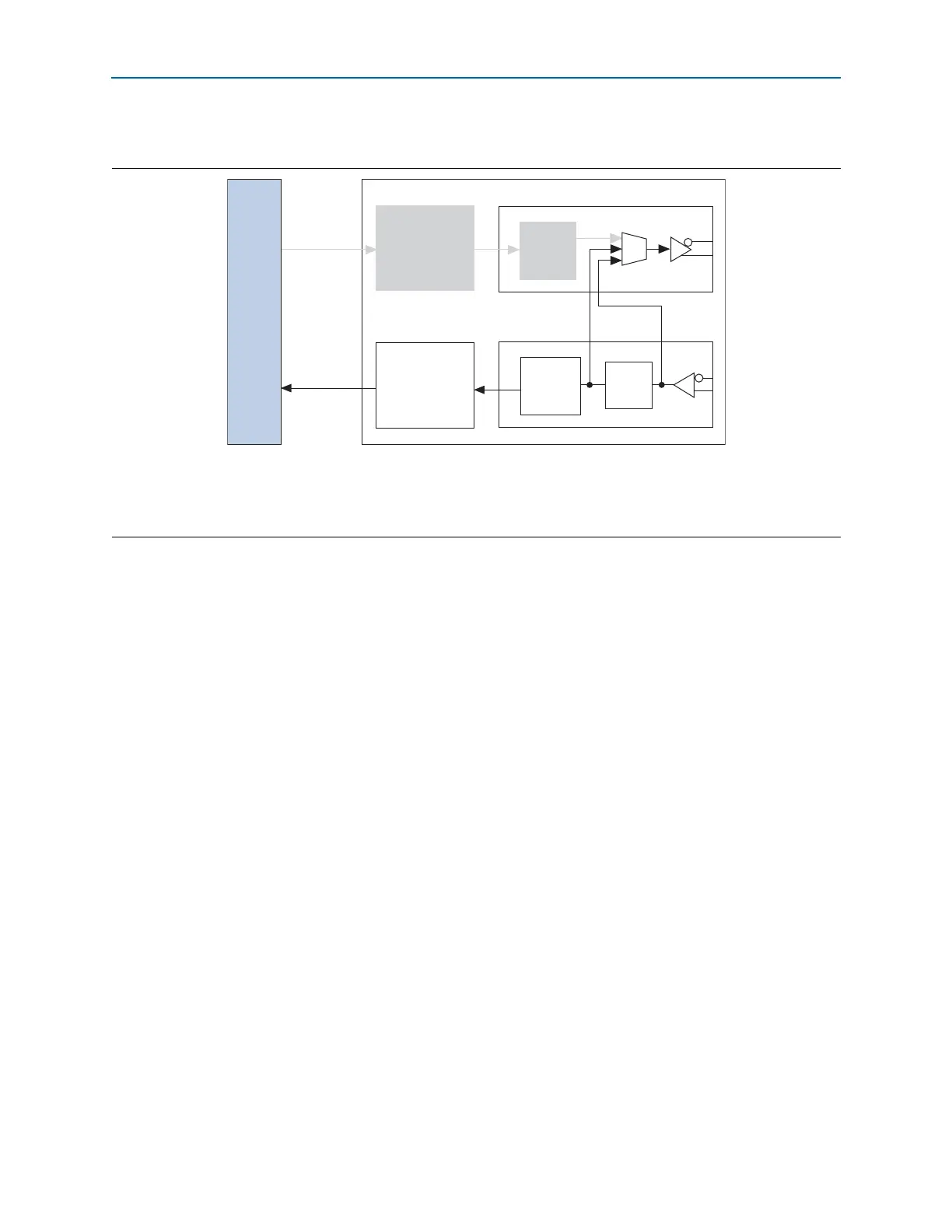

Figure 1–72 shows the two paths in reverse serial loopback mode.

Self Test Modes

Each transceiver channel in the Cyclone IV GX device contains modules for pattern

generator and verifier. Using these built-in features, you can verify the functionality of

the functional blocks in the transceiver channel without requiring user logic. The self

test functionality is provided as an optional mechanism for debugging transceiver

channels.

There are three types of supported pattern generators and verifiers:

■ Built-in self test (BIST) incremental data generator and verifier—test the complete

transmitter PCS and receiver PCS datapaths for bit errors with parallel loopback

before the PMA blocks.

■ Pseudo-random binary sequence (PRBS) generator and verifier—the PRBS

generator and verifier interface with the serializer and deserializer in the PMA

blocks. The advantage of using a PRBS data stream is that the randomness yields

an environment that stresses the transmission medium. In the data stream, you

can observe both random jitter and deterministic jitter using a time interval

analyzer, bit error rate tester, or oscilloscope.

■ High frequency and low frequency pattern generator—the high frequency

patterns generate alternate ones and zeros and the low frequency patterns

generate five ones and five zeroes. These patterns do not have a corresponding

verifier.

1 The self-test features are only supported in Basic mode.

Figure 1–72. Reverse Serial Loopback

(1)

Notes to Figure 1–72:

(1) Grayed-Out Blocks are Not Active in this mode.

(2) Post-CDR reverse serial loopback path.

(3) Pre-CDR reverse serial loopback path.

Tx PCS

Rx PCS

Tx PMA

Serializer

Rx PMA

Deserializer

To FPGA fabric

for verication

Transceiver

CDR

Tx PMA

(2) (3)

FPGA

Fabric

Loading...

Loading...