5–2 Chapter 5: Clock Networks and PLLs in Cyclone IV Devices

Clock Networks

Cyclone IV Device Handbook, October 2012 Altera Corporation

Volume 1

f For more information about the number of GCLK networks in each device density,

refer to the Cyclone IV FPGA Device Family Overview chapter.

GCLK Network

GCLKs drive throughout the entire device, feeding all device quadrants. All resources

in the device (I/O elements, logic array blocks (LABs), dedicated multiplier blocks,

and M9K memory blocks) can use GCLKs as clock sources. Use these clock network

resources for control signals, such as clock enables and clears fed by an external pin.

Internal logic can also drive GCLKs for internally generated GCLKs and

asynchronous clears, clock enables, or other control signals with high fan-out.

Tab le 5 –1 , Table 5–2 on page 5–4, and Table 5–3 on page 5–7 list the connectivity of the

clock sources to the GCLK networks.

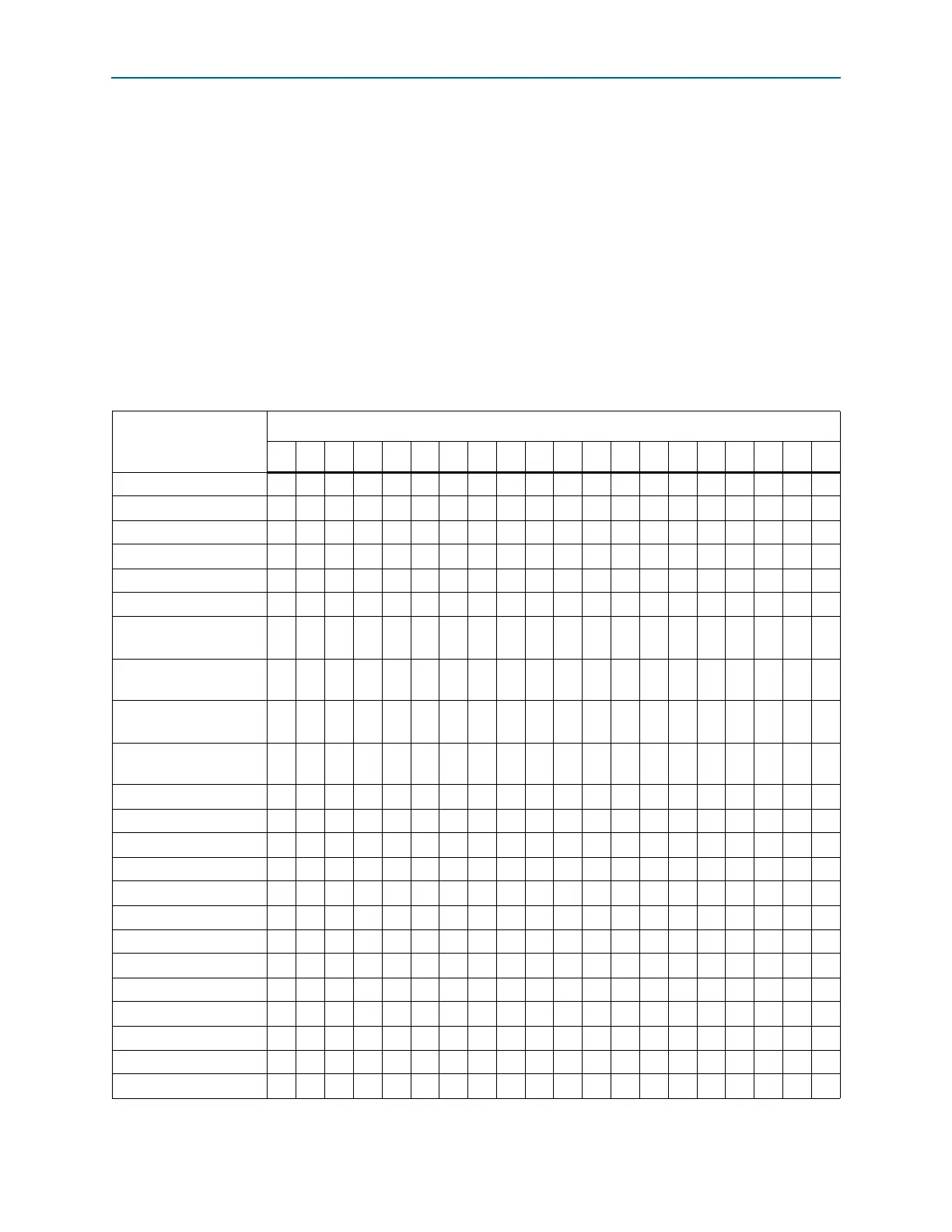

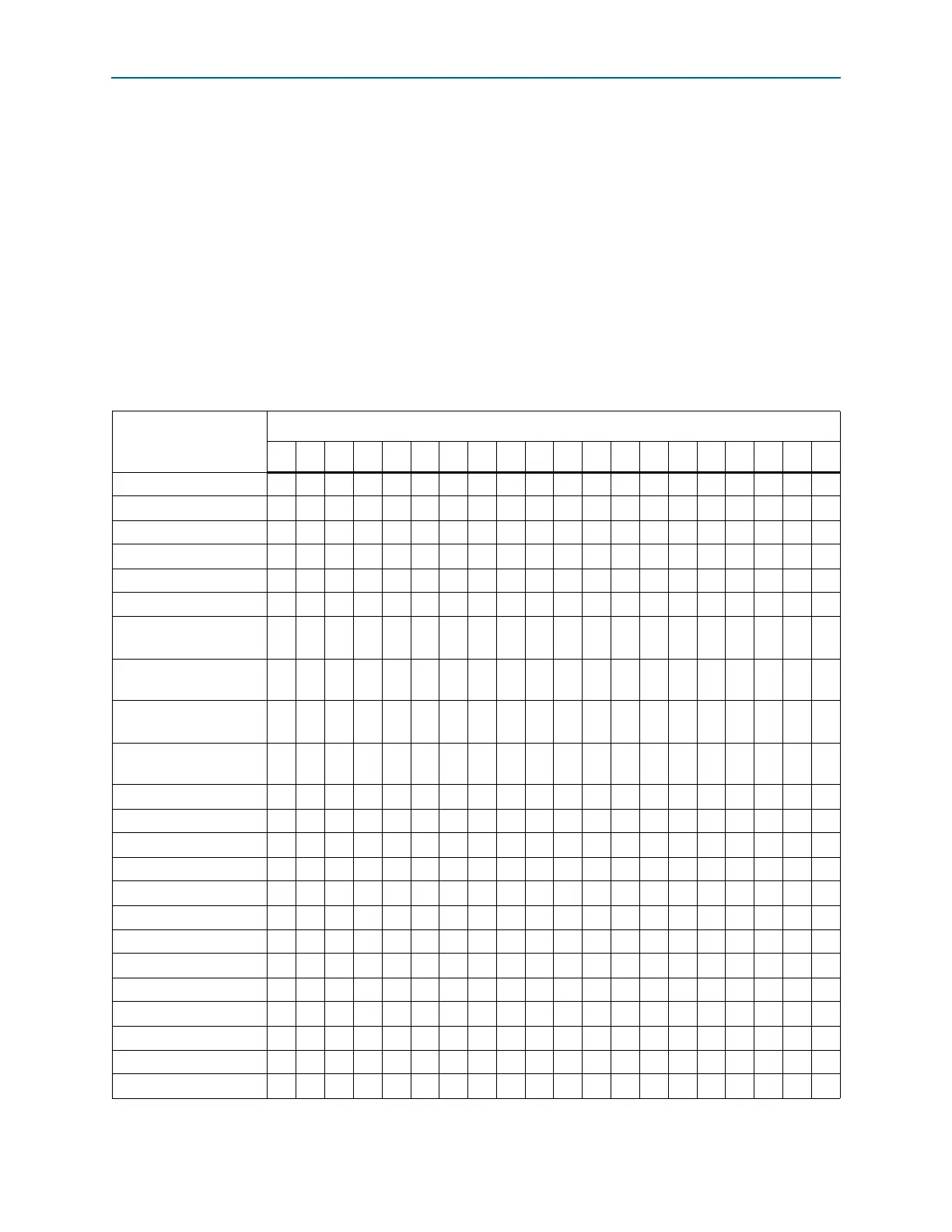

Table 5–1. GCLK Network Connections for EP4CGX15, EP4CGX22, and EP4CGX30

(1),

(2)

(Part 1 of 2)

GCLK Network Clock

Sources

GCLK Networks

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

CLK4/DIFFCLK_2n

—————v — v — v ——————————

CLK5/DIFFCLK_2p

——————vv————————————

CLK6/DIFFCLK_3n

——————v — vv——————————

CLK7/DIFFCLK_3p

—————v ——v ———————————

CLK8/DIFFCLK_5n

——————————v — v — v —————

CLK9/DIFFCLK_5p

———————————vv———————

CLK10/DIFFCLK_4n/RE

FCLK1n

———————————v — vv—————

CLK11/DIFFCLK_4p/RE

FCLK1p

——————————v ——v ——————

CLK12/DIFFCLK_7p/RE

FCLK0p

———————————————v — v — v

CLK13/DIFFCLK_7n/RE

FCLK0n

————————————————vv——

CLK14/DIFFCLK_6p

————————————————v — vv

CLK15/DIFFCLK_6n

———————————————v ——v —

PLL_1_C0

v ——v ———————————v ——v —

PLL_1_C1

— v ——v ———————————v ——v

PLL_1_C2

v — v ————————————v — v ——

PLL_1_C3

— v — v ————————————v — v —

PLL_1_C4

——v — v ————————————v — v

PLL_2_C0

v ——v ——————v ——v ——————

PLL_2_C1

— v ——v ——————v ——v —————

PLL_2_C2

v — v ———————v — v ———————

PLL_2_C3

— v — v ———————v — v ——————

PLL_2_C4

——v — v ———————v — v —————

PLL_3_C0

—————v ——v ——————v ——v —

Loading...

Loading...