Chapter 1: Cyclone IV Transceivers Architecture 1–47

Transceiver Functional Modes

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

The hard IP block supports 1, 2, or 4 initial lane configurations with a maximum

payload of 256 bytes at Gen1 frequency. The application interface is 64 bits with a data

width of 16 bits per channel running at up to 125 MHz. As a hard macro and a verified

block, it uses very few FPGA resources, while significantly reducing design risk and

the time required to achieve timing closure. It is compliant with the PCI Express Base

Specification 1.1. You do not have to pay a licensing fee to use this module.

Configuring the hard IP block requires using the PCI Express Compiler.

f For more information about the hard IP block, refer to the PCI Express Compiler User

Guide.

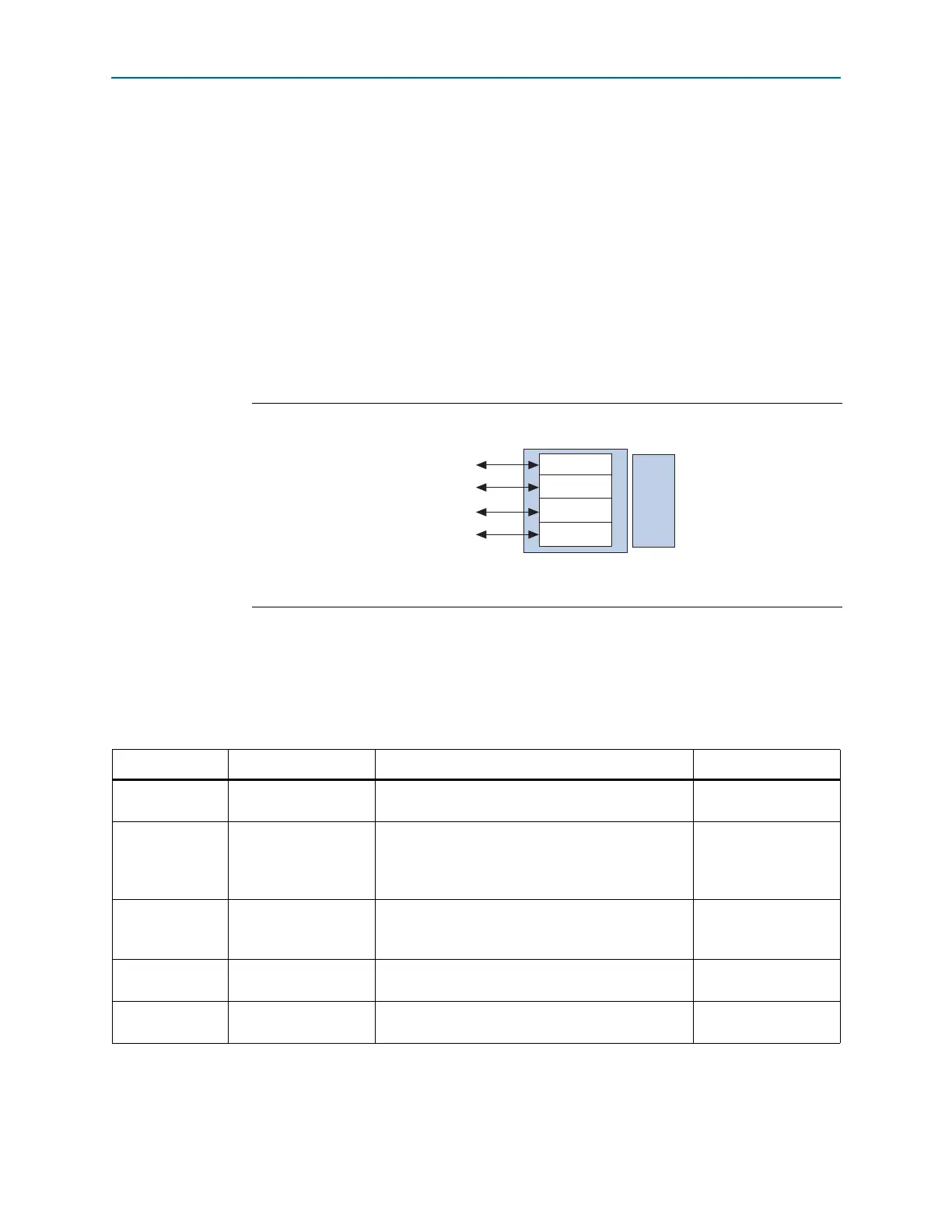

Figure 1–43 shows the lane placement requirements when implementing PCIe with

hard IP block.

Transceiver Functional Modes

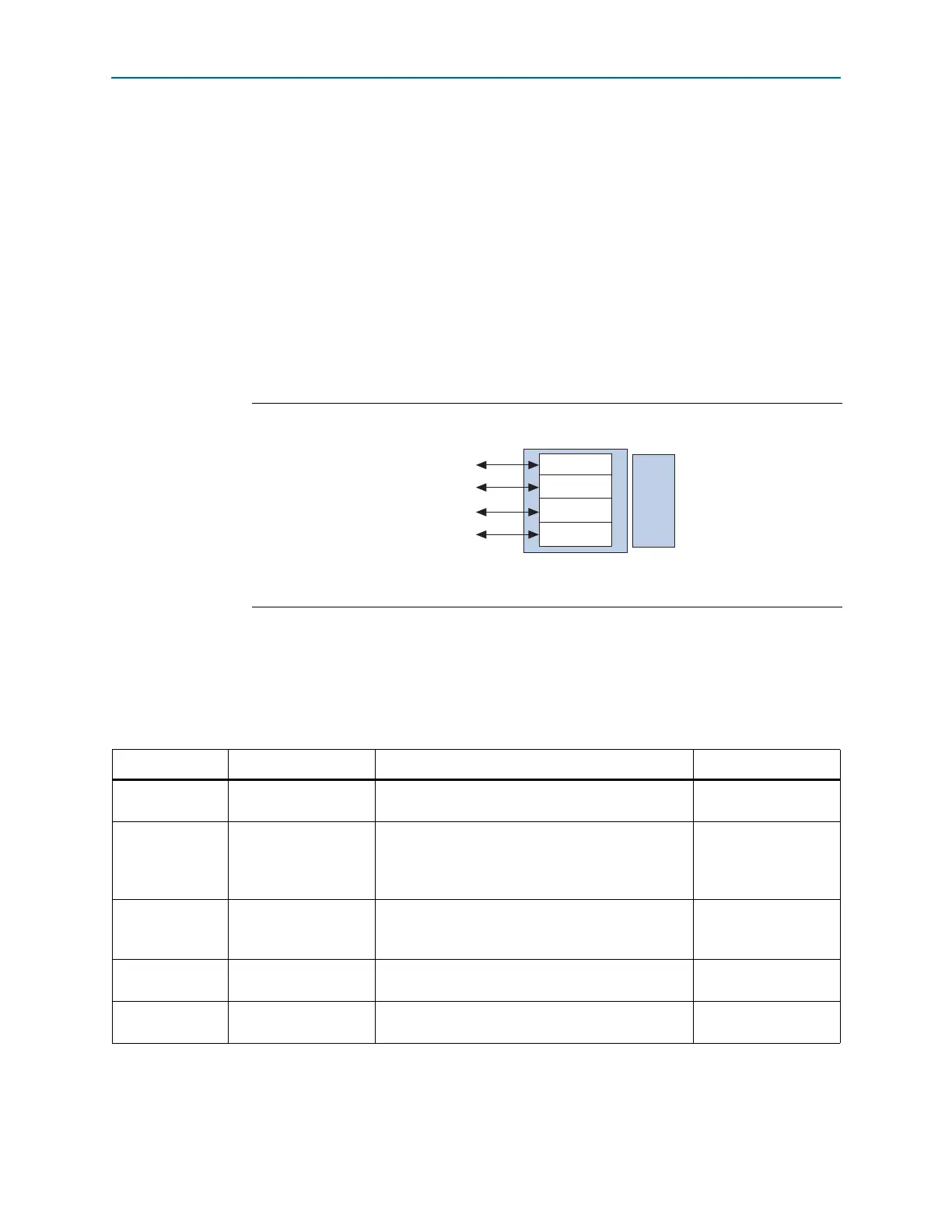

The Cyclone IV GX transceiver supports the functional modes as listed in Table 1–14

for protocol implementation.

Figure 1–43. PCIe with Hard IP Block Lane Placement Requirements

(1)

Note to Figure 1–43:

(1) Applicable for PCIe ×1, ×2, and ×4 implementations with hard IP blocks only.

Channel 3

Channel 2

Channel 1

Channel 0

PCIe Lane 3

PCIe Lane 2

PCIe Lane 1

PCIe Lane 0

PCIe

hard IP

Transceiver

Block GXBL0

Table 1–14. Transceiver Functional Modes for Protocol Implementation (Part 1 of 2)

Functional Mode Protocol Key Feature Reference

Basic

Proprietary, SATA, V-

by-One, Display Port

Low latency PCS, transmitter in electrical idle, signal

detect at receiver, wider spread asynchronous SSC

“Basic Mode” on

page 1–48

PCI Express

(PIPE)

PCIe Gen1 with PIPE

Interface

PIPE ports, receiver detect, transmitter in electrical

idle, electrical idle inference, signal detect at receiver,

fast recovery, protocol-compliant word aligner and

rate match FIFO, synchronous SSC

“PCI Express (PIPE)

Mode” on page 1–52

GIGE GbE

Running disparity preservation, protocol-compliant

word aligner, recovered clock port for applications

such as Synchronous Ethernet

“GIGE Mode” on

page 1–59

Serial RapidIO SRIO Protocol-compliant word aligner

“Serial RapidIO Mode”

on page 1–64

XAUI XAUI

Deskew FIFO, protocol-compliant word aligner and

rate match FIFO

“XAUI Mode” on

page 1–67

Loading...

Loading...