8–30 Chapter 8: Configuration and Remote System Upgrades in Cyclone IV Devices

Configuration

Cyclone IV Device Handbook, May 2013 Altera Corporation

Volume 1

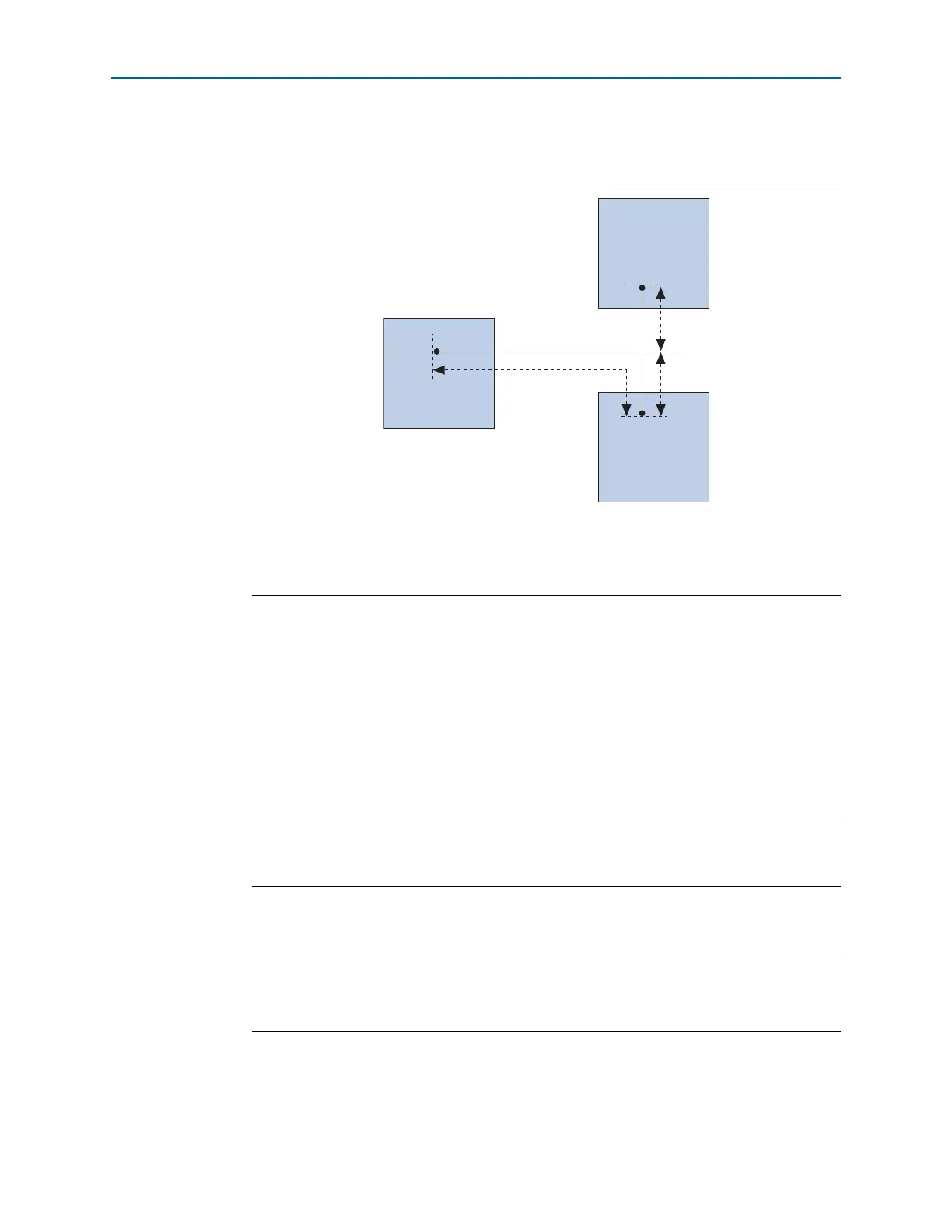

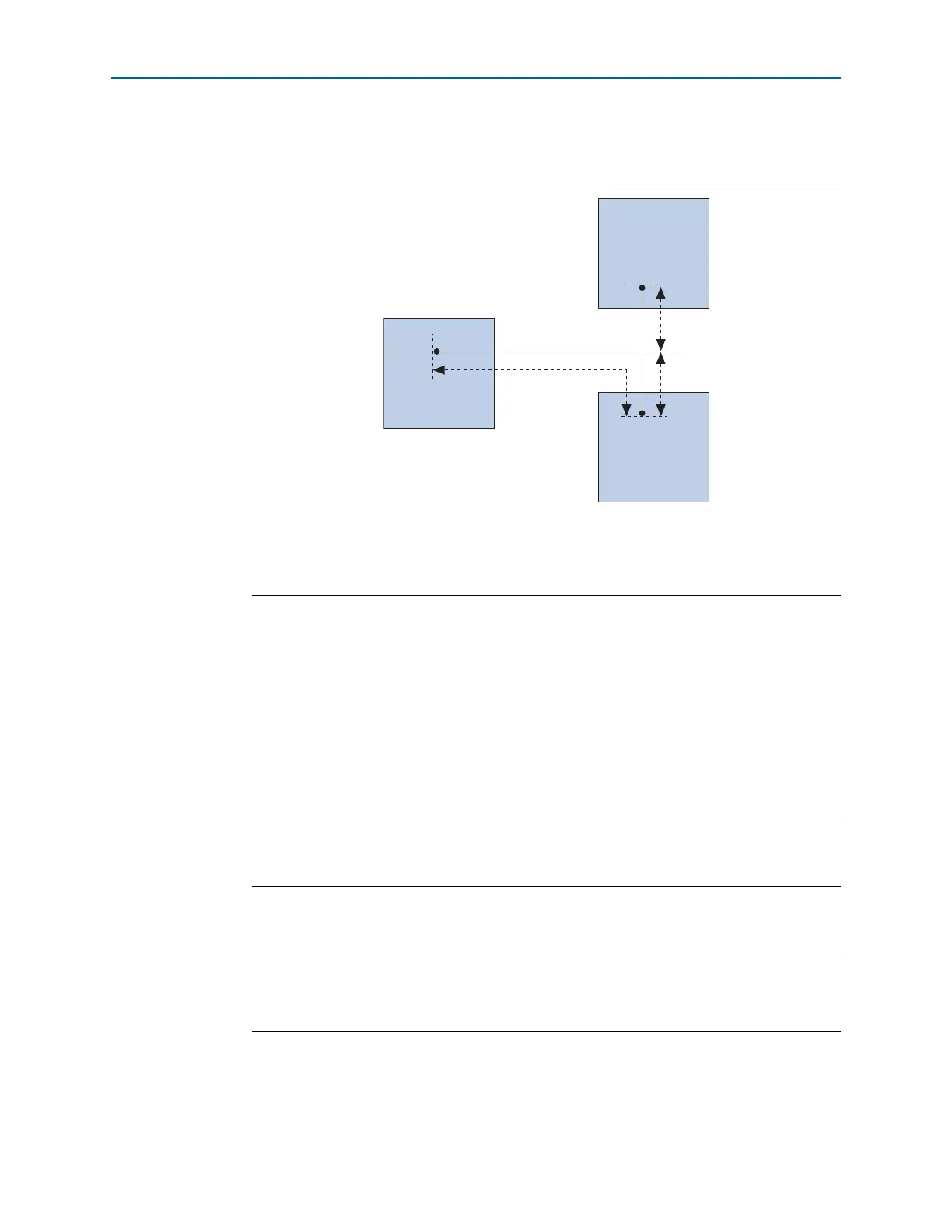

Figure 8–11 shows the recommended balanced star routing for multiple bus master

interfaces to minimize signal integrity issues.

Estimating AP Configuration Time

AP configuration time is dominated by the time it takes to transfer data from the

parallel flash to Cyclone IV E devices. This parallel interface is clocked by the

Cyclone IV E

DCLK

output (generated from an internal oscillator). The

DCLK

minimum

frequency when using the 40-MHz oscillator is 20 MHz (50 ns). In word-wide cascade

programming, the

DATA[15..0]

bus transfers a 16-bit word and essentially cuts

configuration time to approximately 1/16 of the AS configuration time. Equation 8–4

and Equation 8–5 show the configuration time calculations.

Figure 8–11. Balanced Star Routing

Notes to Figure 8–11:

(1) Altera recommends that M does not exceed 6 inches, as listed in Table 8–11 on page 8–28.

(2) Altera recommends using a balanced star routing. Keep the N length equal and as short as possible to minimize

reflection noise from the transmission line. The M length is applicable for this setup.

Equation 8–4.

Equation 8–5.

External

Master Device

Cyclone IV E

Master Device

Micron Flash

DCLK

M (1)

N (2)

N (2)

Size

maximum DCLK period

16 bits per DCLK cycle

----- ----------------- ------------- ----------------- ------------

estimated maximum configuration time =

9,600,000 bits

50 ns

16 bit

----- ---------

30 ms=

Loading...

Loading...