9–4 Chapter 9: SEU Mitigation in Cyclone IV Devices

Error Detection Block

Cyclone IV Device Handbook, May 2013 Altera Corporation

Volume 1

1 WYSIWYG is an optimization technique that performs optimization on a VQM

(Verilog Quartus Mapping) netlist in the Quartus II software.

Error Detection Block

Tab le 9 –3 lists the types of CRC detection to check the configuration bits.

This section focuses on the first type—the 32-bit CRC when the device is in user

mode.

Error Detection Registers

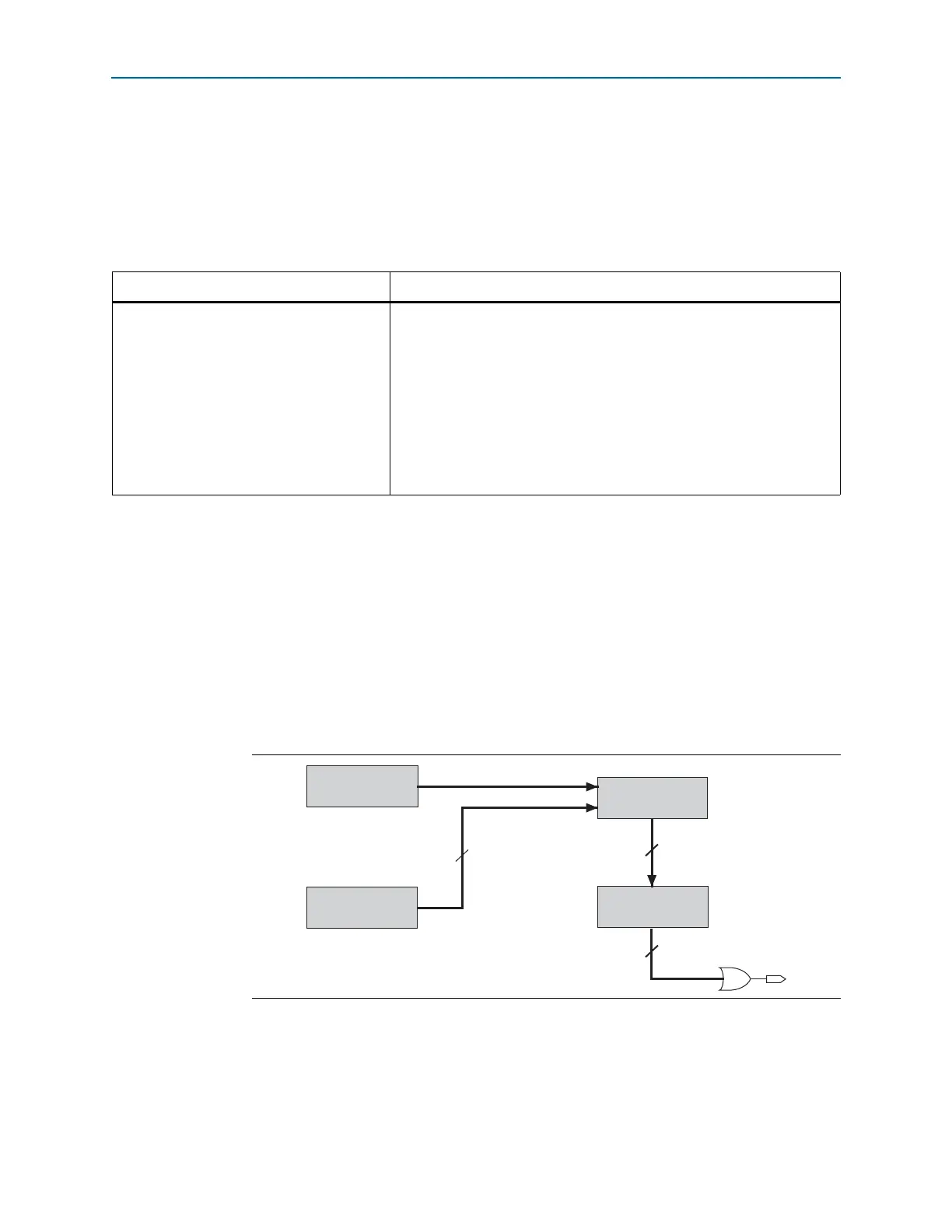

There are two sets of 32-bit registers in the error detection circuitry that store the

computed CRC signature and pre-calculated CRC value. A non-zero value on the

signature register causes the

CRC_ERROR

pin to set high.

Figure 9–1 shows the block diagram of the error detection block and the two related

32-bit registers: the signature register and the storage register.

Table 9–3. Types of CRC Detection to Check the Configuration Bits

First Type of CRC Detection Second Type of CRC Detection

■ CRAM error checking ability (32-bit CRC)

during user mode, for use by the

CRC_ERROR

pin.

■ There is only one 32-bit CRC value. This

value covers all the CRAM data.

■ 16-bit CRC embedded in every configuration data frame.

■ During configuration, after a frame of data is loaded into the device, the

pre-computed CRC is shifted into the CRC circuitry.

■ Simultaneously, the CRC value for the data frame shifted-in is calculated.

If the pre-computed CRC and calculated CRC values do not match,

nSTATUS

is set low.

■ Every data frame has a 16-bit CRC. Therefore, there are many 16-bit CRC

values for the whole configuration bit stream.

■ Every device has a different length of configuration data frame.

Figure 9–1. Error Detection Block Diagram

Control Signals

Error Detection

State Machine

32-bit Storage

Register

Compute & Compare

CRC

32-bit Signature

Register

32

32

32

Loading...

Loading...