1–24 Chapter 1: Cyclone IV Device Datasheet

Switching Characteristics

Cyclone IV Device Handbook, December 2016 Altera Corporation

Volume 3

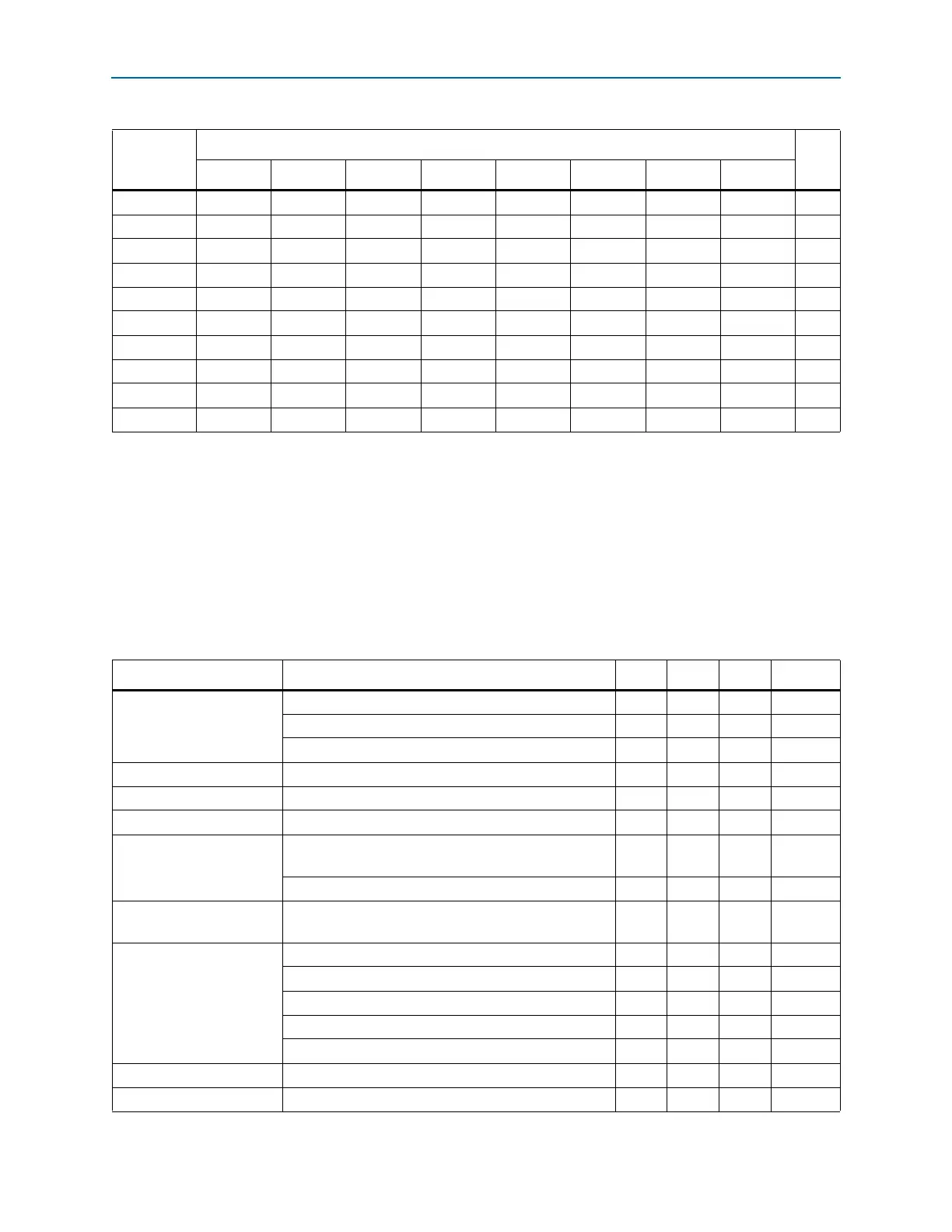

PLL Specifications

Table 1–25 lists the PLL specifications for Cyclone IV devices when operating in the

commercial junction temperature range (0°C to 85°C), the industrial junction

temperature range (–40°C to 100°C), the extended industrial junction temperature

range (–40°C to 125°C), and the automotive junction temperature range (–40°C to

125°C). For more information about the PLL block, refer to “Glossary” on page 1–37.

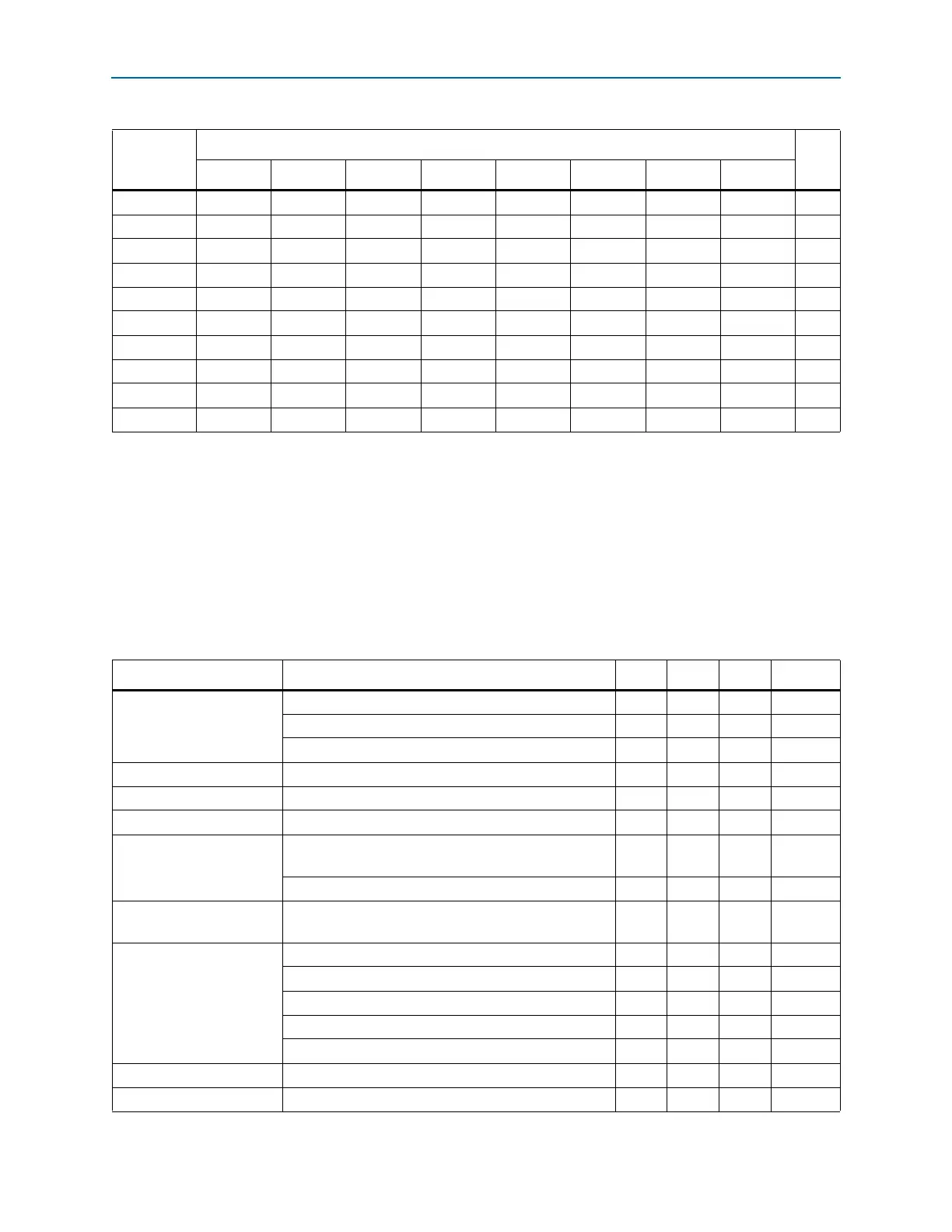

EP4CE55 500 437.5 402 362 265 437.5 362 — MHz

EP4CE75 500 437.5 402 362 265 437.5 362 — MHz

EP4CE115 — 437.5 402 362 265 437.5 362 — MHz

EP4CGX15 500 437.5 402 — — 437.5 — — MHz

EP4CGX22 500 437.5 402 — — 437.5 — — MHz

EP4CGX30 500 437.5 402 — — 437.5 — — MHz

EP4CGX50 500 437.5 402 — — 437.5 — — MHz

EP4CGX75 500 437.5 402 — — 437.5 — — MHz

EP4CGX110 500 437.5 402 — — 437.5 — — MHz

EP4CGX150 500 437.5 402 — — 437.5 — — MHz

Note to Table 1–24:

(1) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades.

Table 1–24. Clock Tree Performance for Cyclone IV Devices (Part 2 of 2)

Device

Performance

Unit

C6 C7 C8 C8L

(1)

C9L

(1)

I7 I8L

(1)

A7

Table 1–25. PLL Specifications for Cyclone IV Devices

(1),

(2)

(Part 1 of 2)

Symbol Parameter Min Typ Max Unit

f

IN

(3)

Input clock frequency (–6, –7, –8 speed grades) 5 — 472.5 MHz

Input clock frequency (–8L speed grade) 5 — 362 MHz

Input clock frequency (–9L speed grade) 5 — 265 MHz

f

INPFD

PFD input frequency 5 — 325 MHz

f

VCO

(4)

PLL internal VCO operating range 600 — 1300 MHz

f

INDUTY

Input clock duty cycle 40 — 60 %

t

INJITTER_CCJ

(5)

Input clock cycle-to-cycle jitter

F

REF

100 MHz

— — 0.15 UI

F

REF

< 100 MHz — — ±750 ps

f

OUT_EXT

(external clock

output)

(3)

PLL output frequency — — 472.5 MHz

f

OUT

(to global clock)

PLL output frequency (–6 speed grade) — — 472.5 MHz

PLL output frequency (–7 speed grade) — — 450 MHz

PLL output frequency (–8 speed grade) — — 402.5 MHz

PLL output frequency (–8L speed grade) — — 362 MHz

PLL output frequency (–9L speed grade) — — 265 MHz

t

OUTDUTY

Duty cycle for external clock output (when set to 50%) 45 50 55 %

t

LOCK

Time required to lock from end of device configuration — — 1 ms

Loading...

Loading...