2–2 Chapter 2: Logic Elements and Logic Array Blocks in Cyclone IV Devices

Logic Elements

Cyclone IV Device Handbook, November 2009 Altera Corporation

Volume 1

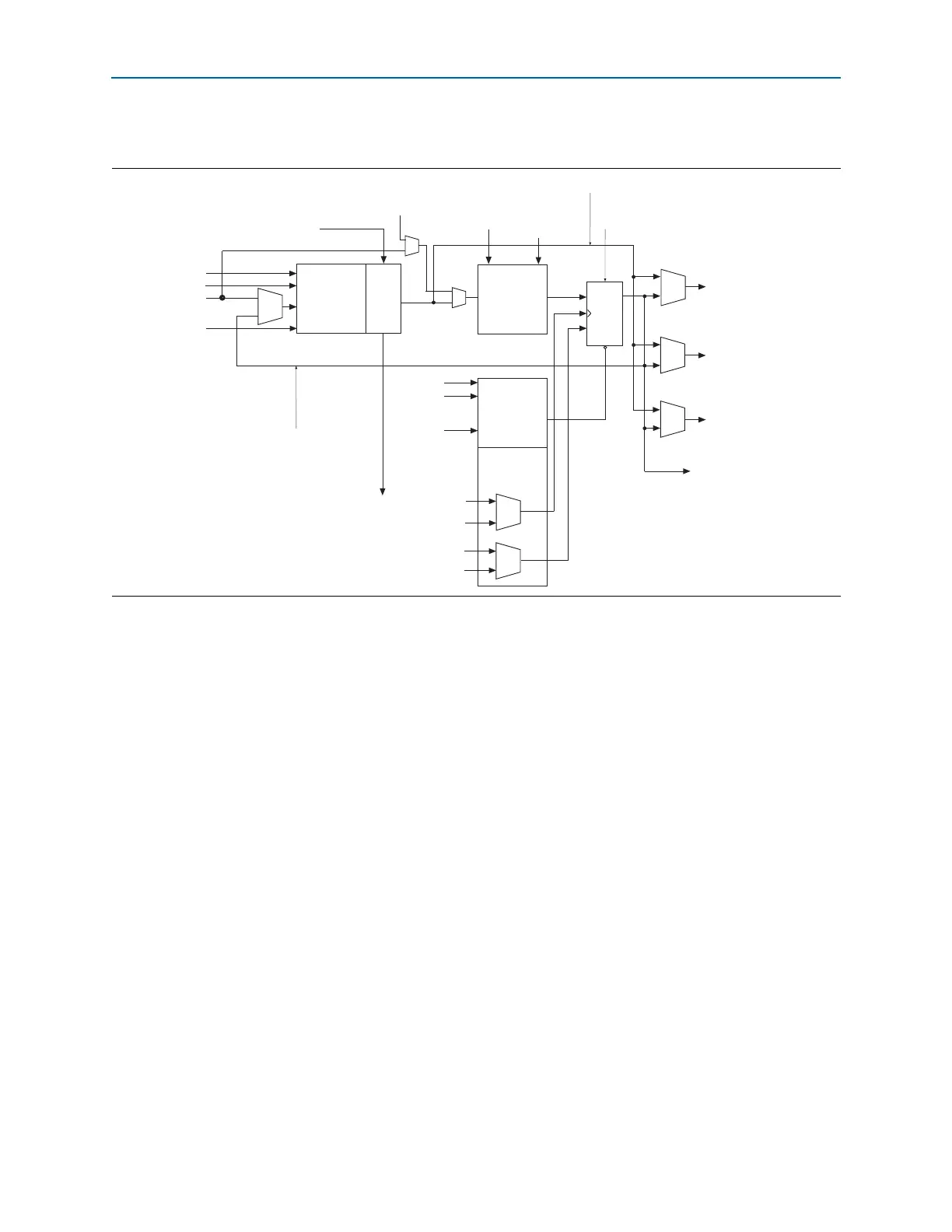

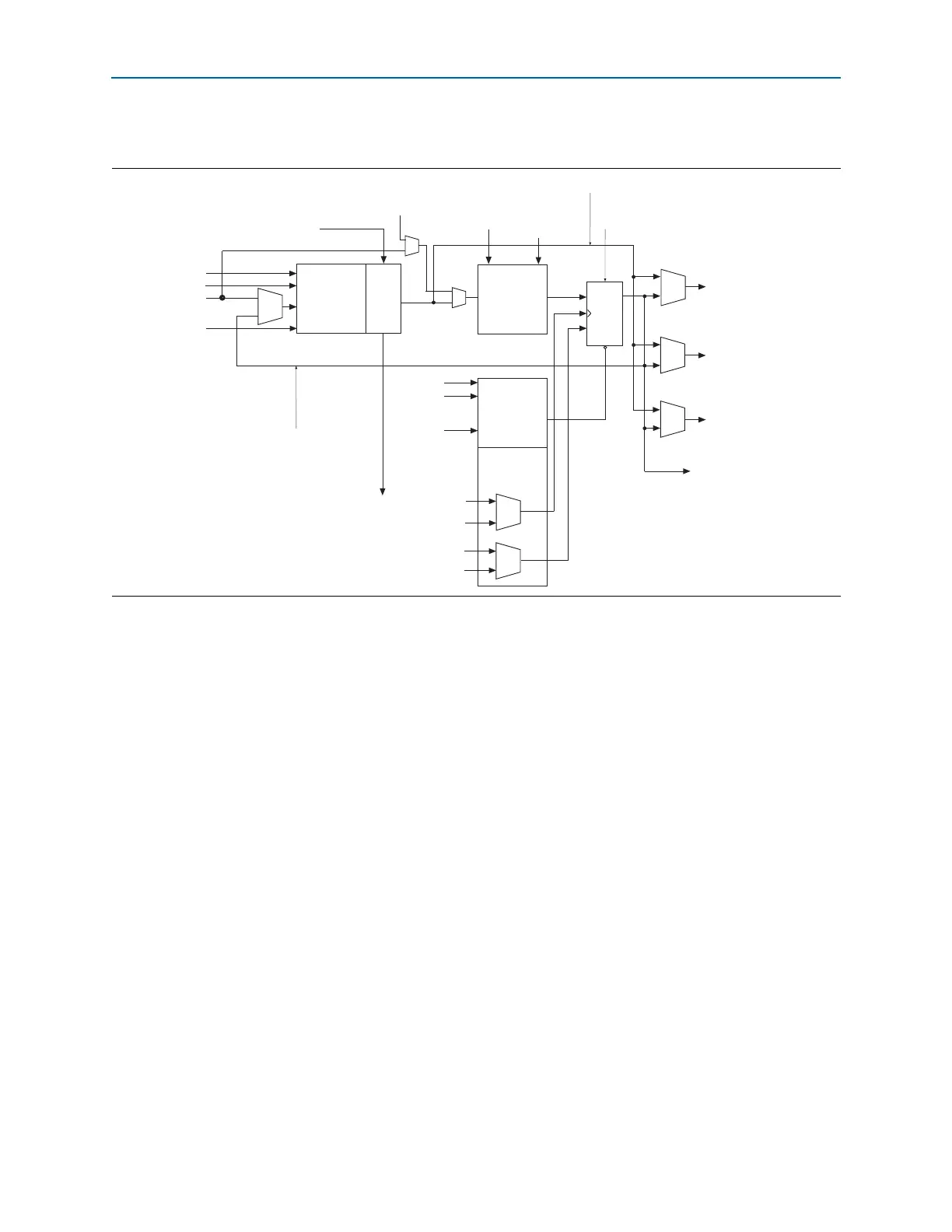

Figure 2–1 shows the LEs for Cyclone IV devices.

LE Features

You can configure the programmable register of each LE for D, T, JK, or SR flipflop

operation. Each register has data, clock, clock enable, and clear inputs. Signals that

use the global clock network, general-purpose I/O pins, or any internal logic can

drive the clock and clear control signals of the register. Either general-purpose I/O

pins or the internal logic can drive the clock enable. For combinational functions, the

LUT output bypasses the register and drives directly to the LE outputs.

Each LE has three outputs that drive the local, row, and column routing resources. The

LUT or register output independently drives these three outputs. Two LE outputs

drive the column or row and direct link routing connections, while one LE drives the

local interconnect resources. This allows the LUT to drive one output while the

register drives another output. This feature, called register packing, improves device

utilization because the device can use the register and the LUT for unrelated

functions. The LAB-wide synchronous load control signal is not available when using

register packing. For more information about the synchronous load control signal,

refer to “LAB Control Signals” on page 2–6.

The register feedback mode allows the register output to feed back into the LUT of the

same LE to ensure that the register is packed with its own fan-out LUT, providing

another mechanism for improved fitting. The LE can also drive out registered and

unregistered versions of the LUT output.

Figure 2–1. Cyclone IV Device LEs

Row, Column,

And Direct Link

Routing

data 1

data 2

data 3

data 4

labclr1

labclr2

Chip-Wide

Reset

(DEV_CLRn)

labclk1

labclk2

labclkena1

labclkena2

LE Carry-In

LAB-Wide

Synchronous

Load

LAB-Wide

Synchronous

Clear

Row, Column,

And Direct Link

Routing

Local

Routing

Register Chain

Output

Register Bypass

Programmable

Register

Register Chain

Routing from

previous LE

LE Carry-Out

Register Feedback

Synchronous

Load and

Clear Logic

Carry

Chain

Look-Up Table

(LUT)

Asynchronous

Clear Logic

Clock &

Clock Enable

Select

D

Q

ENA

CLRN

Loading...

Loading...