9–6 Chapter 9: SEU Mitigation in Cyclone IV Devices

Software Support

Cyclone IV Device Handbook, May 2013 Altera Corporation

Volume 1

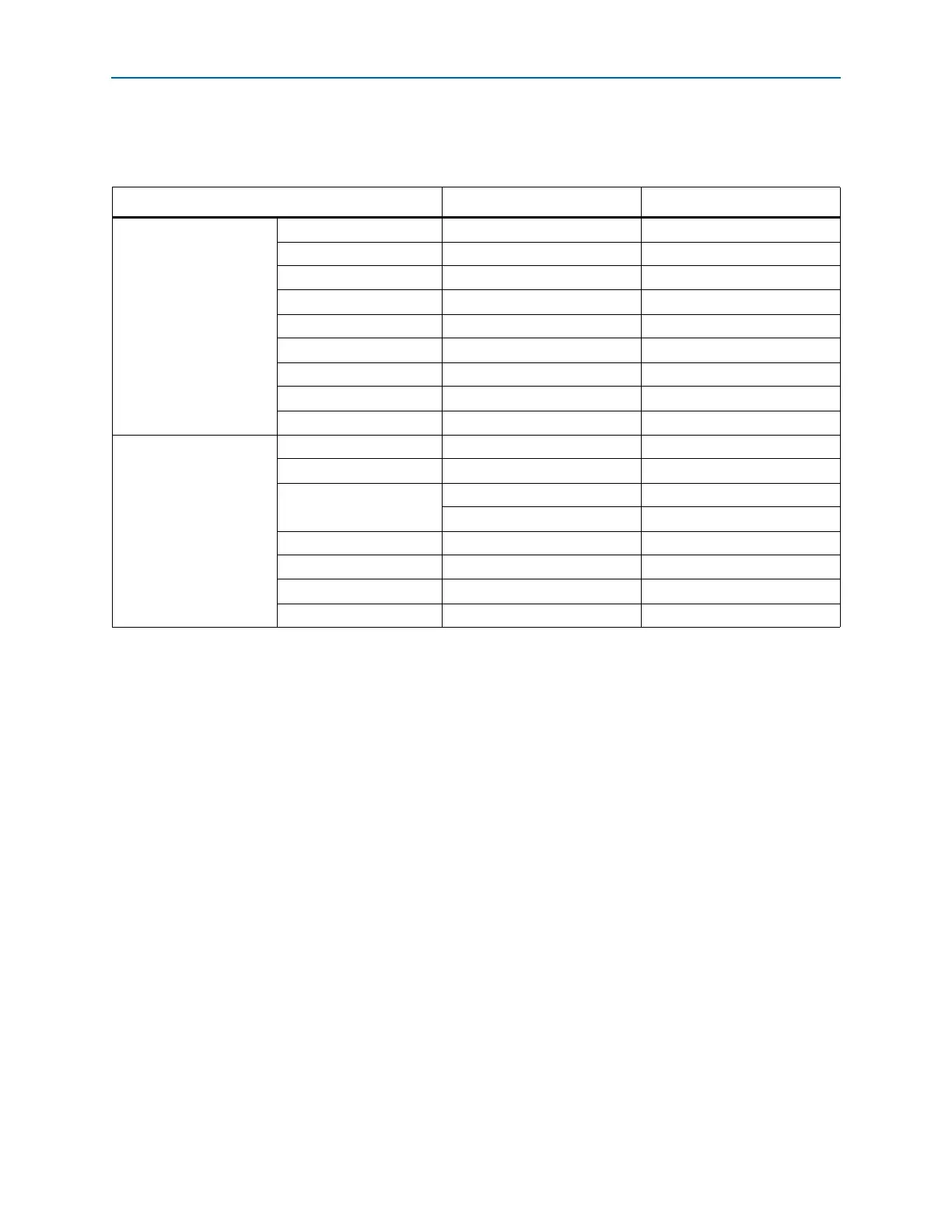

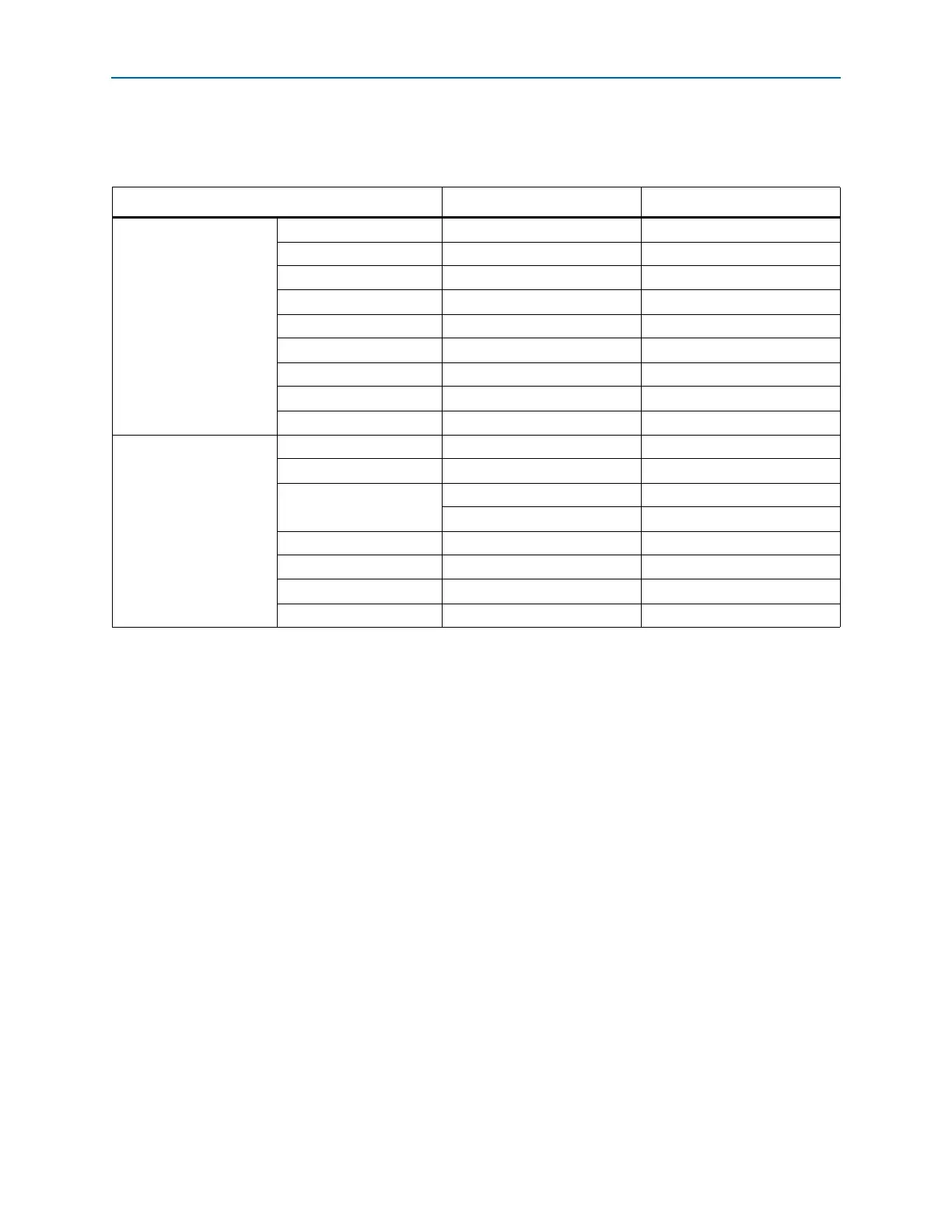

Tab le 9 –6 lists the estimated time for each CRC calculation with minimum and

maximum clock frequencies for Cyclone IV devices.

Software Support

Enabling the CRC error detection feature in the Quartus II software generates the

CRC

_

ERROR

output to the optional dual purpose

CRC

_

ERROR

pin.

To enable the error detection feature using CRC, perform the following steps:

1. Open the Quartus II software and load a project using Cyclone IV devices.

2. On the Assignments menu, click Settings. The Settings dialog box appears.

3. In the Category list, select Device. The Device page appears.

4. Click Device and Pin Options. The Device and Pin Options dialog box appears as

shown in Figure 9–2.

5. In the Device and Pin Options dialog box, click the Error Detection CRC tab.

6. Turn on Enable error detection CRC.

7. In the Divide error check frequency by box, enter a valid divisor as documented

in Table 9–5 on page 9–5.

Table 9–6. CRC Calculation Time

Device Minimum Time (ms)

(1)

Maximum Time (s)

(2)

Cyclone IV E

EP4CE6

(3)

5 2.29

EP4CE10

(3)

5 2.29

EP4CE15

(3)

73.17

EP4CE22

(3)

9 4.51

EP4CE30

(3)

15 7.48

EP4CE40

(3)

15 7.48

EP4CE55

(3)

23 11.77

EP4CE75

(3)

31 15.81

EP4CE115

(3)

45 22.67

Cyclone IV GX

EP4CGX15 6 2.93

EP4CGX22 12 5.95

EP4CGX30

12 5.95

34

(4)

17.34

(4)

EP4CGX50 34 17.34

EP4CGX75 34 17.34

EP4CGX110 62 31.27

EP4CGX150 62 31.27

Notes to Table 9–6:

(1) The minimum time corresponds to the maximum error detection clock frequency and may vary with different processes, voltages, and

temperatures (PVT).

(2) The maximum time corresponds to the minimum error detection clock frequency and may vary with different PVT.

(3) Only applicable for device with 1.2-V core voltage

(4) Only applicable for the F484 device package.

Loading...

Loading...