Chapter 6: I/O Features in Cyclone IV Devices 6–13

Termination Scheme for I/O Standards

March 2016 Altera Corporation Cyclone IV Device Handbook,

Volume 1

Cyclone IV devices support PCI and PCI-X I/O standards at 3.0-V V

CCIO

. The 3.0-V

PCI and PCI-X I/O are fully compatible for direct interfacing with 3.3-V PCI systems

without requiring any additional components. The 3.0-V PCI and PCI-X outputs meet

the V

IH

and V

IL

requirements of 3.3-V PCI and PCI-X inputs with sufficient noise

margin.

f For more information about the 3.3/3.0/2.5-V LVTTL & LVCMOS multivolt I/O

support, refer to AN 447: Interfacing Cyclone III and Cyclone IV Devices with 3.3/3.0/2.5-V

LVTTL/LVCMOS I/O Systems.

Termination Scheme for I/O Standards

This section describes recommended termination schemes for voltage-referenced and

differential I/O standards.

The 3.3-V LVTTL, 3.0-V LVTTL and LVCMOS, 2.5-V LVTTL and LVCMOS, 1.8-V

LVTTL and LVCMOS, 1.5-V LVCMOS, 1.2-V LVCMOS, 3.0-V PCI, and PCI-X

I/O standards do not specify a recommended termination scheme per the JEDEC

standard

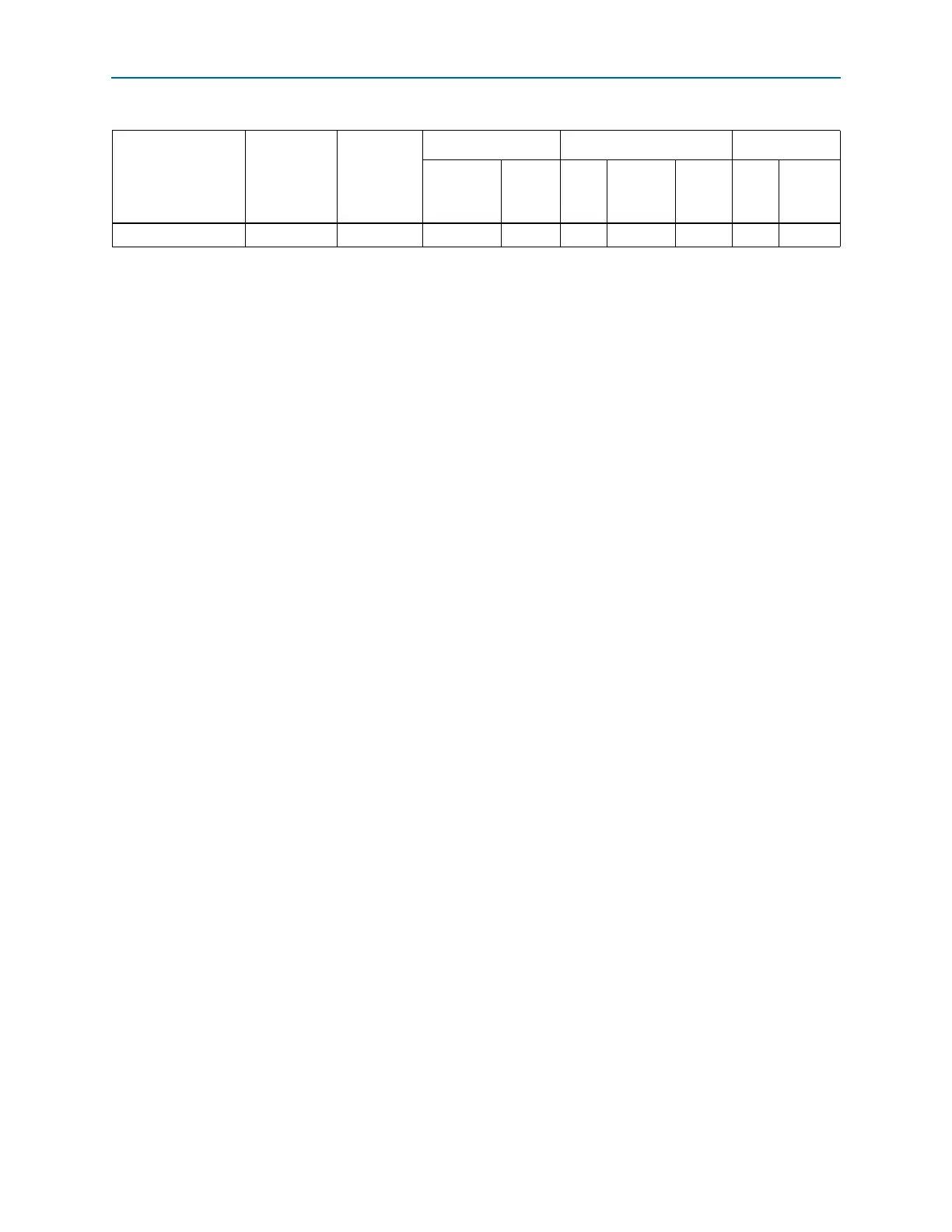

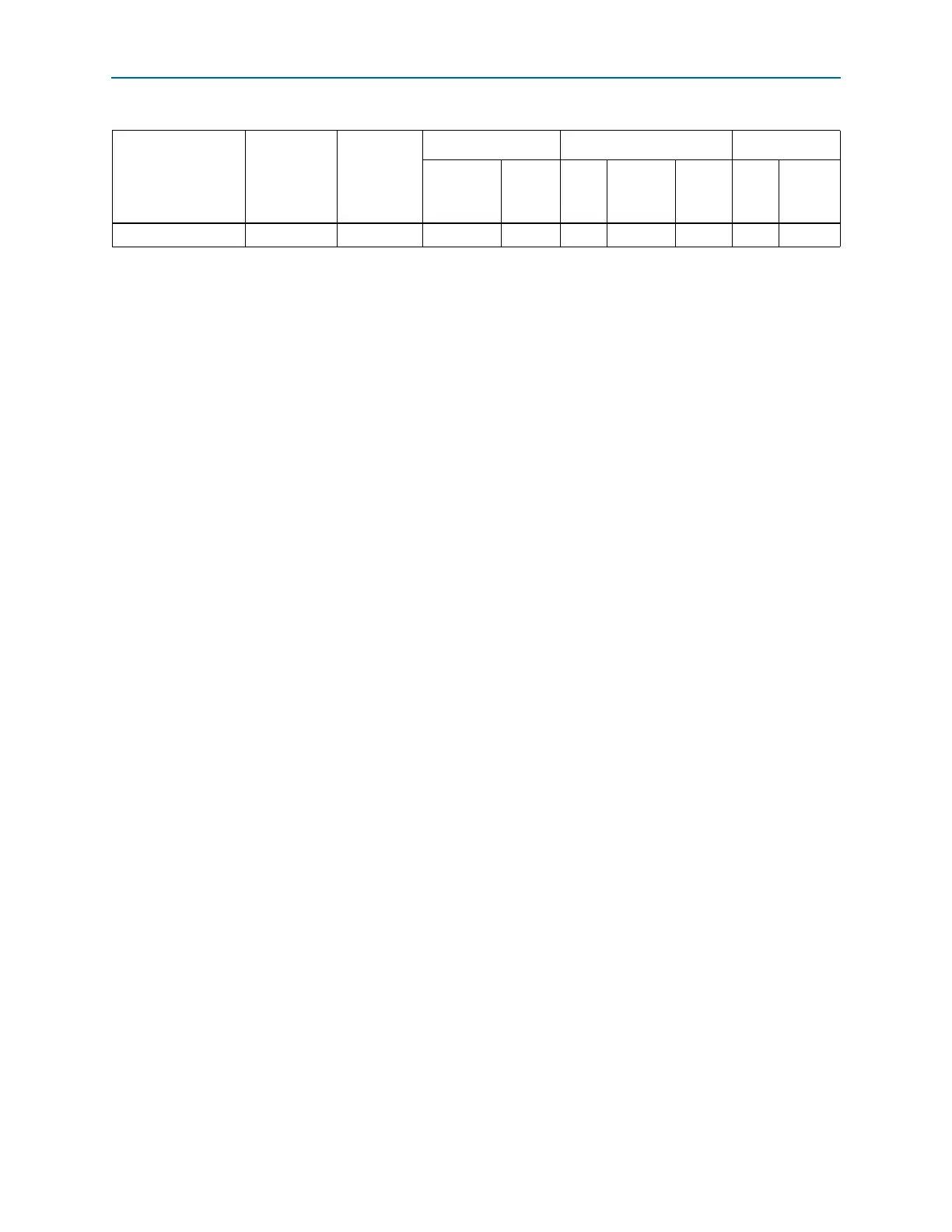

LVPECL

(7)

Differential — 2.5 — v ——v —

Notes to Table 6–3:

(1) Cyclone IV GX devices only support right I/O pins.

(2) The PCI-clamp diode must be enabled for 3.3-V/3.0-V LVTTL/LVCMOS.

(3) The Cyclone IV architecture supports the MultiVolt I/O interface feature that allows Cyclone IV devices in all packages to interface with I/O

systems that have different supply voltages.

(4) Cyclone IV GX devices do not support 1.2-V V

CCIO

in banks 3 and 9. I/O pins in bank 9 are dual-purpose I/O pins that are used as configuration

or GPIO pins. Configuration scheme is not support at 1.2 V, therefore bank 9 can not be powered up at 1.2-V V

CCIO

.

(5) Differential HSTL and SSTL outputs use two single-ended outputs with the second output programmed as inverted. Differential HSTL and SSTL

inputs treat differential inputs as two single-ended HSTL and SSTL inputs and only decode one of them. Differential HSTL and SSTL are only

supported on CLK pins.

(6) PPDS, mini-LVDS, and RSDS are only supported on output pins.

(7) LVPECL is only supported on clock inputs.

(8) Bus LVDS (BLVDS) output uses two single-ended outputs with the second output programmed as inverted. BLVDS input uses LVDS input

buffer.

(9) 1.2-V HSTL input is supported at both column and row I/Os regardless of Class I or Class II.

(10) True LVDS, RSDS, and mini-LVDS I/O standards are supported in left and right I/O pins, while emulated LVDS, RSDS, and mini-LVDS I/O

standards are supported in the top, bottom, and right I/O pins.

Table 6–3. Cyclone IV Devices Supported I/O Standards and Constraints (Part 3 of 3)

I/O Standard Type

Standard

Support

V

CCIO

Level (in V) Column I/O Pins Row I/O Pins

(1)

Input Output

CLK,

DQS

PLL_OUT

User

I/O

Pins

CLK,

DQS

User I/O

Pins

Loading...

Loading...