5–24 Chapter 5: Clock Networks and PLLs in Cyclone IV Devices

Clock Feedback Modes

Cyclone IV Device Handbook, October 2012 Altera Corporation

Volume 1

No Compensation Mode

In no compensation mode, the PLL does not compensate for any clock networks. This

provides better jitter performance because clock feedback into the PFD does not pass

through as much circuitry. Both the PLL internal and external clock outputs are phase

shifted with respect to the PLL clock input.

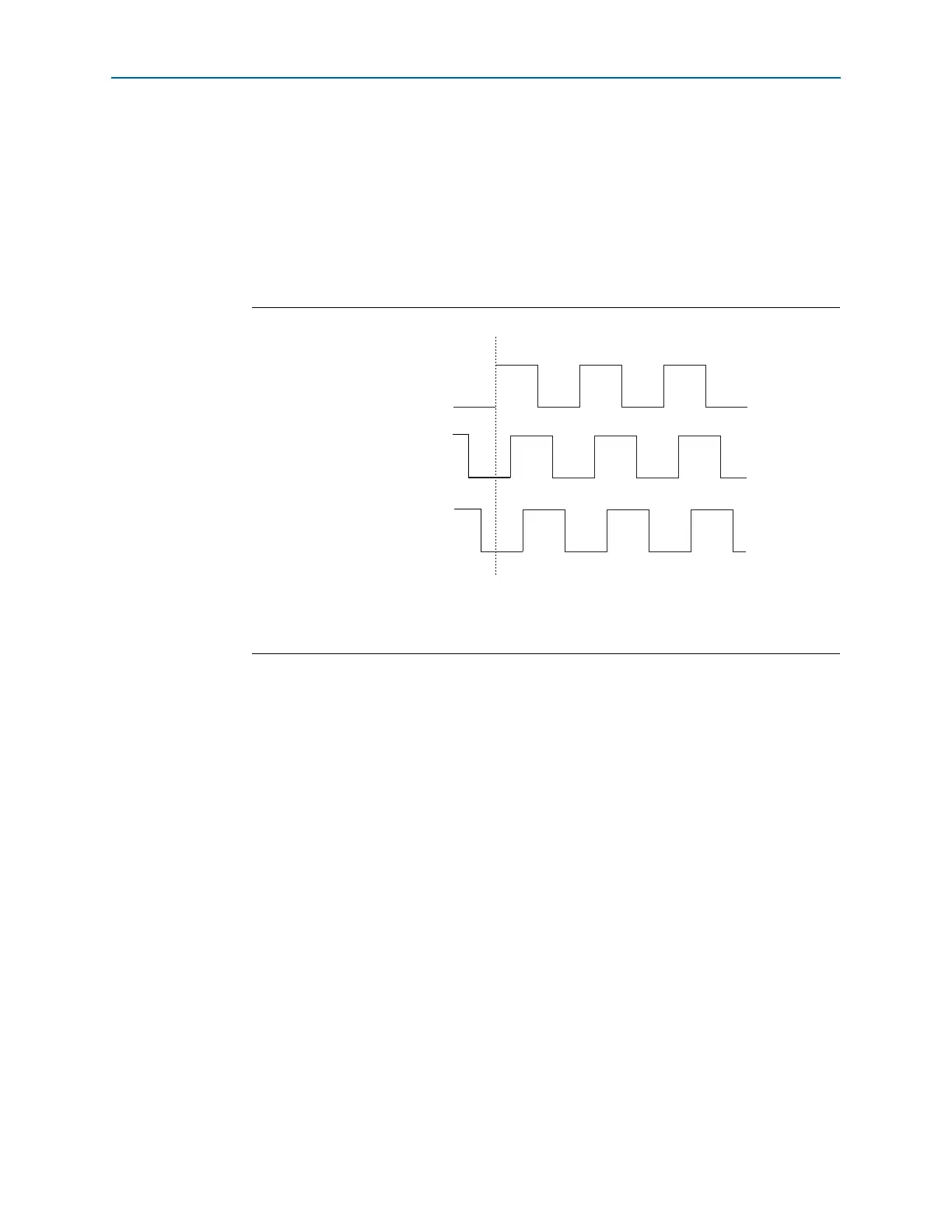

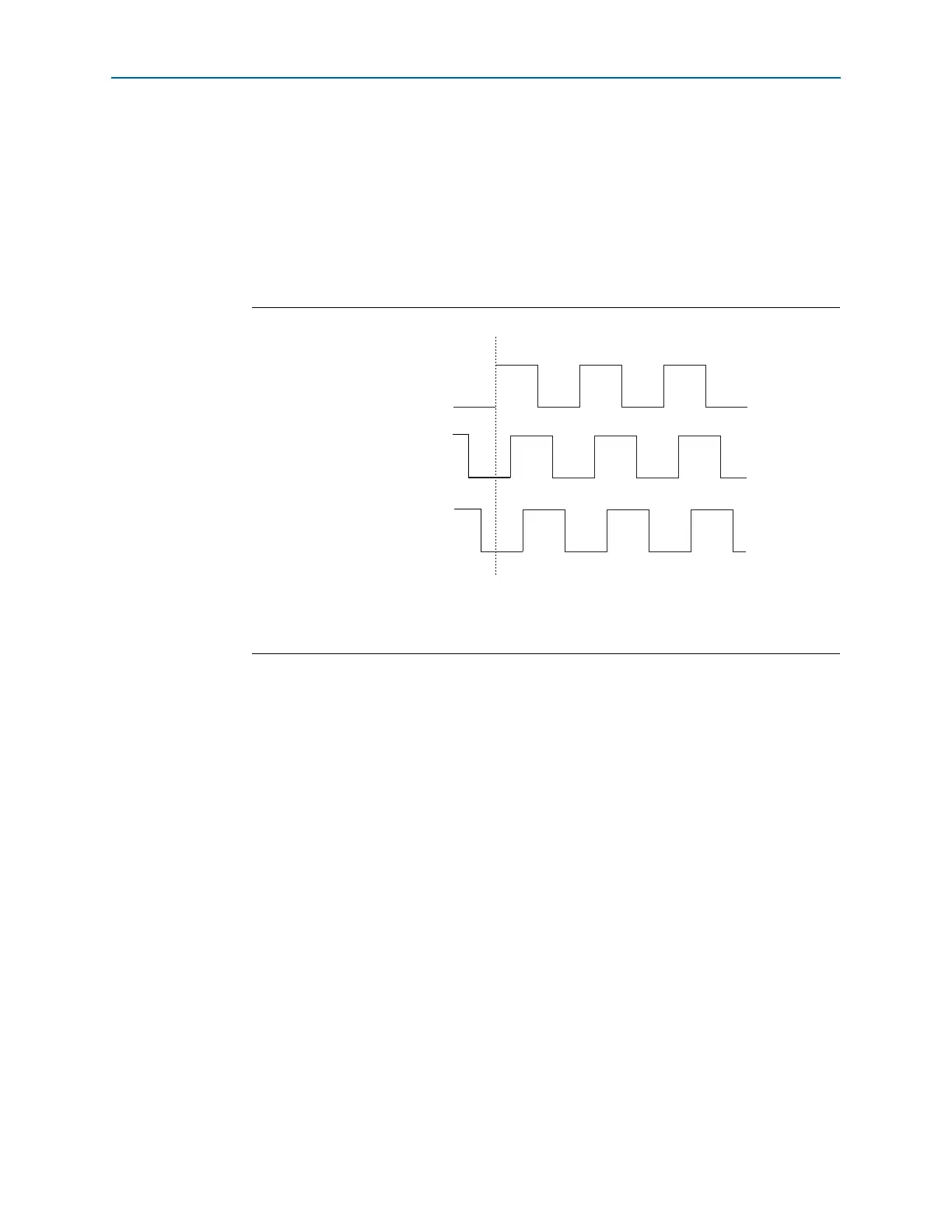

Figure 5–13 shows a waveform example of the phase relationship of the PLL clock in

this mode.

Normal Mode

An internal clock in normal mode is phase-aligned to the input clock pin. The external

clock output pin has a phase delay relative to the clock input pin if connected in this

mode. The Quartus II software timing analyzer reports any phase difference between

the two. In normal mode, the PLL fully compensates the delay introduced by the

GCLK network.

Figure 5–13. Phase Relationship Between PLL Clocks in No Compensation Mode

Notes to Figure 5–13:

(1) Internal clocks fed by the PLL are phase-aligned to each other.

(2) The PLL clock outputs can lead or lag the PLL input clocks.

PLL Reference

Clock at the Input Pin

PLL Clock at the

Register Clock Port

(1), (2)

External PLL Clock

Outputs

(2)

Phase Aligned

Loading...

Loading...