Chapter 6: I/O Features in Cyclone IV Devices 6–31

High-Speed I/O Standards Support

March 2016 Altera Corporation Cyclone IV Device Handbook,

Volume 1

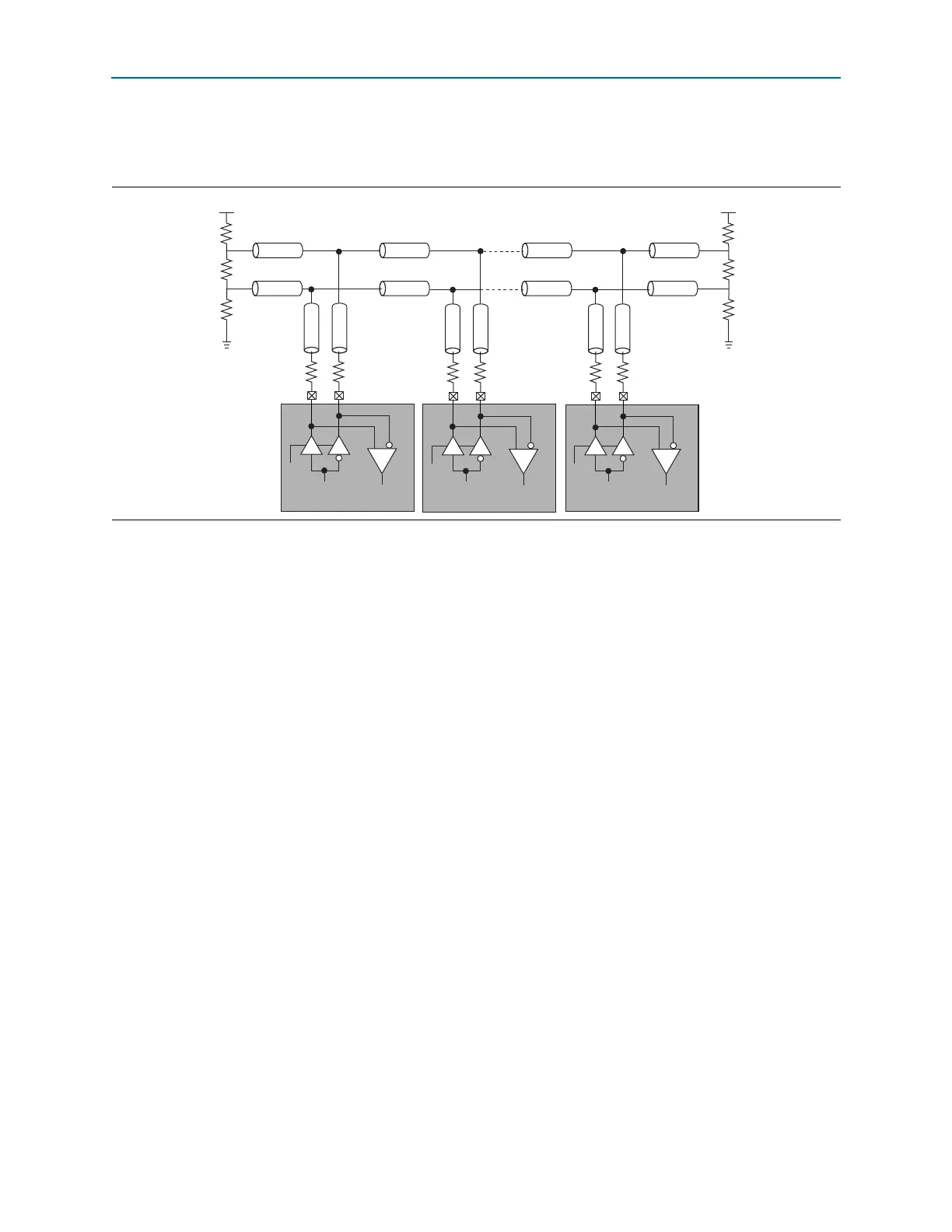

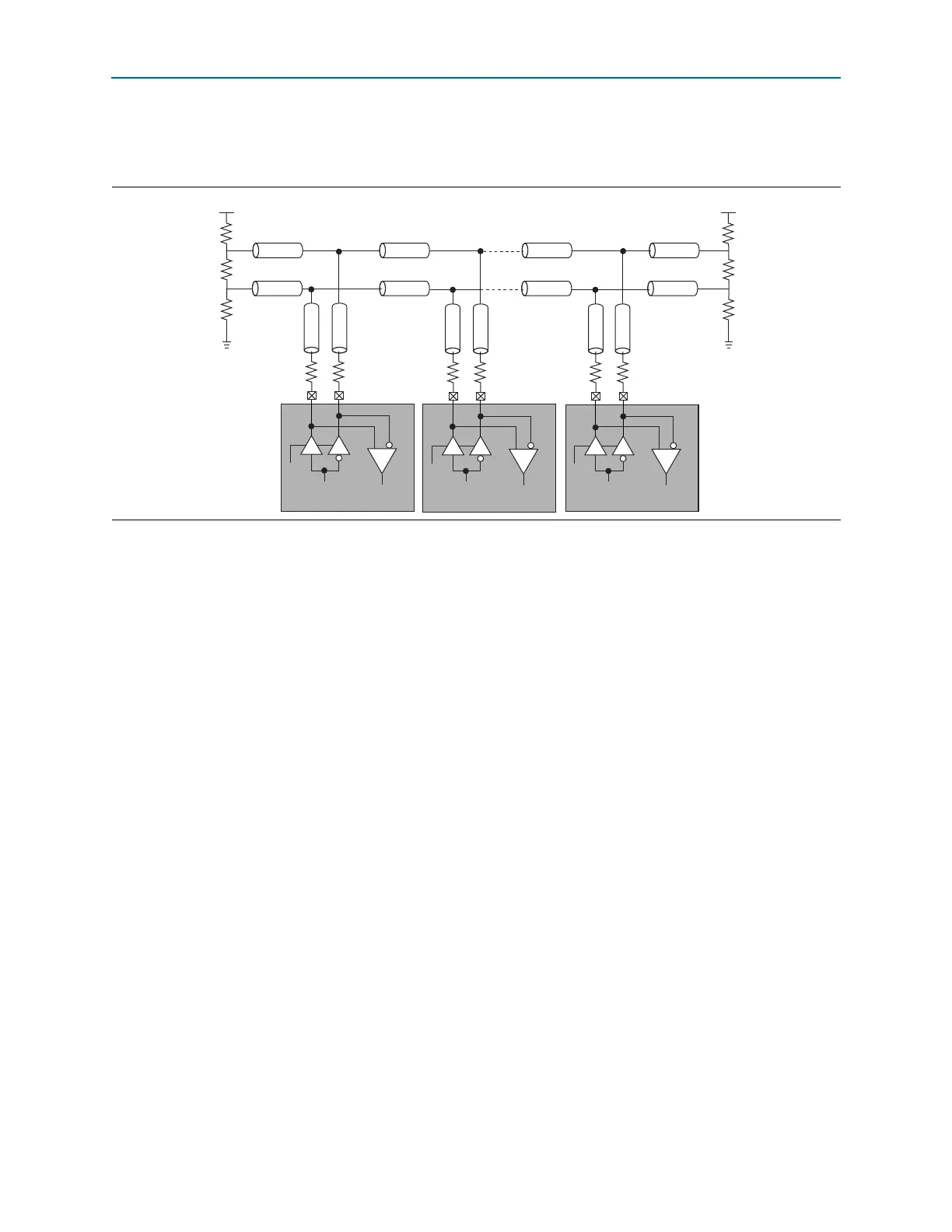

Figure 6–14 shows a typical BLVDS topology with multiple transmitter and receiver

pairs.

The BLVDS I/O standard is supported on the top, bottom, and right I/O banks of

Cyclone IV devices. The BLVDS transmitter uses two single-ended output buffers

with the second output buffer programmed as inverted, while the BLVDS receiver

uses a true LVDS input buffer. The transmitter and receiver share the same pins. An

output-enabled (

OE

) signal is required to tristate the output buffers when the LVDS

input buffer receives a signal.

f For more information, refer to the Cyclone IV Device Datasheet chapter.

Designing with BLVDS

The BLVDS bidirectional communication requires termination at both ends of the bus

in BLVDS. The termination resistor (R

T

) must match the bus differential impedance,

which in turn depends on the loading on the bus. Increasing the load decreases the

bus differential impedance. With termination at both ends of the bus, termination is

not required between the two signals at the input buffer. A single series resistor (R

S

) is

required at the output buffer to match the output buffer impedance to the

transmission line impedance. However, this series resistor affects the voltage swing at

the input buffer. The maximum data rate achievable depends on many factors.

1 Altera recommends that you perform simulation using the IBIS model while

considering factors such as bus loading, termination values, and output and input

buffer location on the bus to ensure that the required performance is achieved.

f For more information about BLVDS interface support in Altera devices, refer to

AN 522: Implementing Bus LVDS Interface in Supported Altera Device Families.

Figure 6–14. BLVDS Topology with Cyclone IV Devices Transmitters and Receivers

V

CC

R

T

50 Ω

100 kΩ

100 kΩ

GND

Output

Data

Input

Data

Cyclone IV Device Family

OE

R

S

R

S

Output

Data

Input

Data

Cyclone IV Device Family

OE

R

S

R

S

Output

Data

Input

Data

Cyclone IV Device Family

OE

R

S

R

S

V

CC

R

T

100 k

Ω

100 kΩ

GND

50

Ω

50 Ω

50 Ω

50 Ω

50 Ω

50 Ω

50 Ω

50 Ω

50 Ω

50 Ω

50 Ω

50 Ω

50 Ω

Loading...

Loading...