Chapter 1: Cyclone IV Transceivers Architecture 1–55

Transceiver Functional Modes

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

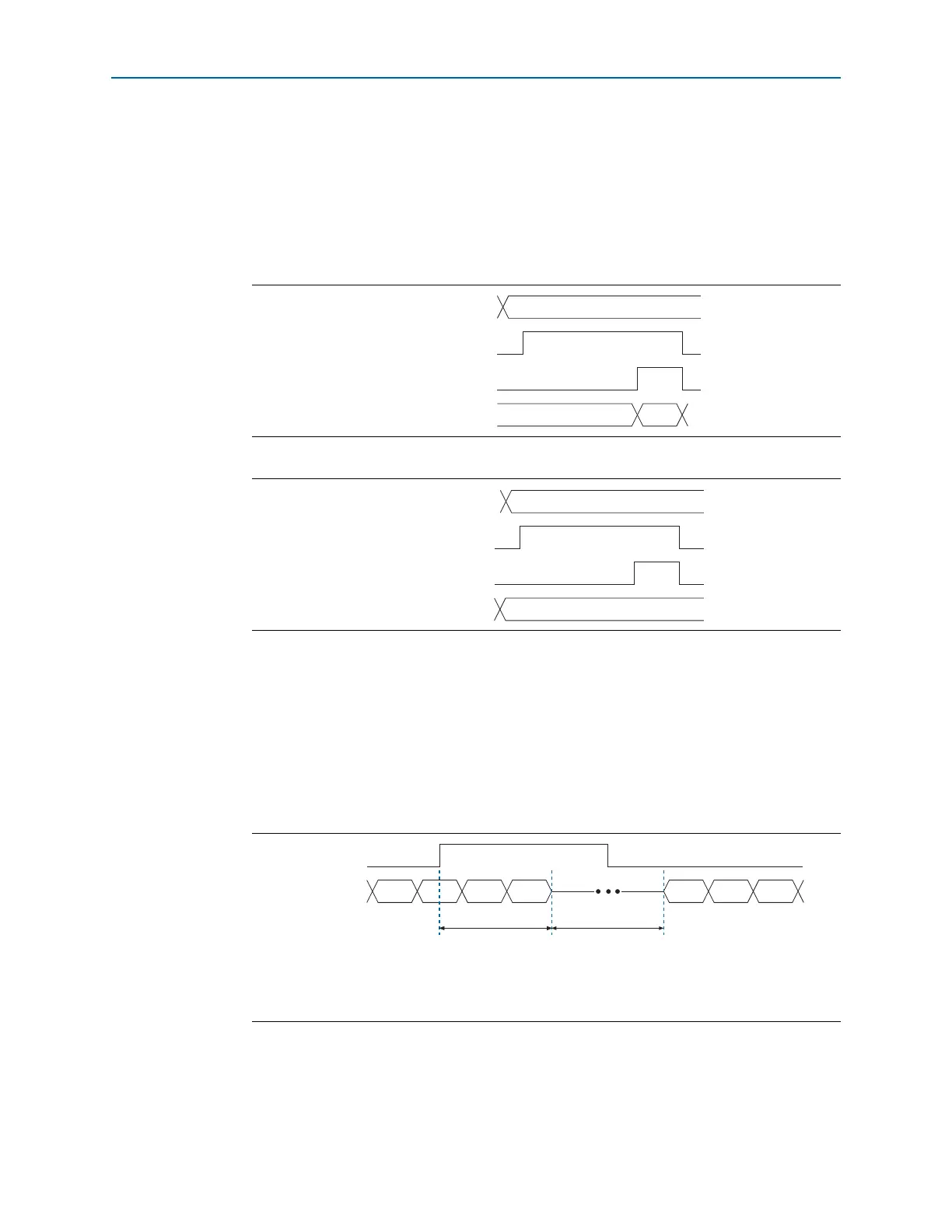

Figure 1–50 and Figure 1–51 show the detection mechanism example for a successful

and unsuccessful receiver detection scenarios respectively. The

tx_forceelecidle

port must be asserted at least 10 parallel clock cycles prior to assertion of

tx_detectrxloop

port to ensure the transmitter buffer is properly tri-stated. Detection

completion is indicated by

pipephydonestatus

assertion, with detection successful

indicated by 3'b011 on

pipestatus[2..0]

port, or detection unsuccessful by 3'b000 on

pipestatus[2..0]

port.

Electrical Idle Control

The Cyclone IV GX transceivers support transmitter buffer in electrical idle state

using the

tx_forceelecidle

port. During electrical idle, the transmitter buffer

differential and common mode output voltage levels are compliant to the PCIe Base

Specification 2.0 for Gen1 signaling rate.

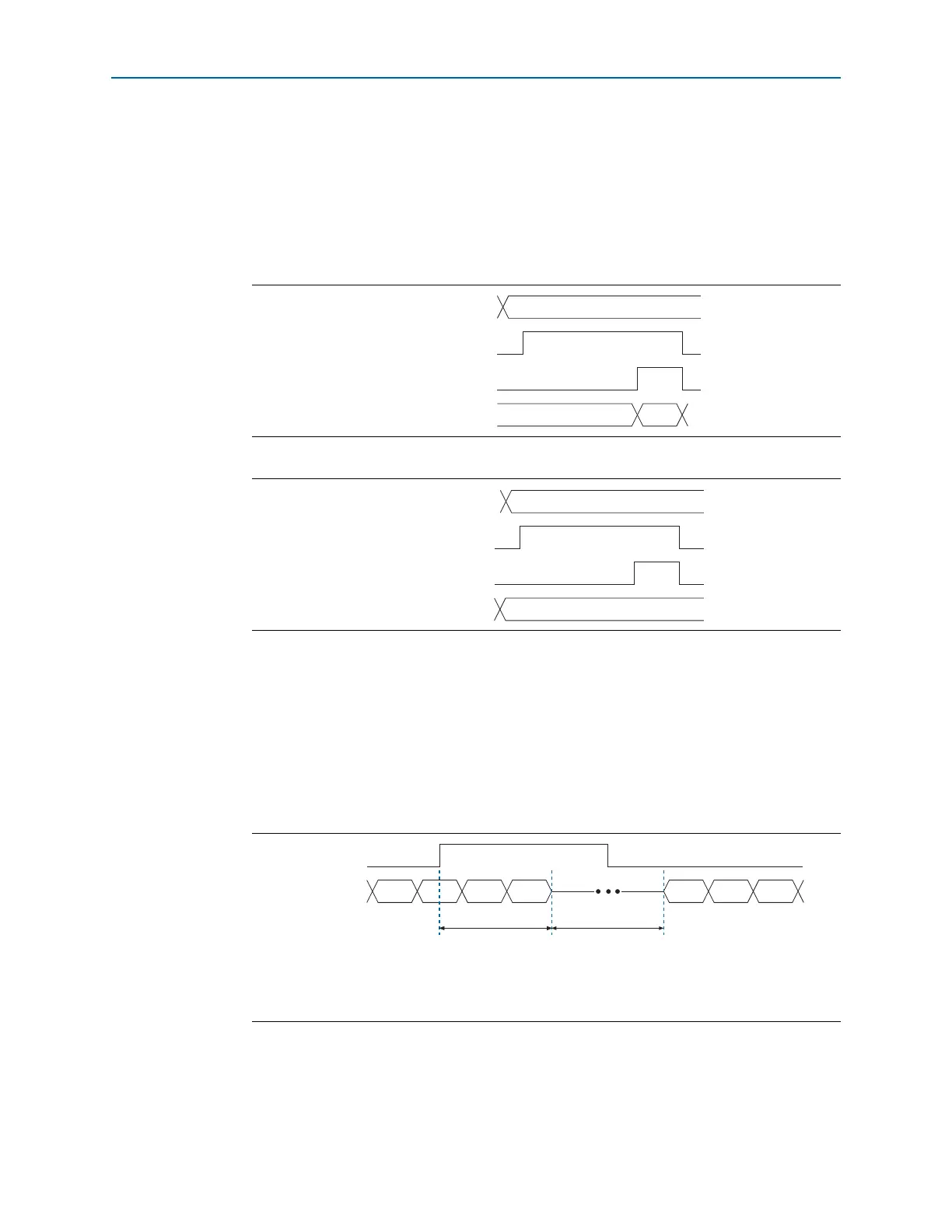

Figure 1–52 shows the relationship between assertion of the

tx_forceelecidle

port

and the transmitter buffer output on the

tx_dataout

port.

Figure 1–50. Example of Successful Receiver Detect Operation

Figure 1–51. Example of Unsuccessful Receiver Detect Operation

Figure 1–52. Transmitter Buffer Electrical Idle State

Notes to Figure 1–52:

(1) The protocol requires the transmitter buffer to transition to a valid electrical idle after sending an electrical idle

ordered set within 8 ns.

(2) The protocol requires transmitter buffer to stay in electrical idle for a minimum of 20 ns for Gen1 signaling rate.

pipephydonestatus

pipestatus[2..0]

3'b0113'b000

powerdown[1..0]

tx_detectrxloopback

2'b10(P1)

pipephydonestatus

pipestatus[2..0]

3'b000

powerdown[1..0]

tx_detectrxloopback

2'b10(P1)

tx_forcelecidle

tx_dataout

<8 ns (1)

>20 ns (2)

Loading...

Loading...