3–8 Chapter 3: Memory Blocks in Cyclone IV Devices

Memory Modes

Cyclone IV Device Handbook, November 2011 Altera Corporation

Volume 1

1 Violating the setup or hold time on the M9K memory block input registers may

corrupt memory contents. This applies to both read and write operations.

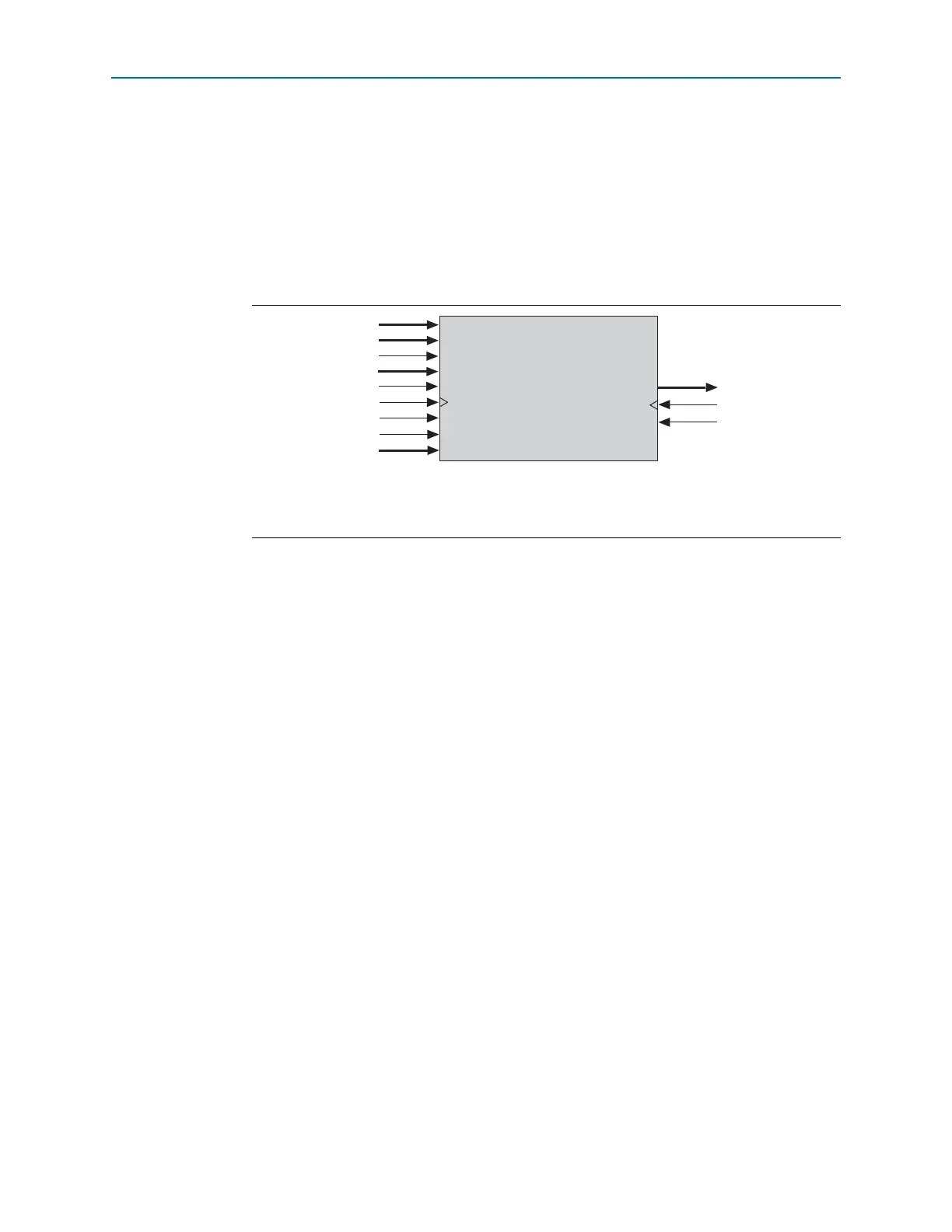

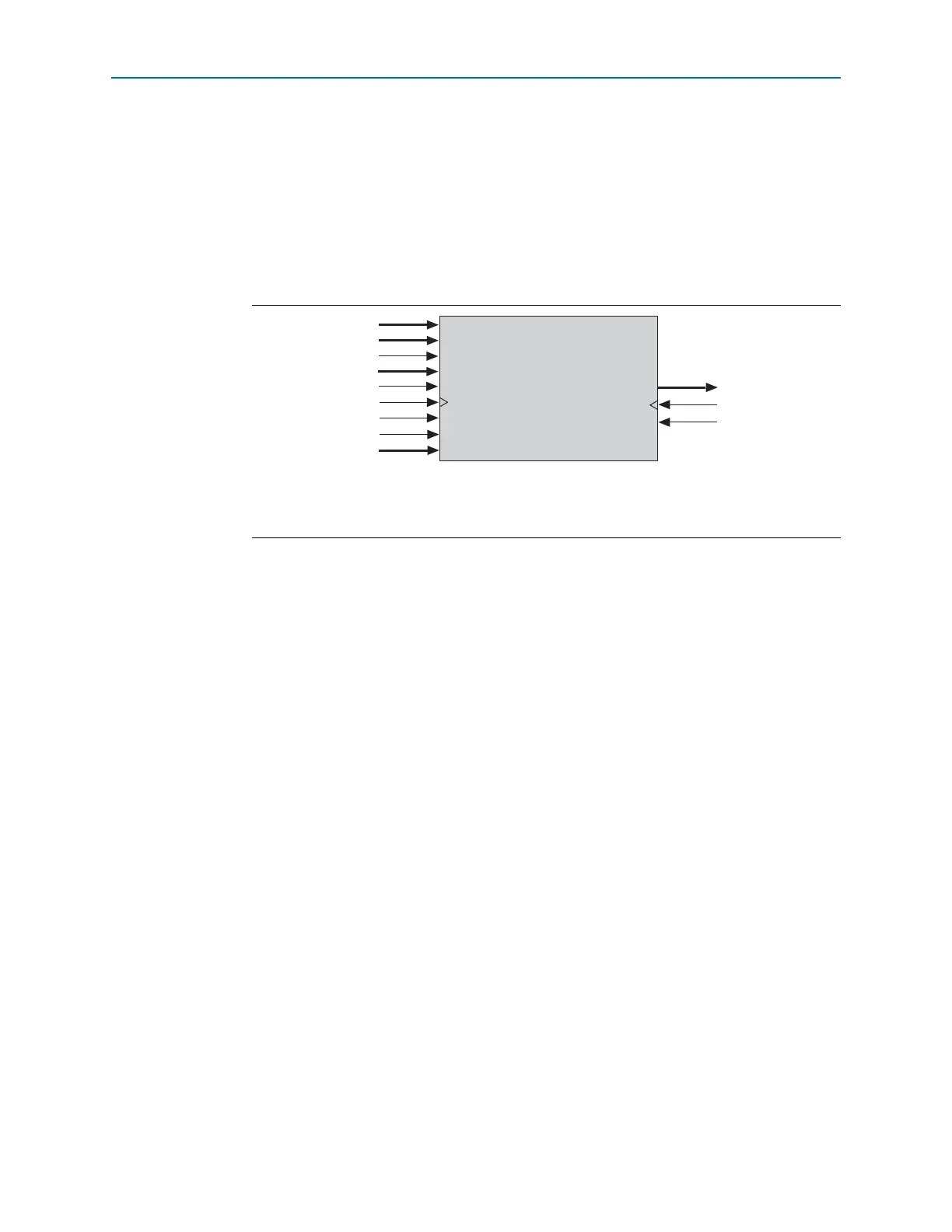

Single-Port Mode

Single-port mode supports non-simultaneous read and write operations from a single

address. Figure 3–6 shows the single-port memory configuration for Cyclone IV

devices M9K memory blocks.

During a write operation, the behavior of the RAM outputs is configurable. If you

activate

rden

during a write operation, the RAM outputs show either the new data

being written or the old data at that address. If you perform a write operation with

rden

deactivated, the RAM outputs retain the values they held during the most recent

active

rden

signal.

To choose the desired behavior, set the Read-During-Write option to either New Data

or Old Data in the RAM MegaWizard Plug-In Manager in the Quartus II software. For

more information about read-during-write mode, refer to “Read-During-Write

Operations” on page 3–15.

The port width configurations for M9K blocks in single-port mode are as follow:

■ 8192 × 1

■ 4096 × 2

■ 2048 × 4

■ 1024 × 8

■ 1024 × 9

■ 512 × 16

■ 512 × 18

■ 256 × 32

■ 256 × 36

Figure 3–6. Single-Port Memory

(1)

,

(2)

Notes to Figure 3–6:

(1) You can implement two single-port memory blocks in a single M9K block.

(2) For more information, refer to “Packed Mode Support” on page 3–4.

data[ ]

address[ ]

wren

byteena[]

addressstall

inclock

inclocken

rden

aclr

outclock

q[]

outclocken

Loading...

Loading...