Chapter 1: Cyclone IV Transceivers Architecture 1–45

Calibration Block

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

When using user-specified clock option, ensure that the clock feeding

rx_coreclk

port

has 0 ppm difference with the RX phase compensation FIFO write clock.

Calibration Block

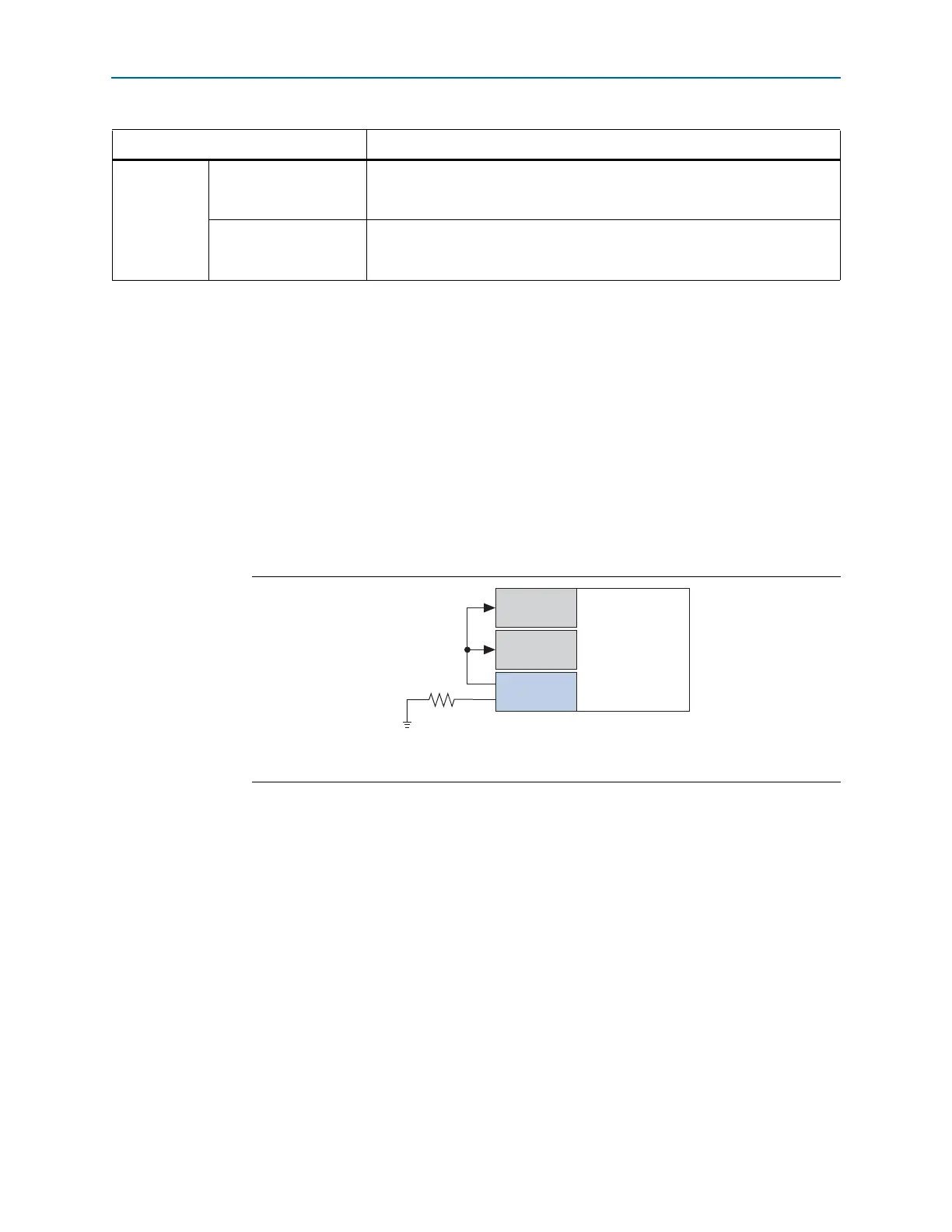

This block calibrates the OCT resistors and the analog portions of the transceiver

blocks to ensure that the functionality is independent of process, voltage, and

temperature (PVT) variations.

Figure 1–40 shows the location of the calibration block and how it is connected to the

transceiver blocks.

Bonded

With rate match FIFO

(1)

coreclkout

clock feeds the FIFO read clock for the bonded channels.

coreclkout

clock is the common bonded low-speed clock, which also feeds

the FIFO read clock and transmitter PCS in the bonded channels.

Without rate match FIFO

rx_clkout

clock feeds the FIFO read clock.

rx_clkout

is forwarded through

the receiver channel from low-speed recovered clock, which also feeds the FIFO

write clock.

Note to Table 1–13:

(1) Configuration with rate match FIFO is supported in transmitter and receiver operation.

Table 1–13. Automatic RX Phase Compensation FIFO Read Clock Selection (Part 2 of 2)

Channel Configuration Quartus II Selection

Figure 1–40. Transceiver Calibration Blocks Location and Connection

Note to Figure 1–40:

(1) Transceiver block GXBL1 is only available for devices in F484 and larger packages.

GXBL1 (1)

GXBL0

2KΩ

RREF

Calibration

Block

Cyclone IV GX

Device

Loading...

Loading...