1–44 Chapter 1: Cyclone IV Transceivers Architecture

Transceiver Clocking Architecture

Cyclone IV Device Handbook, February 2015 Altera Corporation

Volume 2

In the transmitter datapath, TX phase compensation FIFO forms the FPGA

fabric-transmitter interface. Data and control signals for the transmitter are clocked

with the FIFO write clock. The FIFO write clock supports automatic clock selection by

the Quartus II software (depending on channel configuration), or user-specified clock

from

tx_coreclk

port. Table 1–12 details the automatic TX phase compensation FIFO

write clock selection by the Quartus II software.

1 The Quartus II software assumes automatic clock selection for TX phase

compensation FIFO write clock if you do not enable the

tx_coreclk

port.

When using user-specified clock option, ensure that the clock feeding

tx_coreclk

port

has 0 ppm difference with the TX phase compensation FIFO read clock.

In the receiver datapath, RX phase compensation FIFO forms the receiver-FPGA

fabric interface. Data and status signals from the receiver are clocked with the FIFO

read clock. The FIFO read clock supports automatic clock selection by the Quartus II

software (depending on channel configuration), or user-specified clock from

rx_coreclk

port. Table 1–13 details the automatic RX phase compensation FIFO read

clock selection by the Quartus II software.

1 The Quartus II software assumes automatic clock selection for RX phase

compensation FIFO read clock if you do not enable the

rx_coreclk

port.

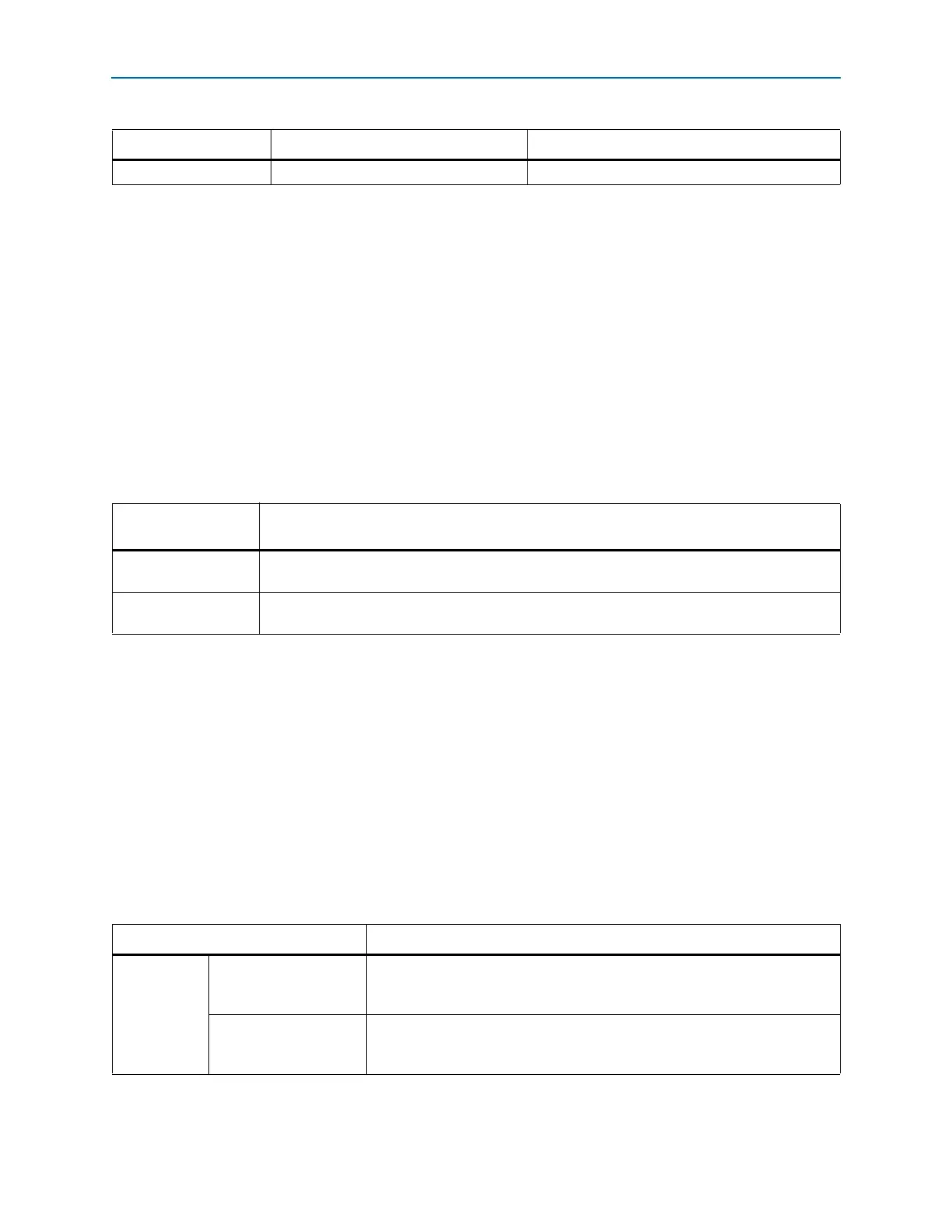

cal_blk_clk

(2)

Transceiver calibration block clock FPGA fabric to transceiver

Notes to Table 1–11:

(1) Offset cancellation process that is executed after power cycle requires

reconfig_clk

clock. The

reconfig_clk

must be driven with a

free-running clock and not derived from the transceiver blocks.

(2) For the supported clock frequency range, refer to the Cyclone IV Device Data Sheet.

Table 1–11. FPGA Fabric-Transceiver Interface Clocks (Part 2 of 2)

Clock Name Clock Description Interface Direction

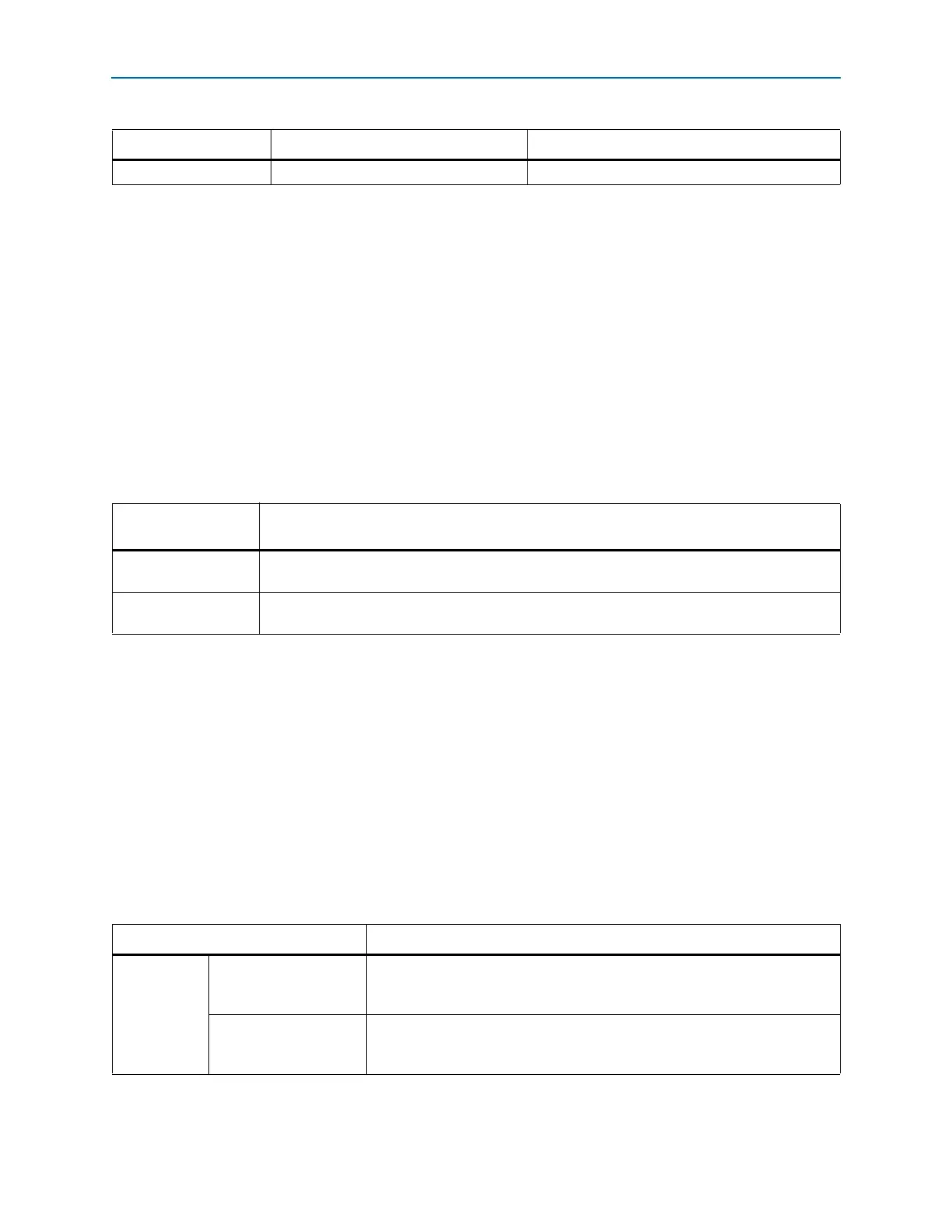

Table 1–12. Automatic TX Phase Compensation FIFO Write Clock Selection

Channel

Configuration

Quartus II Selection

Non-bonded

tx_clkout

clock feeds the FIFO write clock.

tx_clkout

is forwarded through the transmitter

channel from low-speed clock, which also feeds the FIFO read clock.

Bonded

coreclkout

clock feeds the FIFO write clock for the bonded channels.

coreclkout

clock is the

common bonded low-speed clock, which also feeds the FIFO read clock in the bonded channels.

Table 1–13. Automatic RX Phase Compensation FIFO Read Clock Selection (Part 1 of 2)

Channel Configuration Quartus II Selection

Non-bonded

With rate match FIFO

(1)

tx_clkout

clock feeds the FIFO read clock.

tx_clkout

is forwarded through

the receiver channel from low-speed clock, which also feeds the FIFO write

clock and transmitter PCS.

Without rate match FIFO

rx_clkout

clock feeds the FIFO read clock.

rx_clkout

is forwarded through

the receiver channel from low-speed recovered clock, which also feeds the FIFO

write clock.

Loading...

Loading...