Chapter 10: JTAG Boundary-Scan Testing for Cyclone IV Devices 10–3

BST Operation Control

December 2013 Altera Corporation Cyclone IV Device Handbook,

Volume 1

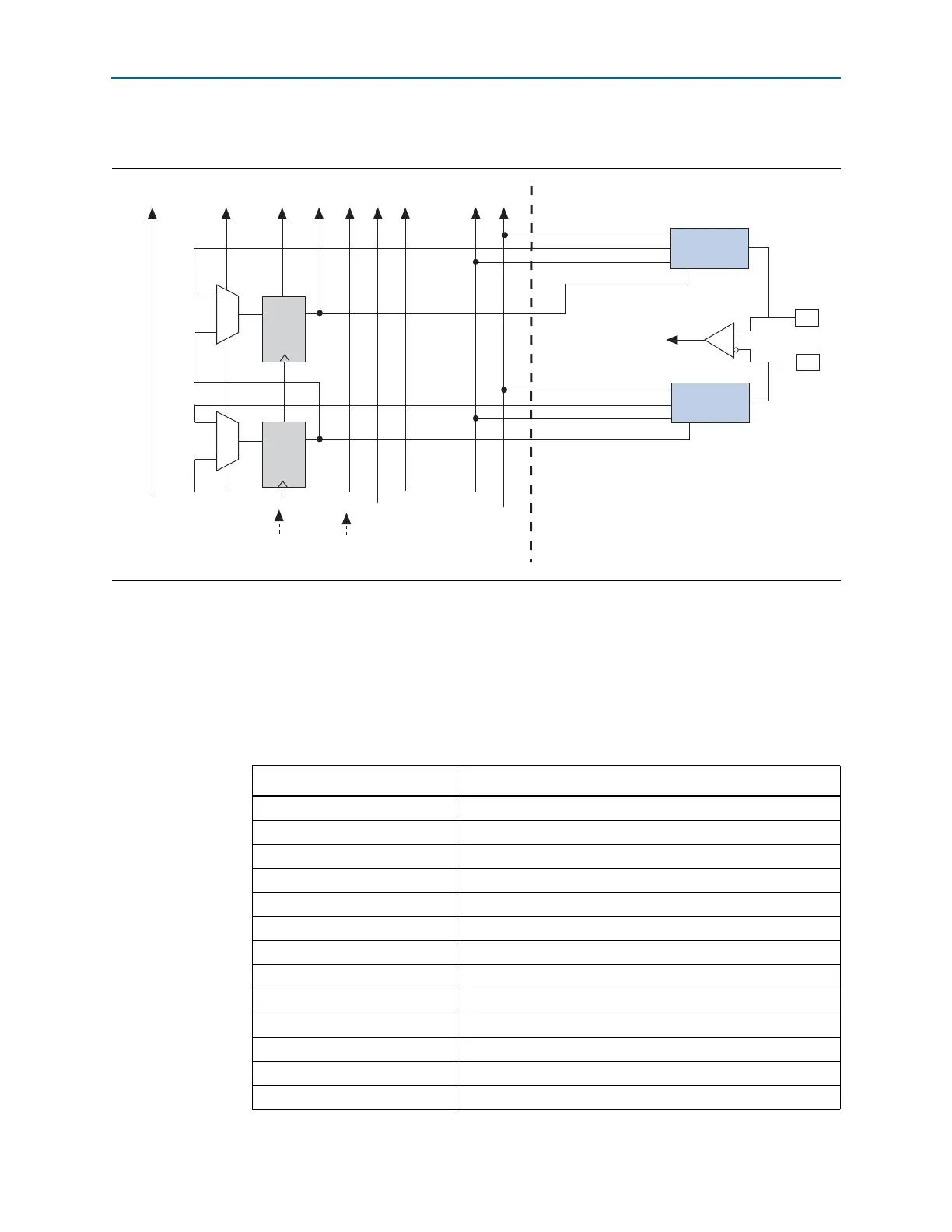

Figure 10–2 shows the Cyclone IV GX HSSI receiver BSC.

f For more information about Cyclone IV devices user I/O boundary-scan cells, refer to

the IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone III Devices chapter.

BST Operation Control

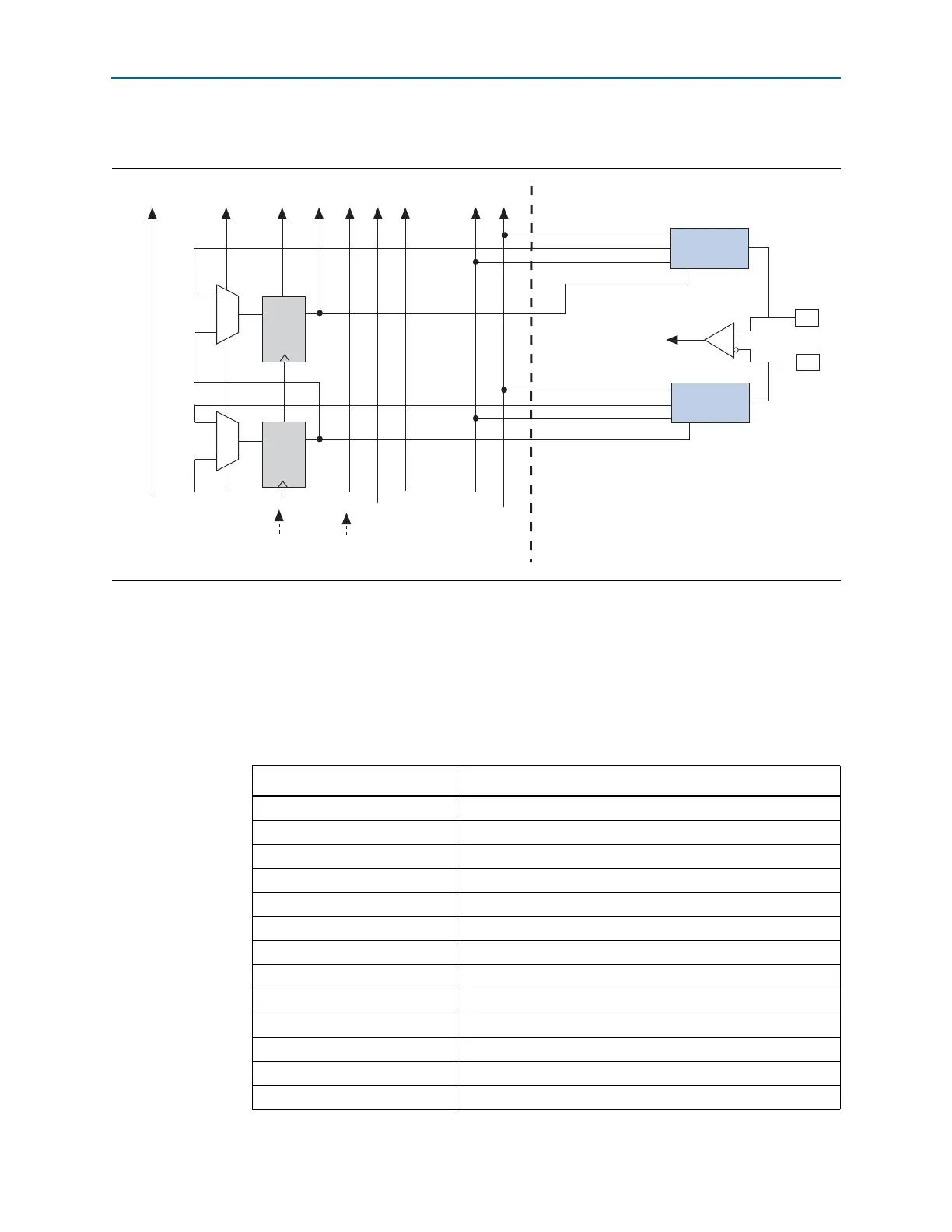

Tab le 1 0– 1 lists the boundary-scan register length for Cyclone IV devices.

Figure 10–2. HSSI Receiver BSC with IEEE Std. 1149.6 BST Circuitry for the Cyclone IV GX Devices

HIGHZ

SDIN

SHIFT

0

1

0

1

DQ

DQ

CLK

SDOUT

UPDATE

MODE

AC_TEST

Capture Update

Registers

BSRX1

BSOUT1

BSRX0

BSOUT0

MEM_INIT

AC_MODE

Hysteretic

Memory

AC JTAG Test

Receiver

Mission

(DATAIN)

Optional INTEST/RUNBIST

not supported

Pad

Pad

Rx Input

Buffer

AC JTAG Test

Receiver

Hysteretic

Memory

BSCAN PMA

Table 10–1. Boundary-Scan Register Length for Cyclone IV Devices (Part 1 of 2)

Device Boundary-Scan Register Length

EP4CE6 603

EP4CE10 603

EP4CE15 1080

EP4CE22 732

EP4CE30 1632

EP4CE40 1632

EP4CE55 1164

EP4CE75 1314

EP4CE115 1620

EP4CGX15 260

EP4CGX22 494

EP4CGX30

(1)

494

EP4CGX50 1006

Loading...

Loading...