Chapter 3: Cyclone IV Dynamic Reconfiguration 3–27

Dynamic Reconfiguration Modes

November 2011 Altera Corporation Cyclone IV Device Handbook,

Volume 2

Control and Status Signals for Channel Reconfiguration

The various control and status signals involved in the Channel Reconfiguration mode

are as follows. Refer to “Dynamic Reconfiguration Controller Port List” on page 3–4

for the descriptions of the control and status signals.

The following are the input control signals:

■

logical_channel_address[n..0]

■

reset_reconfig_address

■

reconfig_reset

■

reconfig_mode_sel[2..0]

■

write_all

The following are output status signals:

■

reconfig_address_en

■

reconfig_address_out[5..0]

■

channel_reconfig_done

■

busy

The ALTGX_RECONFIG connection to the ALTGX instances when set in channel

reconfiguration mode are as follows. For the port information, refer to “Dynamic

Reconfiguration Controller Port List” on page 3–4.

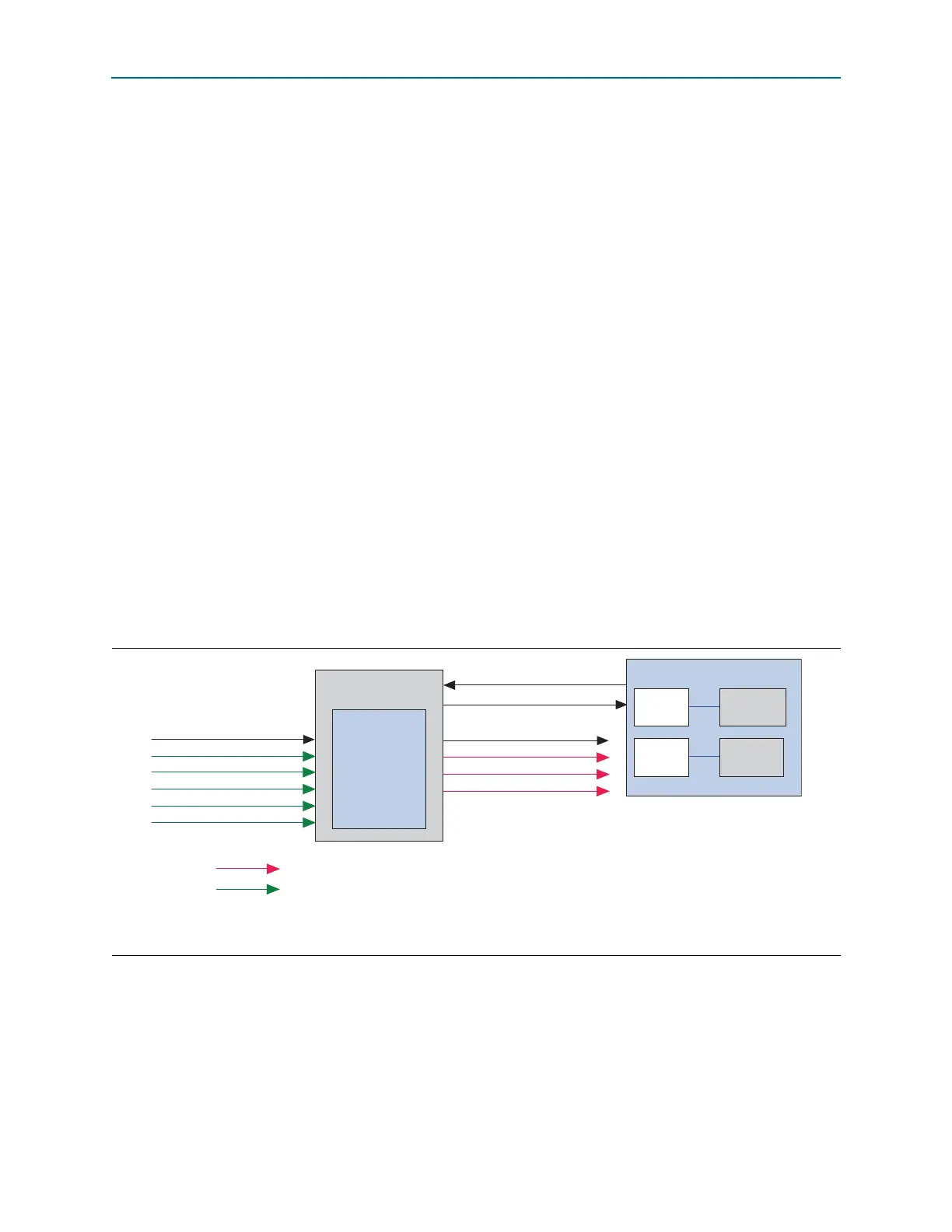

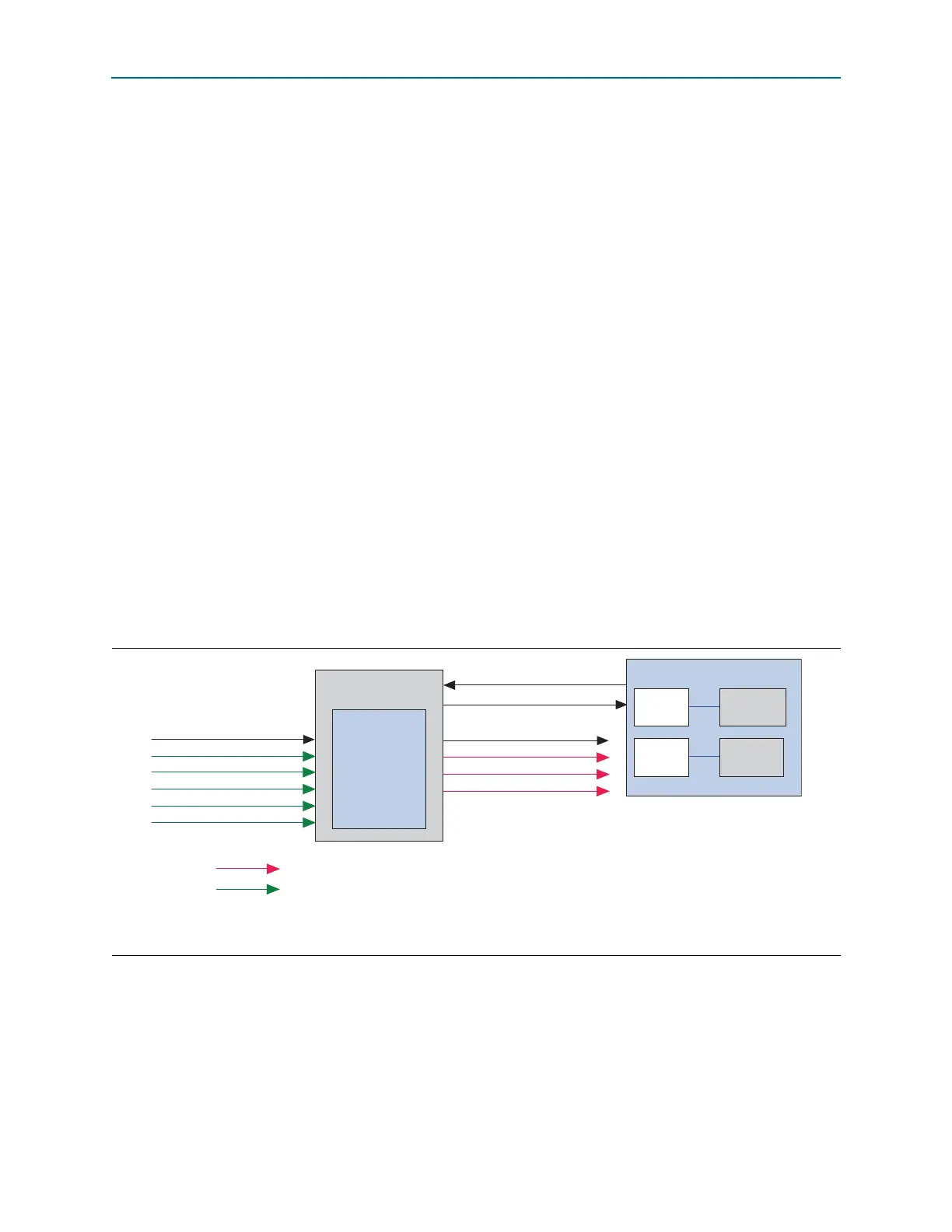

Figure 3–10 shows the connection for channel reconfiguration mode.

Figure 3–10. ALTGX and ALTGX_RECONFIG Connection for Channel Reconfiguration Mode

Note to Figure 3–10:

(1) This block can be reconfigured in channel reconfiguration mode.

ALTGX_RECONFIG

Channel

Reconfig

Control

Logic

reconfig_clk

reconfig_reset

write_all

reconfig_data[15..0]

busy

channel_reconfig_done

reconfig_address_out[5..0]

reconfig_address_en

reset_reconfig_address

logical_channel_address[n..0]

Output status signals from the ALTGX_RECONFIG controller

Input control signals to the ALTGX_RECONFIG controller

ALTGX

reconfig_fromgxb[n..0]

TX PCS

(1)

TX PMA

reconfig_togxb[3..0]

RX PCS

(1)

RX PMA

+

CDR (1)

Loading...

Loading...